Изобретение относится к вычисли- тельной технике, в частности к технологии изготовления полупроводниковых интегральных №1кросхем, и может быть; использовано для изготовления матричного накопителя электрически пере- програм шруемого постоянного запоминающего устройства.

Целью изобретения является повышение быстродействия матричного накопителя.

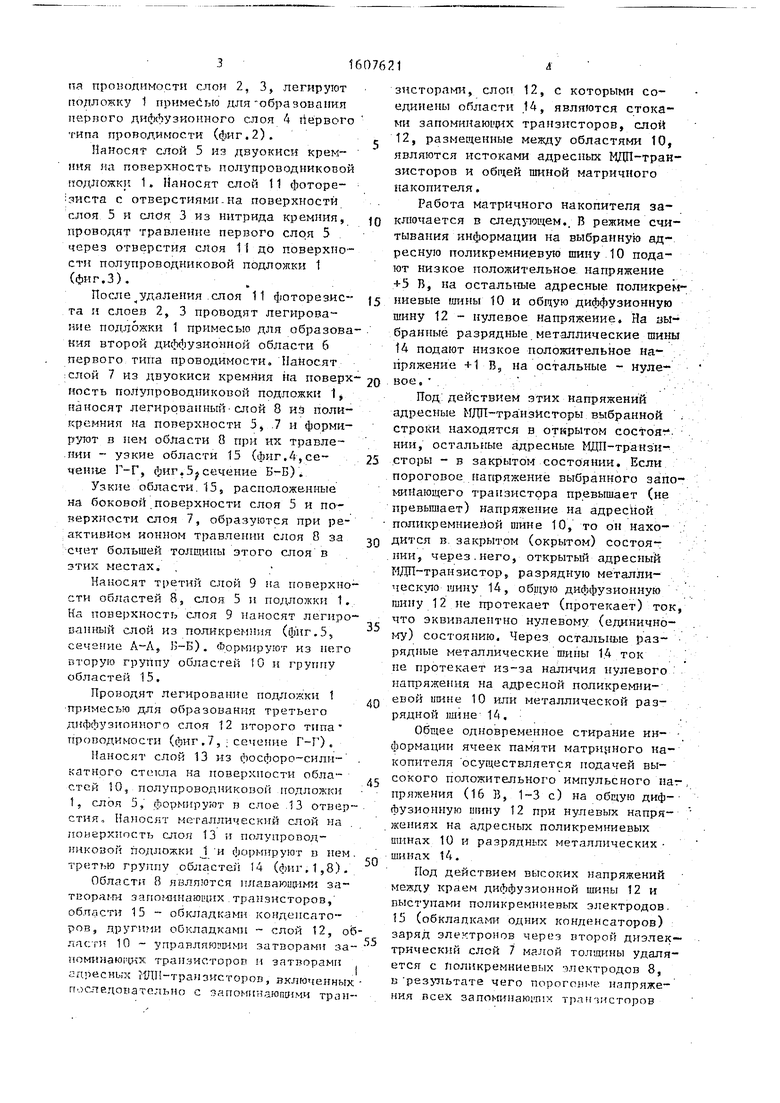

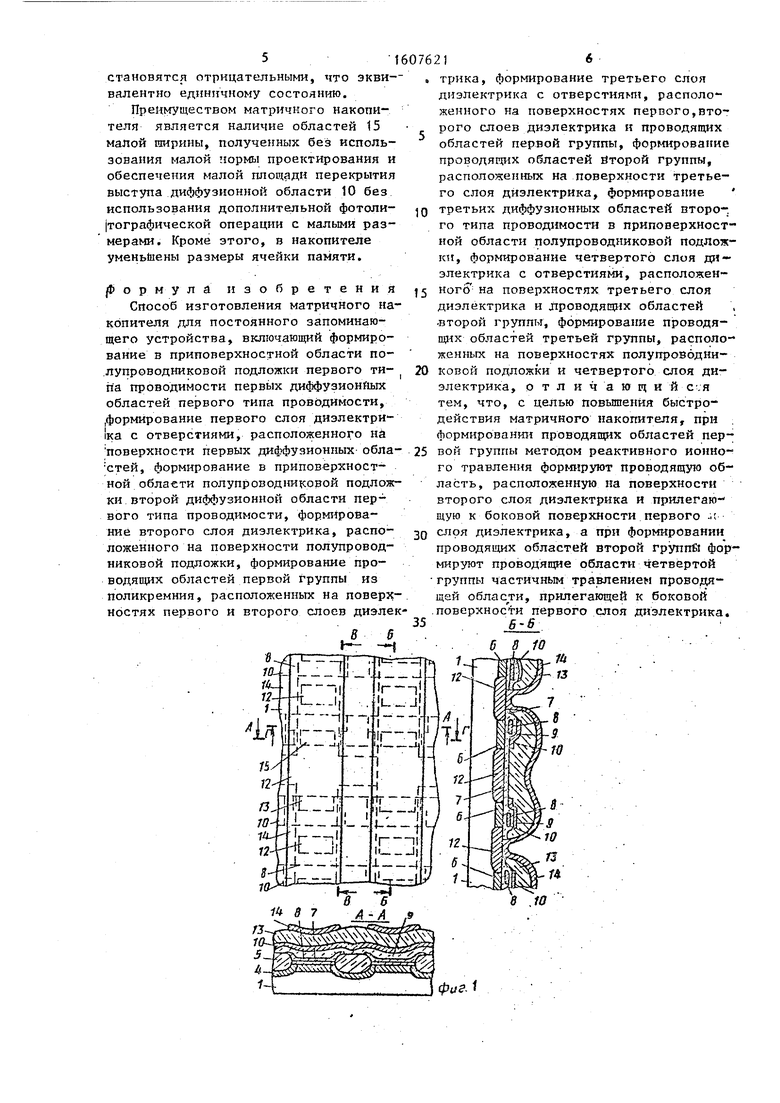

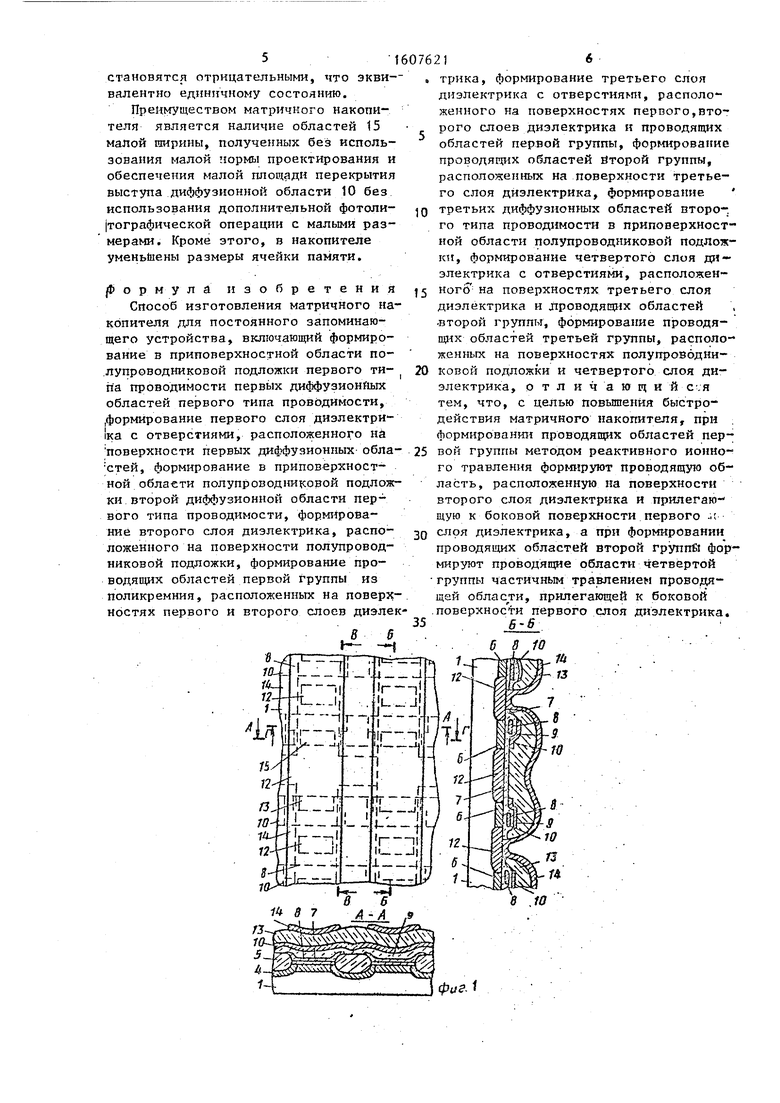

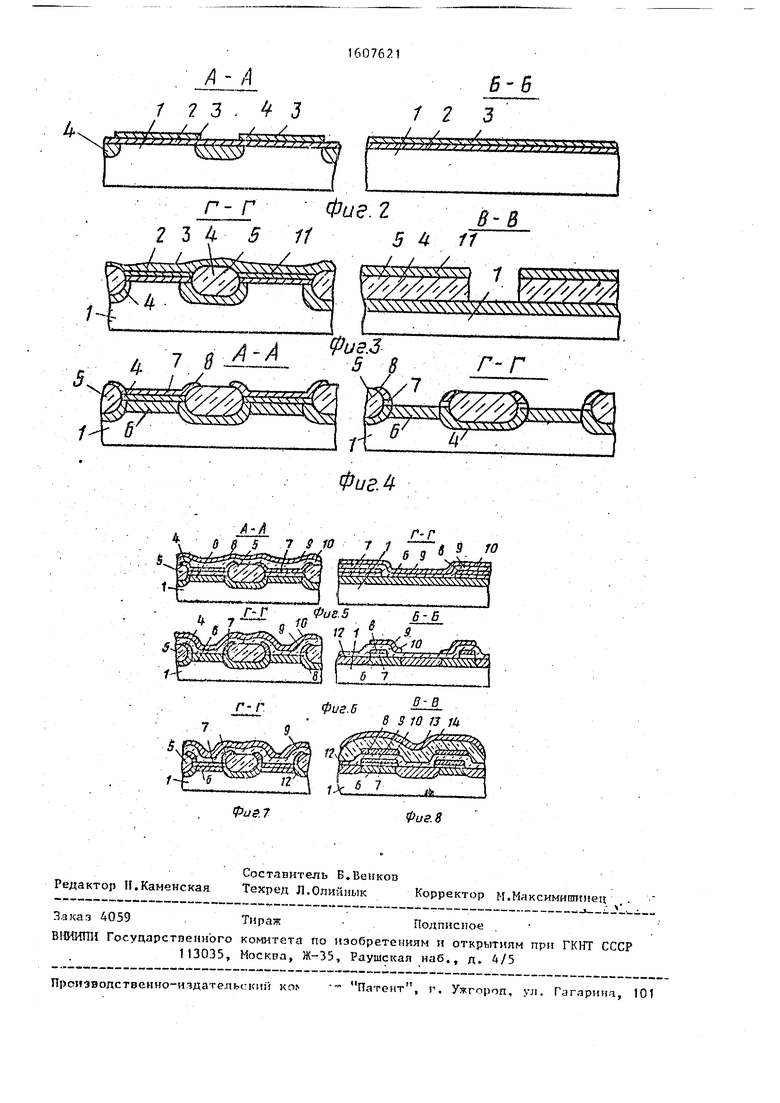

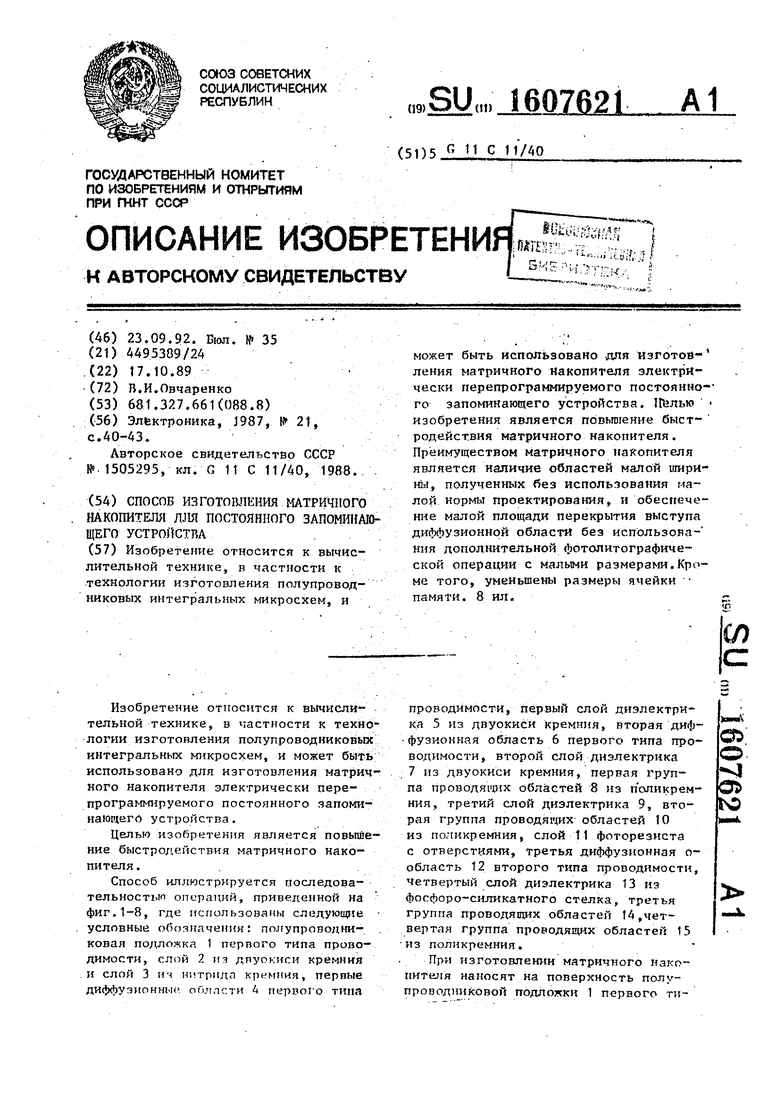

Способ иллюстрируется последовательностью опираиий, приведенной на фиг.1-8, где использованы следующие условные обозначения: по;гупроводни- . ковал подложка 1 первого типа проводимости, сл(1й 2 из двуокиси кремния и слой 3 нч нитридп кремния, первые диффузионные обллсти А первого типа

проводимости, первый слой диэлектрика 5 из двуокиси кремния, вторая диффузионная область 6 первого типа проводимости, второй слой диэлектрика

7 из двуокиси кремния, первая группа проводя1 р1Х областей 8 из п оликрем- ния, третий слой диэлектрика 9, вторая группа проводягдих областей 10 из поликремния, слой 11 фоторезиста с отверстиями, третья диффузионная о- область 12 второго типа проводимости, четвертый слой диэлектрика 13 из фосфоро-силикатного стелка, третья группа проводятзнх областей 14,чет- вер тая группа проводящих областей 15

из поликремния.

При изготовлении матричного накопителя наносят на поверхность полупроводниковой подложки 1 первого

О

еп

па проводимости слои 2, 3, легируют подложку 1 примеСыо для образования первого диффузионного слоя 4 Первого типа проводимости (фиг.2).

HaHocfit слой 5 из двуокиси крем- иия на поверхность полупроводниковой гтодложк 1. Наносят слой 11 фоторе- зиста с отверстиями-На поверхности слоя 5 и 3 из нитрида кремния, проводят травление первого слоя 5 через отверстия слоя 11 до поверхности полупроводниковой подложки 1 (фиг.З),

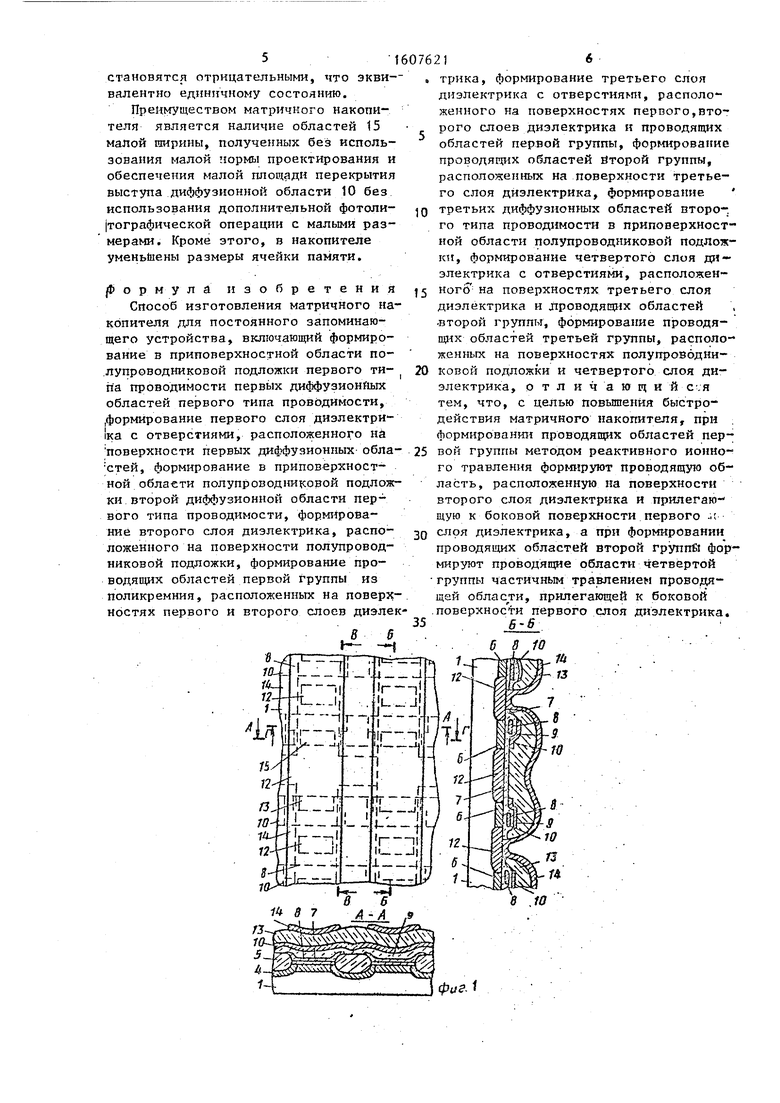

После ддалепия .слоя 11 фоторезиста и слоев 2, 3 проводят легирование подложки 1 примесью для образования второй дшМ Узнонной области б первого типа проводимости. Наносят :слой 7 из двуокиси кремршя на поверхность полупроводниковой подложки 1j наносят легированный-слой 8 из поли- г-;ремния на поверхности 5, .7 и формируют в нем области 8 при их травле- ,нии - узкие области 15 (фиг.4,сечение , фиг.5 сечение Б-Б)

Узкие области.15, расположенные на боковой.поверхности слоя 5 и поверхности слоя 7, образуются при ре- ;активном ионном травлении слоя 8 за счет большей толщины этого слоя в зтик местах, ,

Наносят третий слой 9 на поверхности областей 8, слоя 5 и подложки 1. На поверхность с.лоя 9 наносят легиро оангшй слой из поликремиия (фпг.5, сечеиие А-А, Б-Б), Формируют из него вторую группу областей 10 и группу областей 15,

Проводят легирование подложки 1 примесью для образования третьего диффузионного слоя 12 второго типа проводимости (фиг .7, :сечение Г-Г).

Наносят слой 13 из фосфоро-сили- каткого CTLMuia на поверхности областей 10, полупроводниковой подложки 1, слоя 5, формируют в слое .13 отверстия. Наносят металлический слой на понерхность слоя 13 и полупроводниковой подложки J И формируют в нем трет7,ю группу областей 14 (фиг. 1,8),

Области 8 являются плаваюио-ши за- Ti opai-M эапог-п1наю1чих .тран.зисторов, области 15 - обкладками конденсаторов, другими обкладками - слой 12, об ЛПСТ15 10 управляюпшми затворами за- поминаюр нх транзисторов и затворами адресных ШП-трамзисторов, включенных последовательно с запомпнаюпшми транзисторами, слои 12, с которыми соединены области .14, являются стоками запоминаю1 их транзисторов, слой

5 12, размещенные между областями 10, являются истоками адресных МДП-тран- зисторов и об|цей шиной матричного накопителя.

Работа матричного накопителя за0 ключается в ,. В режиме считывания информации на выбранную адресную поликремни.евую шину 10 подают низкое положительное напряжение +5 В, на остальные адресные поликреь 5 ниевые шины 10 и общую диффузионную шину 12 - нулевое напряжение. На зы- бранныё. разрядные мет.аллические шины

14подают низкое положительное напряжение +1 В, на остальные - нуле0 вое. :

Под: действием этих напряжений адресные МЛП-транзИсгоры выбранной . строки находятся в открытом состояг . НИИ, остальные адресные МДП-транз и5 сторы - в закрытом состоянии. Если пороговое напряжение выбранного запоминающего транзистора превышает (не превышает) напряжение на адресной поликремниейой шине 10, то он нахо0 дится в. закрытом (окрытом) состоя- .НИИ, через.него, открытый адресный ИДП-транзистор, разрядную металлическую шину 14, общую диффузионную тнну 12 не протекает (протекает) ток,

что эквивалентно нулевому (единично- 1-гу) состоянию. Через остальные раз- рядные металлические шины 14 ток не протекает из-за наличия нулевого . . нащ5яжения на адресной поликремни- .

г) евой ишне 10 или металлической разрядной mine- 14.

Общее одновременное стирание ин- формации ячеек памяти матри.чного накопителя осуществляется подачей вы5 сокого положительного импульсного на-, нряжения (16 В, 1-3 с) на общую диф- фузионную utmiy 12 при нулевых напря- . жениях на адресных поликремниевых шинах 10 и разрядных металлических шинах 14,

Под действием высоких напряжений между краем диффузионной шины 12 и выступами поликремниевьгх электродов.

15(обкладкамт-f одних конденсаторов)

заряд эле.чтронов через второй диэлектрический слой 7 малой толщины удаляется с поликремниевых электродов 8, в-рез -льтате чего пороговые напряже- ПИЯ всех запоминаю1 П1х транчисторов

0

становятся отрицательными, что эквивапентно единичному состоянию.

Преимуществом матричного накопи- теля является наличие областей 15 малой ширины, полученных без использования малой ормы проектирования и обеспечения малой площади перекрытия выступа диффузионной области 10 без использования дополнительной фотоли- |тографической операции с малыми размерами. Кроме этого, в накопителе уменьшены размеры ячейки памяти.

5ормула изобретения Способ изготовления матричного накопителя для постоянного запоминающего устройства, включающий формирование в приповерхностной области по- .лупроводниковой подложки первого тип а проводимости первых диффузионйых областей первого типа проводимости, .формирование первого слоя диэлектри- 1ка с отверстиями, расположенного на поверхности первых диффузионных обла- стей, формирование в приповерхностной области полупроводниковой подложки второй диффузионной области первого типа проводимости, форшфова- ниё второго слоя диэлектрика, расположенного на поверхности полупроводниковой подложки, формирование проводящих областей первой группы из поликремния, расположенных на поверхкостях первого и второго слоев диэлекS

/й4fii121

/5/ 12

П

Wt-M

12

ia

-

, к10

15

20

25

30

35

трика, формирование третьего слоя диэлектрика с отверстиям, расположенного на поверхностях первого,второго слоев диэлектрика и проводящих областей первой группы, формирование проводящих областей второй группы, расположенных на поверхности третьего слоя диэлектрика, формирование третьих диффузионных областей второго типа проводимости в приповерхност ной области полупроводниковой подложки, формирование четвертого слоя диэлектрика с отверстиями, расположен- ногб-на поверхностях третьего слоя диэлектрика и лроводящих областей второй группы, формирование проводящих областей третьей группы, расположенных на поверхностях полупроводниковой подложки и четвертого слоя диэлектрика, отличающи и с-.я тем, что, с целью повышения быстродействия матричного накопителя, при ; формировант проводящих областей первой группы методом реактивного ионного травления формируют проводящую область, расположенную на поверхности второго слоя диэлектрика и прилегаю щую к боковой поверхности первого -. слоя диэлектрика, а при формировании проводящих областей второй группй формируют проводящие области четвертой группы частичным травлением проводящей облас ти, прилегающей к боковой .поверхности первого слоя диэлектрика. 6-5

Ю

фаЗ.

/

ALA

1 3 . 4 J

/V ,4,

.чАЗЗ

5-5

/

,//

k I. M t

fff

Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных микросхем, и может быть использовано для изготов- ления матричного иакопителя электрически перепрограммируемого постоянно- го запоьшнающего устройства. 1Гёлью изобретения является повьтгение быстродействия матричного накопителя. Преимуществом матричного накопителя является наличие областей малой шири- нь1, полученных без использования малой нормы проектирования, и обеспечение малой площади перекрытия выступа диффузионной области без использояа- ния дополнительной фотолитографической операции с малыми размерами.Кроме того, уменьшены размеры ячейки памяти. 8 ил. Г

Z 3 Д 5 //

Фгу. 2

ФигЛ

Х-Л

у L± - 5

U/

S jo zy A tvVy// // //;

г-r

фиг. 5

5 /r

г-г

5-5

б 7

в-в

| Эльктроника, J987, С 21, с.40-43 | |||

| Авторское свидетельстбр СССР № 1505295, кл.С 11 С 11/40, 1988 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1992-09-23—Публикация

1989-10-17—Подача