Изобретение относится к вычисли тельной технике и может быть исполь зовано для построения универсальных аналого-цифровых комплексов сбора и обработки первичной информации. Известен универсальный аналогоцифровой преобразователь, содержащий компараторный коммутатор, первые входы которого соединены со вхо дными клеммами преобразователя,втор входы - с выходом преобразователя к да в напряжение,входы разрядов .кото го соединены с выходами счетчика,и нератор импульсов l3 . Недостатком устройства является отсутствие возможности обработки сигналов переменного напряжения при различных частотах и их девиации. Цель изобретения - расширение функциональных возможностей. Поставленная цель достигается тем, что в универсальный аналогоцифровой преобразователь, содержащий компараторный коммутатор, первые входы которого соединены со входными клеммами преобразователя, вторые входы - с выходом преобразователя кода в напряжение, входы разрядов которого соединены с выходами счетчика генератора импульсов, введены регистр адреса, дешифратор, генератор одиночного импульса, R-S триггер, два блока элементов И-ИЛИ, элементы И,ИЛИ, И-НЕ, два инвертора, три Л - К триггера и дополнительный счетчик, причем выходы компараторного коммутатора соединены с первыми входами первого блока элементов И-ИЛИ, вторые входы которого соединены с выходами дешифратора и входами первого элемента ИЛИ, выход которого подключен к первому входу элемента И-НЕ, первому входу первого элемента И и через первый инверторк первому входу второго блока элементов И-ИЛИ, второй вход последнего соединен с выходом генератора импульсов, первым входом второго элемента И, первым входом третьего элемента И, третьим входом второго блока элементов И-ИЛИ, четвертый вход которого соединен с выходом генератора одиночного импульса, первым входом первого 3-К триггера, вторым входом второго элемента И, первым входом дополнительного счетчика, второй вход последнего соединен с выходом второго блока элементов И-ИЛИ, пятый вход

KQiBtsgoro соединен с выходом второго твиггера, первый вход которого подключен к выходу второго элемента Hj второй вход - к третьему входу дополнительного счетчика, первому входу третьего О - К триггера, шине Прианан адреса , первому входу R-S - триггера, первому входу счетчика, вгорой вход Которого соединен с выходом третьего элемента И, а третий вход - с вторым входом элемента И-НЕ,первым входом генератора одийочного импульса и выходом первого блока элементов И-ИЛИ, второй вход первого элемента И соединен с шиной Признак адреса , а выход подключен ко второму входу первого О-К триггера,выход которого соединен со вторым входом третьего элемента И и шестым входом рторого блока элементов И-ИЛИ, третий вход третьего элемента И соединен с выходом элемента И-НЕ и через второй инвертор подключен к первому входу второго элемента ИЛИ, второй вход последнего соединен с первым выходом К-5 триггера а выход - с вторым входом третьего 3-К триггера, и третьим входом первого триггера, второй выходЯ-5 триггера соединен с четвертым входом третьего элемента И, а вход дешифратора соединен с выходом регистра адреса, входы которого соединены соответственно с шинами Признак адреса и Код адреса .

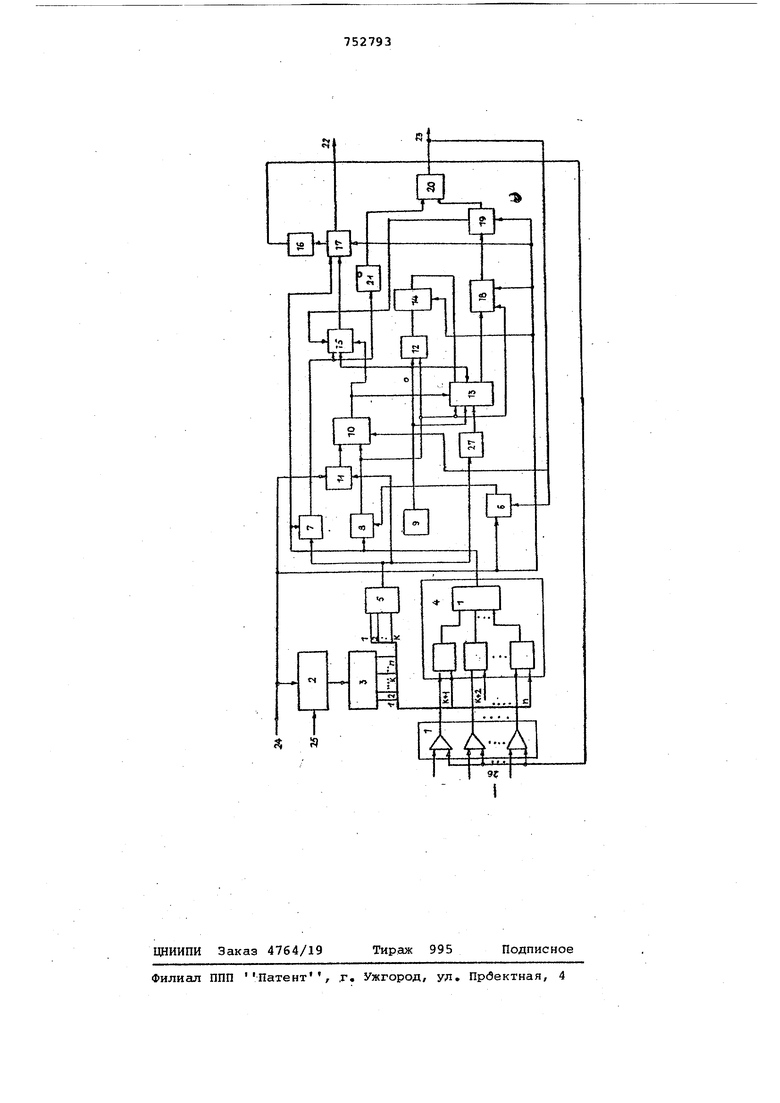

На чертеже схематически изображено устройство.

Универсальный аналого-цифровой преобразователь содержит компараторный коммутатор 1, регистр 2 адреса, дешифратор 3, блок 4 элементов И-ИЛИ, элемент 5 ИЛИ, 3-К триггер 6, элемент И-НЕ 7, генератор 8 одиночного импульса, генератор 9 импульсов,3 - К триггер 10, элементы 11, 12 И, блок 13 элементов И-ИЛИ 3-К триггер 14, элемент 15 И, преобразователь 16 Код-напряжение , реверсивный счетчик 17, реверсивный дополнительный счетчик iSyR-S триггер 19, элемент 20 ИЛИ, инвертор 21 НЕ, магистраль 22 информации, шину 2 Признак информации , шину 24 Признак адреса , шину 25 Кодаадреса, шину 26 аналоговых каналов, инвертор 27 НЕ.

Устройство работает следующим образом,

С приходом сигналов Признак-адреса и Код адреса по шинам 24 и 25 дешифратор 3 подключает выходы компараторного. коммутатора 1 к блоку 4 элементов И-ИЛИ, устанавливаются в нулевое состояние тригге1ха 14, 19 счетчики 17, 18, Выходы дешифратора 3, соответствующие коду каналов постоянного напряжения, поданы на элемент 5 ИЛИ, выход которого подготавливает к работе элемент 7 И-НЕ, и

выход инвертора 27 отключает прохождение серии импульсов с выхода генератора 9 импульсов через блок 13 элементов И-ИЛИ, на дополнительный счетчик 18, Высокие уровни с выхода f элемента 5 ИЛИ и сигнал с шины 24 проходят элемент 11 И и по входу устанавливают триггер 10 в единицу. По заднему фронту импульса Признак адреса генератора 9импульсов сигjj нал проходит элемент 15 и. Подсчет импульсов на счетчике 17 происходит до момента сравнения на выбранном компараторе входного и эталонного набора напряжений. При равенстве

« их на выбранном компараторе возникает высокий уровень, который проходит блок 4 элементов И-ИЛИ,элемент 7 И-НЕ . вырабатывает низкий уровень, запирающий элемент 15 И. Инвертор 21 подает высокий уровень через элемент 20 ИЛИ на шину 23, по которому организуется сигнал Признак информации ,устанавливак1щий в исходные состояния триггеры б и 10,а также разрешающий процесс обмена с ЦВМ информацией, полученной на счетчике 17,

При подключении каналов переменного напряжения на выходе элемента 5 ИЛИ возникает низкий уровень, который подготавливает к работе элемент 15 И, подавая на один из его четырех входов высокий уровень элемента 7 И-НЕ. .Проходя инвертор 27, этот сигнал высоким уровнем подается на.блок 13 элементов И-ИЛИ. Далее

5 устройство находится в ожидании срабатывания выбранного компаратора при сравнении нулевого уровня напряжения выхода преобразователя 16 Код-напряжение с переходом нулевого состояния переменным напряжением на входе компараторного коммутатора 1 из области положительного значения в область отрицательных значений. Предварительно задним фронтом импульса Признак адреса (шина 24) взводится в единичное положение 3 - к триггер 6. При сравнении нулевых уровней измеряемого и эталонного напряжений блок 4 элементов И-ИЛИ подает высокий потенциал с выхода блока 1 на

0 вход генератора 8 одиночного импульса. Высокий уровень, появляющийся на выходе последнего, открывает элемент 12 И и серия импульсов с выхода генератора 9 импульсов, делясь на два

f на 3-к триггере 14, подается на входблока 13 элементов И-ИЛИ. Высокий уровень с выхода генератора 8 поступает на блок 13 И-ИЛИ, а также запускает реверсивный счетчик 18 в . режим счета (сложения) импульсов.

0 Заполнение счетчика 1В продолжается в течение отрицательного полупериода входного напряжения. Переход нулевой точки входного переменного напряжения вызывает отключение блока 4 элементов И-ИЛИ по реакции компараторного коммутатора 1, сброс в О генератора 8, переключение серии импульсов генератора 9 импульсов с делителя (О-К триггера 14) на вход блока 13 элементов и-ИЛИ, установку 3-К триггера 10 в . Дополнительный счетчик 18 работает в ренсиме вычитания частоты серии импульсов с выхода генератора 9. Счетчик 17 работает В следующем режиме при положительной полуволне входного сигнала. Обнуление счетчика 18 проис ходит в момент прохождения входным сигналом максимального значения. Сиг нал обнуления на выходе счетчика 18 установлен R-S триггер 19 в , сигнал с нулевого плеча которого пе рекроет элемент 15 И, счетчик 17 хранит кодовый набор, соответствующий максимуму входного напряжения. Высокий уровень с единичного плеча R -S триггера 19 пройдет элемент 20 ИЛИ и является Признаком информ ции, на шине 23. Этот сигнал обнуляет триггеры 6 и 10, Формула изобретения Универсальный аналого-цифровой преобразователь, содержащий компа- раторный коммутатор, первые входы которого соединены со входными клем мами преобразователя, вторые входыс выходом преобразователя кода в напряжение, входы разрядов которого соединены с выходами счетчика,генератор импульсов,о т л и ч а ю щ и с я тем, что, с целью расширения функциональных возможностей, в него введены регистр адреса, дешифратор генератор одиночного импульса, TZ-S триггер, два блока элементов И-ИЛИ, элементы И, ИЛИ, И-НЕ, два инвертора, три 3 - К триггера и дополнительный счетчик, причем выходы компараторного коммутатора соединены с пер выми входами первого блока элементов И-ИЛИ, вторые входы которого соединены с выходами дешифратора и входами первого элемента ИЛИ, выход которого подключен к первому входу элемента И-НЕ, первому входу пер вого элемента И и через первый инвертор - к первому входу второго блока элементов И-ИЛИ, второй вход последнего соединен с выходом генератора импульсов, первым входом второго элемента И, первым входом третьего элемента И, третьим входом второго блока элементов И-ИЛИ, четвертый вход которого соединен с выходом генератора одиночного импульса, первьгм входом первого 3-К триггера, вторы;м входом второго элемента И, первым входом дополнительного счетчика, второй вход .последнего соединен с выходом второго блока элементов И-ИЛИ,пятый вход которого соединен с выходом второго 3 - К триггера, первый вход которого подключен к выходу второго элемента И, второй вход - к третьему входу дополнительного счетчика, первому входу третьего 3-К триггера, шине Признак адреса , первому входу R-S триггера, первому входу счетчика, второй вход которого соединен с выходом третьего элемеата И, а третий вход - с вторым входом элемента И-НЕ, первым входом генератора одиночного импульса и выходом первого блока Элементов И-ИЛИ, второй вход первого элемента И соединен с шиной Признак адреса , а выход подключен ко второму входу первого 3 - к триггера, выход кЬторого соединен со вторым входом третьего элемента И и шестьом входом второго блока элементов И-ИЛИ, третий вход третьего элемента И соединен с выходом элемента И-НЕ и через второй инвертор подключен к первому входу второго элемента ИЛИ, второй вход последнего соединен с первым выходом R-S триггера, а выход - со вторым входом третьего 3 - К триггера и третьим входом первого 3-1 триггера, второй выход R-S триггера соединен с четвертым входом третьего элемента И, а вход дешифратора соединен с выходом регистра адреса, входы которого соединены соответственно с шинами Признак адреса и Код адреса , Источники информации, принятые во внимание при экспертизе 1. Дроздов А.п. и др. Электронные цифровые вычислительные меицины, 1968, с. 510-511 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсное устройство преобразования сигнала с мостового датчика | 1986 |

|

SU1383474A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Устройство для контроля параметров | 1985 |

|

SU1295420A1 |

| Устройство для дешифрации числового кода | 1990 |

|

SU1785082A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Многоканальный коммутатор | 1988 |

|

SU1541764A1 |

| Адаптивный коммутатор телеизмерительной системы | 1988 |

|

SU1552217A1 |

| Устройство отсчета интервалов времени | 1982 |

|

SU1103228A1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

Si P

Ij 9C I

Авторы

Даты

1980-07-30—Публикация

1978-07-28—Подача