(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ МНОГОФАЗНЫМ ИМПУЛЬСНЫМ РЕГУЛЯТОРОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный параметрический стабилизатор напряжения постоянного тока | 1988 |

|

SU1628057A1 |

| РЕВЕРСИВНЫЙ ВЕНТИЛЬНЫЙ ЭЛЕКТРОПРИВОД (ВАРИАНТЫ) | 1999 |

|

RU2142193C1 |

| Способ управления трехфазным мостовым инвертором и устройство для его осуществления | 1974 |

|

SU633128A1 |

| Устройство для размагничивания постоянных магнитов | 1980 |

|

SU900324A1 |

| Асинхронный электропривод | 1989 |

|

SU1697252A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Позиционный электропривод | 1984 |

|

SU1270859A1 |

| Система сбора и обработки информации | 1977 |

|

SU822662A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1983 |

|

SU1124438A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2336670C1 |

1

Изобретение относится к электротехнике и может быть использовано в регулируемых вторичньЕХ источниках электропитания.

Известно управление группой импульсных регуляторов, при котором у регуляторов,, син-. хронизированных между собой со взаимным фазовым сдвигом и с независимым изменением скважности импульсов напряжения на нагрузке каждого регулятора в отдельности, синхронизация осуществляется поочередно-последовательным включением последующих регуляторов при отключении предыдущих регуляторов 1.

Недостатком такого устройства управления группой импульсных регуляторов является необходимость иметь мощность каждого отдельного регулятора не меньше мощности нагрузки при параллельной работе регуляторов на общую нагрузку.

Наиболее близким к изобретению является устройство для управления многофазным импульсным регулятором, содержащим N однофазных импульсных регуляторов, синхронизированных между собой со взаимным временным сдвигом, равным N-ой части от периода

повторения импульсных процессов в регулято-1 pax, и блок управления, состоящий из задающего генератора, к выходу которого подключены делитель, частоты и регистр сдвига на N позиций 2.

5 Недостатком такого устройства является неизбежное ухудщение качества напряжения на нагрузке при возможном отказе одного из регуляторов, так как на входе фильтра появляется низкочастотная пульсация f - с уд10Т

военной амплитудой по сравнению с амплитудой пульсаций при исправных регуляторах.

Целью изобретения является повышение надежности работы при отказе одного из N ре 5 гуляторов.

Это достигается тем, что в блок управления введены N датчиков работоспособности регуляторов и блок логики, причем выходы датчиков работоспособности регуляторов соединены

20 через блок логики с делителем частоты и с входами регуляторов, делитель частоты соединен через блок логики с регистром сдвига, а выходы регистра сдвига соединены через блок логики с входами регуляторов, датчик работоспособности каждого i-oro регулятора соедиkieH через блок логики с входами всех регуляторов от i-oro до N-oro, где i 2, 3...(N-1), а датчики работоспособности первого и N-oro регуляторов соединены через блок логики с входами первого и N-oro регуляторов соответственно, каждый выход регистра сдвига, кроме первого и N-oro, соедшген через блок логики с входами i-oro и (i - 1) регуляторов, а первый и N-ый выходы регистра соединены через блок логики соответственно с входами первого и N-oro регуляторов.

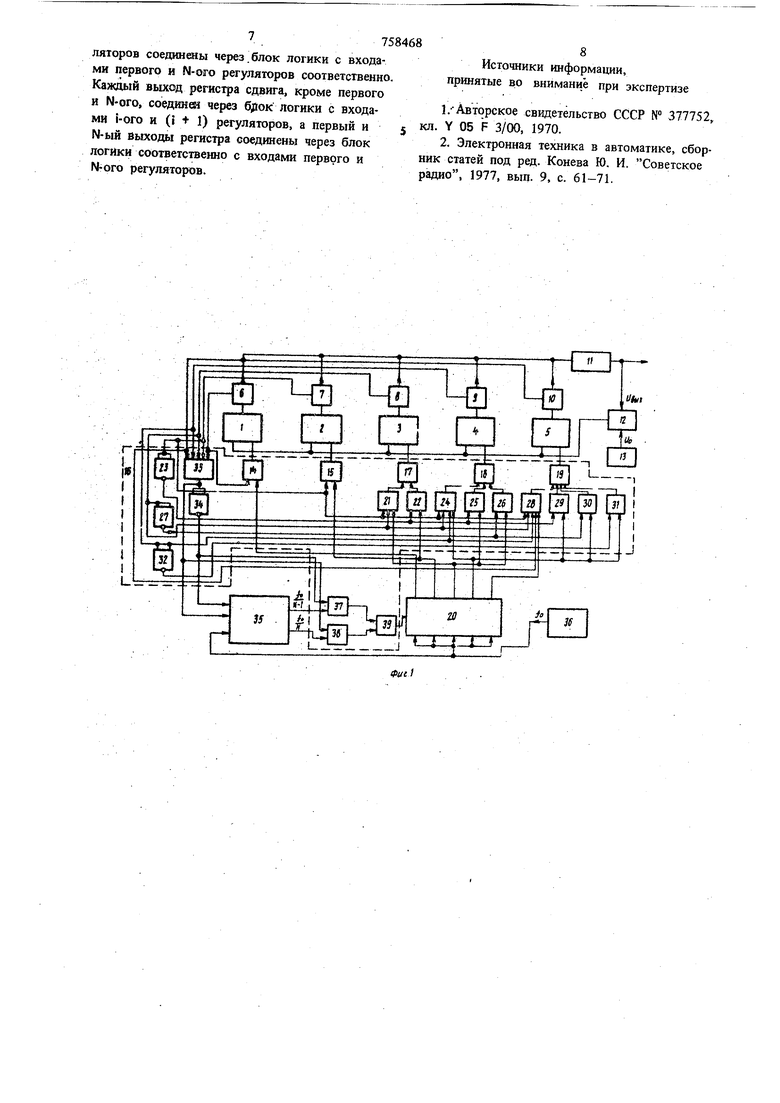

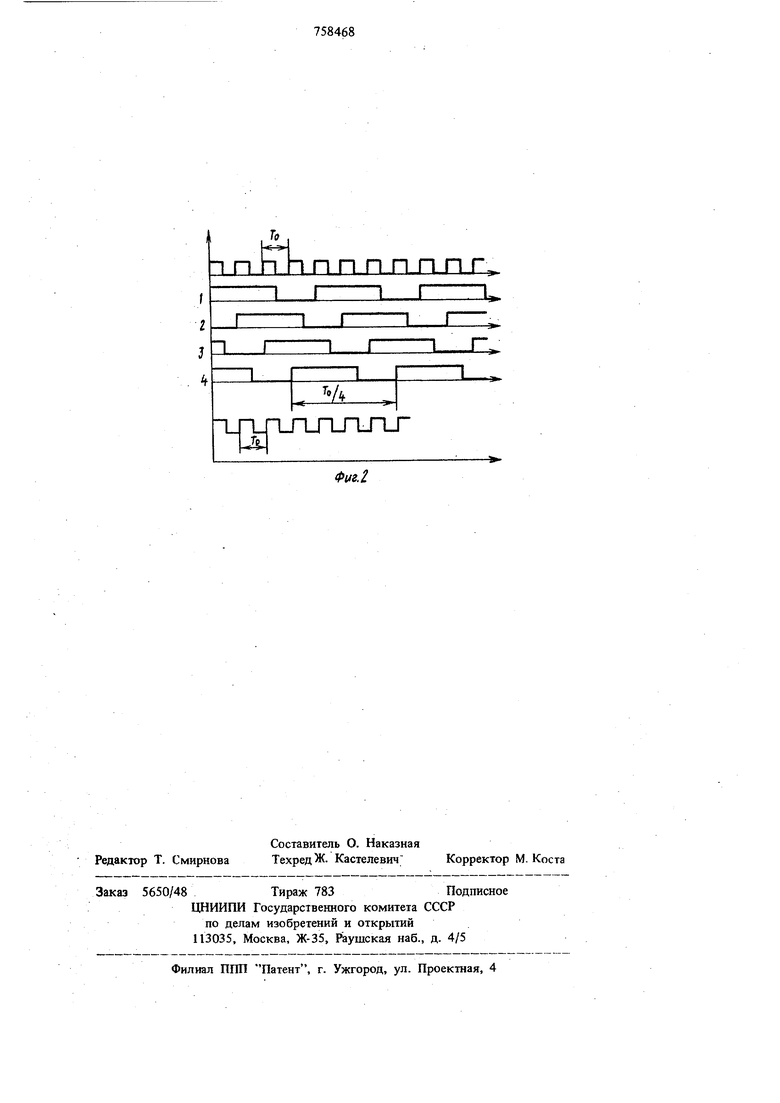

На фиг. 1 приведена схема устройства для осуществлшия способа управления группой импульсных регуляторов, где на фиг. 2 показано входное напряжение фильтра.

Устройство состоит из пяти широтно-импульсных регуляторов напряжения 1-5. Выход каждого из регуляторов 1-5 подключен через датчики 6-10 работоспособности регуляторов (например, пороговые датчики тока) к входу фильтра 11.

Регуляторы 1-5 имеют два входа, один из которых у каждого регулятора подключен к выходу сумматора 12, с которого поступает напряжение обратной связи, пропорциональное разности вь1ходного напряжения стабилизатора и источника опорного напряжения 13. На вторые входы ррегуляторов 1 и 2, подключенные к выходам двухвходовых элементов И 14, 15, поступает прямоугольное напряжение с выходов двухвходовых элементов И 14, 15 блока логики 16. На второй вход регулятора 3, подключе1шый к выходу двухвходового элемента ИЛИ 17, поступает прямоугольное напряжение с выхода двухвходового элемента ИЛИ 17 блока логики 16, на. второй вход регулятора 4, подключенный к выходу трехвходового элемента ИЛИ 18, поступает прямоугольное напряжение с выхода трехвходового элемента ИЛИ 18 блока логики 16, а на второй вход регулятора 5, подключенный к выходу четырехвходового элемента ИЛИ 19, поступает прямоугольное напряжение с выхода четырехвходового элемента ИЛИ 19 блока логики 16. На входы двухвходового элемента И 14 блока логики 16 связанного с входом регулятора 1, поступают соответственно сигнал с выхода датчика 6 регулятора I и прямоугольное напряжение с первого выхода регистра сдвига 20 на пять позиций. На входы двухвходового элемента И 15 блока логики 16, связанного с входом регулятора 2, поступают соотвественно сигнал с выхода датчика 7 регулятора 2 и прямоугольное напряжение со втррого выхода регистра 20. На входы двухвходового элемента ИЛИ 17 блка логики 16, связанного с входом регулятора 3, поступает прямоугольное напряжение либо с выхода трехвходового элемента И 21 блока логики 16, либо с выхода двухвходового элемента И 22 блока логики 16.

Входы трехвходового элемента И 21 связаны с выходом датчика 7 регулятора 2, с выходом датчика 8 регулятора 3 и третьим выходом регистра сдвига 20. Один из входов двухвходового элемента И 22 связан через элемент ИЛИНЕ 23 с выходом датчика 7 регулятора 2, а второй - со вторым выходом регистра сдвига 20. На входы трехвходового элемента ИЛИ 18 блока логики 16, связанного с входом регулятора 4, поступает прямоугольное напряжение либо с выхода четырехвходового элемента И 24, либо с выходов одного из двух двухвходовых элементов И 25, 26 блока логики 16 Входы элемента И 24 связаны с выходом датчика 7 регулятора 2, с выходом датчика 8 регулятора 3, с выходом датчика 9 регулятора 5 и четвертым выходом регистра сдвига 20. Один из входов элемента И 25 связан через элемент И ЛИ-НЕ 23 с выходом датчика 7 регулятора 2, а второй - с третьим выходом регистра сдвига 20. Один из входов элемента И 26 связан через элемент И ЛИ-НЕ 27 с выходом датчика 8 регулятора 3, а второй также с третьим выходом регистра сдвига 20. На входы четырехвходового элемента ИЛИ 19 блока логики 16, связанного с входом регулятора 5, поступает прямоугольное напряжение либо с выхода пятивходового элемента И 28, либо с выходов одного из трех двухвходовых элементов И 29, 30, 31 блока.логики 16. Входы элемента И 28 связаны с выходом датчика 7 регулятора 2, с выходом датчика 8 регулятора 3, с выходом датчика 9 регулятора 4, с выходом датчика 10 регулятора 5 и пятым выходом регистра сдвига 20. Один из входов элемента И 29 связан через элемент ИЛИ-НЕ 23 с выходом датчика. 7 регулятора 2, а второй с четвертым выходом регистра сдвига 20. Один из входов элемента И 30 связан через элемент ИЛИ-НЕ 27 с выходом датчика 8 регулятора 3 второй - с четвертым выходом регистра сдвига 20. Один из входов элемента И 31 связан через элемент ИЛИ-НЕ 32 с выходом датчика 9 регулятора 4, второй - с четвертым выходом регистра сдвига 20.

Кроме того, выходы датчиков 6-10 связаны с входами пятивходового элемента И 33 блока логики 16, выход которого через элемент ИЛИ-НЕ 34 связан с одним из входов делителя частоты 35 и непосредственно связан со вторым входом, делителя частоты 35, Третий вход делителя частоты 35 связан с выходом задающего генератора 36, имеющего частоту fo И период То. Делитель частоты имеет два вылп 1 vjf D мач, IU iDl riivji t; j, /i. к

fo / fn fo / fo

fo

- /) и - (1,

хода с частотами

ко

4 W-1 / 5 N /

5 торые соединены соответствеиио с одним из входов двухвходовых элементов И 37, 38 блока логики 16. Второй вход элемента И 37 соединен с выходом элемента И ЛИ-НЕ 34 бло ка логики 16, а второй вход элемента И 38 соединен с выходом элемента И 33 блока логики 16. Выходы элементов И 37, 38 соединены, чер элемент ИЛИ 39 с информационным входом гистра сдвига 20. На синхронизирующие входы регистра сдвига 20 подаются импульсы с вы хода задающего генератора 36 частотой fo и периодом TQ. Устройство работает следующим образом. Если все регуляторы исправны, то на делитель частоть 35 с элемента И 33 блока логики 16 приходит сигнал, разрещающий деление в 5 раз (N раз) и на регистр сдвига 20 через элементы И 38 н ИЛИ 39 блока логики 16 проходят прямоугольные импульсы частотой ID 10 , где fg - частота задающего генера тора. На выходах регистра 20 появляются им ., 0 пульсы частотой - и сдвинутые во времени 5 относительно др)тг друга на величину . При этом выходы регистра 20 подключаются через блок логики 16 к входам регуляторов 1-5 в таком порядке: первый выход регистра 20 к входу регулятора 1, второй - к входу регулятора 2, третий - к входу регулятора 3 и т.д. Между импульсными процессами в регуляторах 1-5 установится взаимный временный сдвиг г TO при необходимой скважности выходного напряжения. Если условно обозначить сигналы с датчиков работоспособности 6-10 через X с соответствующим индексом, а сигналы с выходов регистра сдвига 20 через Y с соответствующим индексом, то структурные формулы для появления сигналрв на входах регуляторов 1-5 будут такими: FI Хб-Y, р2 Xv YI XvX,Y3 + X,-Ya Y4 + XT-YS t Xg-Yj Х7 Xg Xg YS 4- X,-Y4 + X8-Y4f Х7 Xg Xg в общем случае F ) (м+3) (N + 2) (И-) (Nt 3) (N- 1) 5 Y (N-l) (N-1). . При отказе одного любого из регуляторюв, например регулятора 4, сигнал с датчика рабо тоспособности 9 этого регулятора обращается в логический нуль и в соответствии со структурными формулами будем иметь: FI Хб- YI FZ X7-Y2 РЗ X -Xg-Ya FS 86 Таким образом, при отказе регулятора 4 вход его отключается блоком логики 16 от ре г.истра сдвига 20 и одновреме шо вход регулятора 5 будет соединен с четвертым выходом регистра сдвига 20. Одновременно при отказе одного любого регулятора с элемента И ЛИ-НЕ 34 блока логики 16 на делитель частоты 35 поступает сигнал, разрещающий деление в 4 раза (N-1 раз), и на регистр сдвига 20 через элементы И 37 и ИЛИ 39 блока логики 16 ч.-, ffl. .1 о начинают поступать импульсы частотой На выходах регистра сдвига 20 появятся импульсы частотой- и сдвинутые друг относительно друга во времени на величину г ) JQ. (N - l)fo Следовательно, при отказе одного из регуляторов, например регулятора 4, между импульсными процессами в исправных регуляторах 1, 2, 3, 5 сохраняется последовательный сдвиг Ьо времени г TO и иэменяетсяг рабочая частота исправных регуляторов, в результате чего не происходит ухудшения качества напряжения на нагрузке. На фиг. 2 noka3aHo входное напряжение фильтра 11 при возможном отказе одного из регуляторов, например регулятора 4. Таким образом, в предложенном устройстве при отказе одного из регуляторов не происходит изменения качества, выходного напряжения. Что значительно увеличивает надежность работы группы импульсных регуляторов. Формула изобретения Устройство для управления многофазным импульсным регулятором, содержащим N однофазных импульсных регуляторюв, синхронизированных между собой со взаимным временным сдвигом, равным N-ой части от периода повторения импульсных процессов в регуляторах, и блок управления, состоящий из задающего генератора, к выходу которого подключены делитель частоты и регистр сдвига на N позиций, отличающееся тем, что, с целью повыщения надежности работы при отказе одного из N регуляторов, в блок управления введены N датчико1з работоспособности регуляторов и блок логики, причем выходы датчиков работоспособности регуляторов соединены через блок логики с делителем частоты и с входами регуляторов, делитель частоты соединен через блок логикИ; с регистром сдвига, а выходы, регистра сдвига соединены через блок логики с входами регуляторов, датчик работоспособности каждого i-oro регулятора соединен через блок логики с входами всех регуляторов от j-oro до N-oro, где i 2, 3... (N-1), а датчики работоспособности первого и N-oro регу .75 ляторов соединены через блок логики с входами первого и N-oro регуляторов соответственно. Каждый выход регистра сдвига, кроме первого и N-oro, соединен через логики с входами i-oro и (I -f 1) регуляторов, а первый и N-ый выходы регистра соединены через блок логики соответственно с входами первого и N-oro регуляторов. Источники информации, принятые во внимание при экспертизе 1.-Авторское свидетельство СССР № 377752, кл. Y 05 F 3/00, 1970. 2. Электронная техника в автоматике, сборник статей под ред. Конева Ю. И. Советское радио, 1977, вып. 9, с. 61-71.

Г1ПП1ПП Г1 Г.

JL

-1

Авторы

Даты

1980-08-23—Публикация

1978-05-10—Подача