i

Изобретение относится к технике электрической связи и может быть использовано в цифровых системах передачи, применяющих многоуровневые блочные балансные коды с избыточностью.

Известно устройство блочной синхронизации кодов, в котором для осуществления синхронизации используются запрещенные комбинации, появляющиеся на каждом стыке кодовых слов Л .

Недостатком известного устройства является избыточность кода, приводящая к низкой экономической эффективности цифровой системы передачи.

Наиболее близким к предлагаемому по техническому решению является устройство для блочной синхронизации цифровой системы передачи, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещенных слов, а также последовательно соединенные делитель частоты на два и умножитель частоты на три, при этом первьш, второй и третий входы регистра сдвига являются входами устройства, причем третий вход регистра сдвига объединен с входом делителя частоты иа два, а также, детектор нарушений, блок расширения импульсов, двоичный счетчик на восемь, кЬльдевой счетчик на че тыре, четыре одновибратора, синхронизирующий блок, блок памяти фазы, четыре элемента ШШ-НЕ 2J ,

Однако известное устройство обладает низкой помехоустойчивостью.

Цель изобретения - повьш ение помехоустойчивости передачи информации.

Поставленная цель достигается тем, что в устройство дпя блочной синхронизации щ-1фровой системы передачи, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещенных слов, а также последовательно соединенные делител частоты на два и умножитель частоты на.три, при этом первый, второй и третий входы регистра сдвига являются входами устройства, причем трети вход, регистра сдвига объединен с

244382

входом делителя частоты на два, введены кольцевой счетчик на., три, первый, второй, третий и четвертый синхронизируемые кольцевые счетчики 5 на четьфе, блок задержки импульсов и блок детектирующей логики, содержа1ЦИЙ первый, второй и третий двухвходоные элементы И, и трехвходовой элемент ИЛИ, выход которого через блок

О задержки импульсов подключен к первому входу четвертого синхронизируемого кольцевого счетчика на четыре, второй вход которого объединен с третьим входом регистра сдвига и. пер5 выми входами первого, второго и

третьего синхронизируемых кольцевых счетчиков на четыре, к вторым входам которых подключены выходы кольцевого счетчика на три, к входу которого

0 подключен выход детектора запрещенных слов, при этом выход первого синхронизируемого кольцевого счетчика на четырех подключен к первьм входам первого и третьего двухвходовых зле5 ментов И, выход второго синхронизируемого кольцевого счетчика на четыре . подключен к второму входу первого двухвходового элемента И и первому входу второго двухвходового элемента

0 И, -а выход третьего синхронизируемого кольцевого счетчика на четыре подключен к вторым входам второго и третьего двухвходовых элементов И, выходы которых, а также выход пер5 вого двухвходового элемента И подклю чены к входам трехвходового элемента ИЛИ..

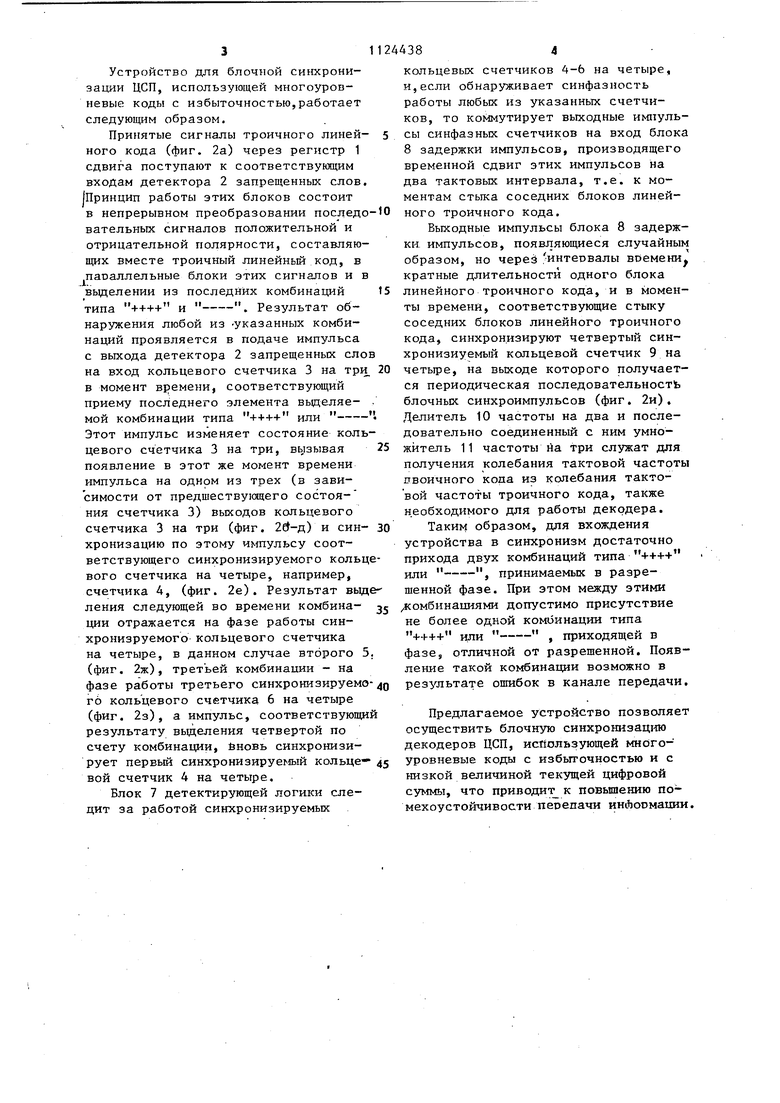

На фиг. 1 представлена структурная электрическая схема устройства

Q ДЛЯ блочной синхронизации цифровой системы передачи; на фиг. 2 - временные диаграммы, поясняющие его

работу.

1

Устройство для блочной синхрони5 зации цифровой системы передачи (цеп) содержит регистр 1 сдвига, детектор 2 запрещенных слов, кольцевой счетчик 3 на три, первый,- третий синхронизируемые кольцевые счет0 чики 4-6 на четыре, блок 7 детектирующей логики, блок 8 задержки импульсов, четвертый 9 синхронизируемый кольцевой счетчик на четыре, делитель 9 частоты на два, умножитель 11

5 частоты на три, блок 7 детектирующей логики, содержащий первьш - третий двухвходовые элементы И 12 - 14, трехвходовьп элемент ИЛИ 15. Устройство для блочной сиюсронизации цеп, использующей многоуровневые коды с избыточностью,работает следующим образом. Принятые сигналы троичного линей ного кода (фиг. 2а) через регистр 1 сдвига поступают к соответствующим входам детектора 2 запрещенных слов |Принцип работы этих блоков состоит в непрерывном преобразовании посдед вательных сигналов положительной и отрицательной полярности, составляю щих вместе троичный линейньм код, в паоаллельные блоки этих сигналов и выделении из последних комбинаций типа ++++ и . Результат обнаружения любой из -указанных комбинаций проявляется в подаче импульса с выхода детектора 2 запрещенных сло на вход кольцевого счетчика 3 на три в момент времени, соответствующий приему последнего элемента вьделяемой комбинации типа ++++ или Этот импульс изменяет состояние кол цевого счетчика 3 на три, вызывая появление в этот же момент времени импульса на одном из трех (в зависимости от предшествующего состоякия счетчика 3) выходов кольцевого счетчика 3 на три (фиг. 2Й-д) и синхронизацию по этому импульсу соответствующего синхронизируемого коль вого счетчика на четыре, например, счетчика 4, (фиг. 2е). Результат вьщ ления следующей во времени комбинации отражается на фазе работы синхронизруемого кольцевого счетчика на четыре, в данном случае второго (фиг. 2ж), третьей комбинации - на фазе работы третьего синхронизируемо го кольцевого счетчика 6 на четыре (фиг. 2з), а импульс, соответствующи результату выделения четвертой по счету комбинации, йновь синхронизирует первый синхронизируемый кольце- вой счетчик 4 на четыре. Блок 7 детектирующей логики следит за работой синхронизируемых 4384 кольцевых счетчиков 4-6 на четыре, и,если обнаруживает синфазность работы любых из указанных счетчиков, то коммутирует выходные импульсы синфазных счетчиков на вход блока 8 задержки импульсов, производящего временной сдвиг этих импульсов на два тактовых интервала, т.е. к моментам стыка соседних блоков линейного троичного кода. Выходные импульсы блока 8 задержки импульсов, появляющиеся случайным образом, но черей интервалы воемени кратные длительности одного блока линейного троичного кода, и в моменты времени, соответствующие стыку соседних блоков линеййого троичного кода, синхронизируют четвертый синхронизиуемый кольцевой счетчик 9 на четыре, на выходе которого получается периодическая последовательность блочных синхроимпульсов (фиг. 2и). Делитель 10 частоты на два и последовательно соединенный с ним умножитель 11 частоты йа три служат для получения колебания тактовой частоты двоичного кода из колебания тактовой частоты троичного кода, также необходимого для работы декодера. Таким образом, для вхождения устройства в синхронизм достаточно прихода двух комбинаций типа ++++ или , принимаемых в разрешенной фазе. При этом между этими омбинациями допустимо присутствие не более одной комбинации типа ++++ или приходящей в фазе, отличной от разрешенной. Появление такой комбинации возможно в результате ошибок в канале передачи. Предлагаемое устройство позволяет осуществить блочную синхронизащда декодеров ДСП, использующей многоуровневые коды с избыточностью и с низкой величиной текущей цифровой суммы, что приводит к повышению помехоустойчивости передачи инйоомации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для блочной синхронизации цифровой системы передачи | 1984 |

|

SU1197119A2 |

| Устройство для блочной синхронизации цифровой системы передачи | 1985 |

|

SU1376258A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство для преобразования двоичной последовательности в балансный троичный код | 1991 |

|

SU1807561A1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1985 |

|

SU1376257A1 |

| Устройство для преобразования двоичной последовательности в блочный балансный троичный код | 1986 |

|

SU1324115A1 |

| Устройство цикловой синхронизации блочных кодов | 1989 |

|

SU1688434A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Устройство синхронизации по циклам | 1983 |

|

SU1172053A1 |

УСТРОЙСТВО ДЛЯ БЛОЧНОЙ СИНХРОНИЗАВДИ ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещенных слов, . а также последовательно соединенные делитель частоты на два и умножитель частоты на три, при этом первый, второй и третий входы регистра сдвига являются входами устройства, причем тоетий вхоп регистра сдвига объединен с входом делителя частоты на два, отличающе-еся тем, что, с целью повышения помехоустойчивости передачи информации, . уведены кольцевой счетчик на три, первый, второй, третий и четвертый синхронизируемые кольцевые счетчики на четыре, блок задержки импульсов и блок детектирующей логики, содержащий первый, второй и третий двухвходовые элементы И и трехвкодовый элемент ИЛИ, выход которого через блок задержки импульсов подключен к первому входу четвертого синхронизируемого кольцевого счетчика на четьфе, второй вход которого объединен с третьим входом регистра сдвига .и первыми входами первого, второго и. третьего синхронизируемых кольцевых счетчиков на четыре, к вторым входам которых подключены выходы кольцевого Счетчика на три, к входу которого подключен выход детектора запрещенных слов, при этом выход (О первого синхронизируемого кольцевого счетчика на четыре подключен к первым входам первого и третьего двухвходовых элементов И, выход второго синхронизируемого кольцевого счетчика на четыре прдключен к второму входу первого двухвходового элемента И и первому входу второго двухвходового элемента И, а вьвсод третьегосинхронизируемого кольцевого счетчика на четыре подключен к вторым входам второго и третьего двухвходовых элементов И, выходы которых, а также выход первого двухвходового элемента И подключены к входам трехвходового элемента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Стиффлер Дж.Дж | |||

| Теория синхронной связи | |||

| М., Связь, 1975, с | |||

| Нефтяная топка для комнатных печей | 1922 |

|

SU326A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ сматывания нити с паковки и устройство для его осуществления | 1988 |

|

SU1564085A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-15—Публикация

1983-04-04—Подача