1

Изобретение относится к вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые.5

Известен аналого-цифровой преобразователь, содержащий блок сравнения, преобразователь код-напряжение, регистр, распределитель импульсов, генератор импульсов, .эле- tO менты И, предназначенный для/поразрядного кодирования входного напряжения fl .

Однако такой преобразователь имеет сложный метрологический контроль j и низкую надежность.

Известен аналого-цифровой преобразователь, содержащий блок управления, регистр., цифро-аналоговый пре-. образователь, блок сравнения, причем 20 выход блока управления соединен со входом регистра, выход которого соединен со входом,цифроаналогового преобразователя, выход цифро-аналоroBOto преобразователя соединен со 25 зторым входом блока сравнения, первый вход которого является входом аналого-цифрового преобразователя, выход блока сравнения соединен со входом блока управления 2.30

Однако аналого-цифровой преобразователь имеет сложный метрологический контроль и не позволяет правильно кодировать преобразуемую аналоговую величину при расстройке или неисправности хотя бы одного из разрядов цифроаналогового преобразователя.

Целью изобретения является упрощение метрологического контроля и повышение надежности, заключающееся в возможности правильного кодирования входной аналоговой величины при расстройке или неисправности одного и более разрядов цифроаналогового преобразователя.

Указанная цель достигается тем, что в ансшого-цифровой преобразователь, содержащий блок управления, первый регистр, цифроаналоговый Преобразователь, блок сравнения введены блок выделения разности, пороговый элемент, второй регистр, блок развертки кода, блок приведения кода к ;«1инимальной форме и цифровой коммутатор, причем выход цифроаналогового преобразователя соединен со входом блока выделения разности, выход которого соединен с информацион

ным входои порогового элементав йыход порогового элемента соединен со вторым входом блока управления, управляющие входы цифрового коммутатора, порогового элемента блока развертки кода, блока приведения кода к минимальной форме и вход второго регистра соединены с соответствующими выходами блока управления, выход блока развертки кода соединен с первым информационным входом цифрового коммутатора/ выход которого соединен со ВХОДОМ; цифроаналогового преобразователя, выход второго регистра, соединен со вторым входом первого регистра, выход которого соединен с информационным входом блока развертки кода, вторым информационным входом цифрового коммутатора и информационным входом блока приведения к минимальной форме.

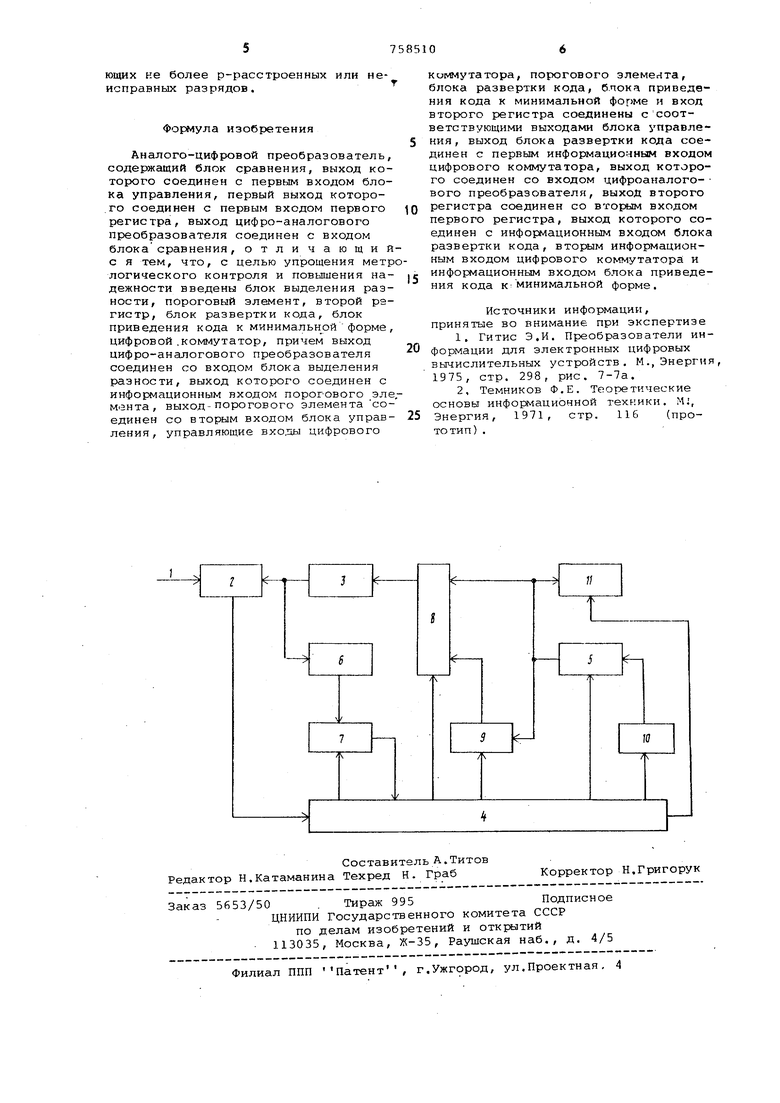

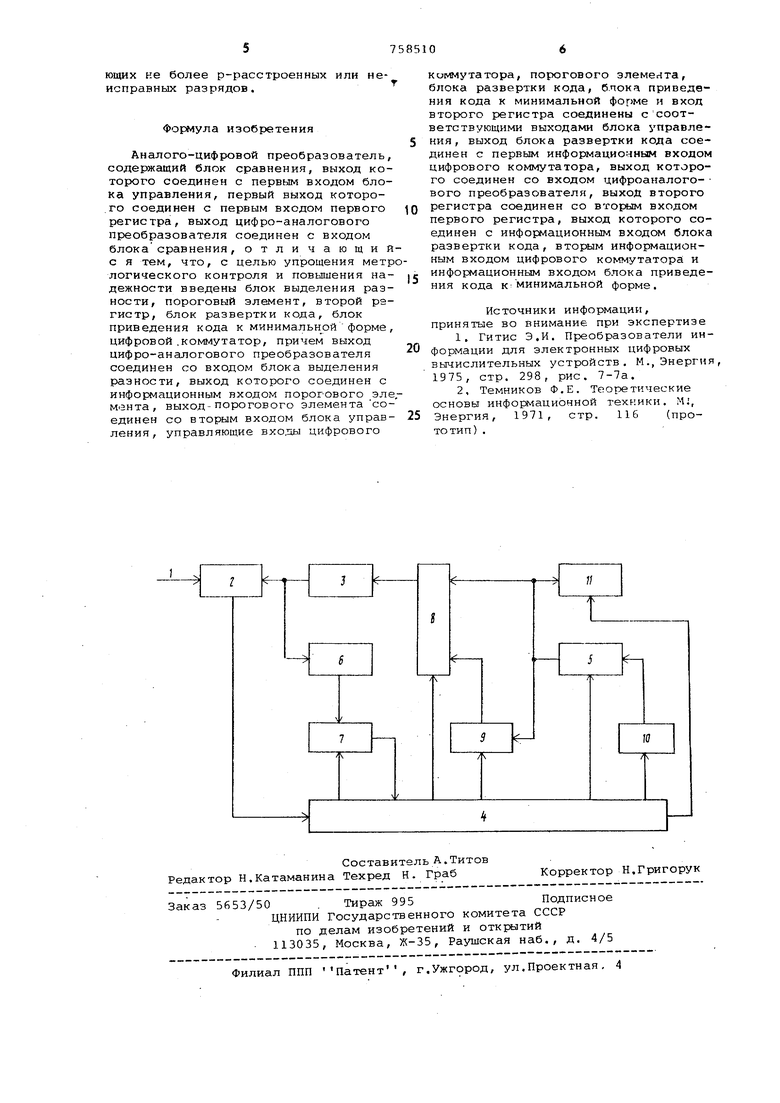

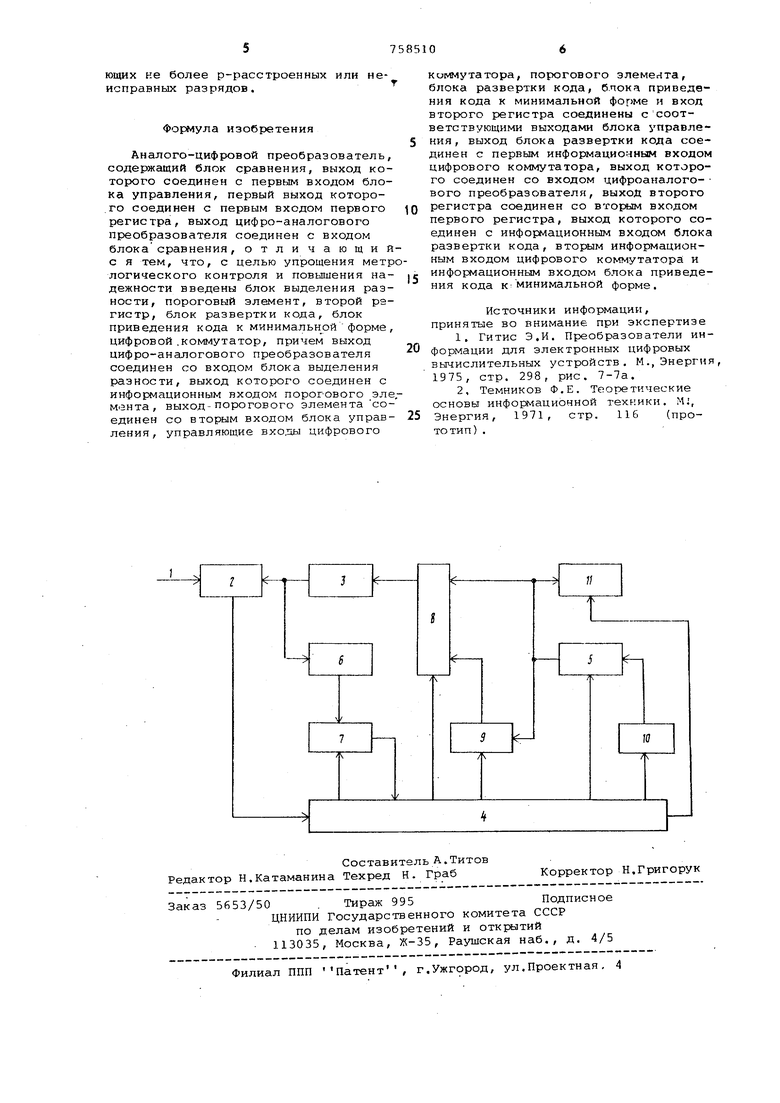

Структурная электрическая схема уст-ройства приведена на чертеже.

Устройство содержит входную шину 1, блок 2 сравнения, цифроаналого- вый преобразователь 3, блок 4 управления, регистр 5, блок 6 выделения разности, осуществляющий выделение и линейное преобразование величины расстройки разрядов цифроаналогового преобразователя 3, пороговый элемент 7, цифровой коммутатор 8, блок У развертки кода, регистр 10, блок И приведения кода к минимальной форме.

В первом такте блок 4 вырабатывает первую серию команд, записывая единицу в первый (стариий) разряд регистра 5, и включает первый канал цифрового коммутатора 8,обеспечивая тем самым включение первого (старшего) разряда цифроаналогового преобразователя 3, Вторая .серия команд включает блок 9, второй канал цифрового коммутатора 8 и пороговый элемент 7, производя при этом развертку первого разряда цифроаналогового пробразователя 3. Блок 6 осуществляет линейное преобразование разности первого и суммы второго и (р+1)-го разрядов цифроаналогового преобразователя 3. В случае превышения этой разностью допустимого предела, происходит срабатывание порогового элемента 7 и запись единицы в первый разряд регистра 10. В конце первого такта происходит сброс в нулевое состояние регистра 5, порогового элемента 7 и выключение блока 9. На. втором такте блок 4 второй серией команд записывает единицу во второй разряд регистра 5 и включает лервЬйканал цифрового коммутатора Ь, обеспечивая тем caMbSKi: включение второго разряди цифроаналогового преобразователя 3, Вторая серия команд включает блок 9, второй канал цифрового коммутатора Ъ и пороговый элемент 7, производя при этом развертку второго разряда цифроаналогового преобразователя 3. так же как и в первом такте блок 6 и пороговый элемент 7 вырабатывает соответствующий сигнал, подаваемый в блок 4. В оставшихся (п-2}-тактах схема работает аналогичным образом, обеспечивая последовательное включение и развертку оставшихся (п-2)-разрядов дифроаналогового преобразователя 3.

Запись номера позиции расстроенного или неисправного разряда регистр 10 происходит следующим образом. Если на 1-м такте пороговый элемент 7 сработал первый раз, то в i-й разряд регистра записывается единица, а в остальных разрядах остаются нули.

Если пороговый элемент 7 срабатывает и на (1+1)-м такте, то в (1+1)-й разряд регистра 10 записывается единица, а в i-й разряд записывается ноль.Запись единиц в последующие разряды и нулей в предыдущие разряды происходит до тех пор, пока не перестанет срабатывать пороговый элемент 7

В режиме аналого-цифрового преобразования устройство осуществляет поразрядное преобразование входной аналоговой величины и работает известны образом. Отличие состоит в том, что расстроенные или неисправные разряды номера которых записаны в регистре 10, на соответствующем такте не включаются. Блок У, блок 6, пороговый элемент 7 при работе преобразователя в этом режиме не участвуют.Поскольк золотой р-код при р 1 является избыточным, то несмотря на наличие не более р расстроенных или неисправных разрядов, код входной аналоговой величины получится правильным, только форма его записи будет неминимальной, поэтому на последнем такте преобразования блок 4 включает блок 11, в результате чего на выходе блока 11 полученный код будет в минимальной форме. Приведение к минимальной форме представления золотого р-кода осуществляется путем последовательного проведения операций свертки и развертки.

Введение новых блоков и связей обеспечивает упрощение метрологического контроля и выполнение его автоматически, а также повышение надежности, заключающееся в правильном кодировании входной аналоговой величины при расстройке или неисправности не более р-разрядов цифро-аналогового преобразователя (где р- ц раметр используемого кода). Это позволяет также увеличить процент выпуска годной продукции при серийном изготовлении налого-цифровых преобразователей Ъ вяде больших интегральных схем за счет включения в объем готовлй продукции преобразователей, имеющих не более р-расстроенных или неисправных разрядов. Формула изобретения Аналого-цифровой преобразователь содержащий блок сравнения, выход которого соединен с первым входом блока управления, первый выход которого соединен с первым входом первого регистра, выход цифро-аналогового преобразователя соединен с входом блока сравнения, отличающий с я тем, что, с целью упрощения метр логического контроля и повьпиения надежности введены блок выделения разности, пороговый элемент, второй рэгистр, блок развертки кода, блок приведения кода к минимальнойформе цифровой.коммутатор, причем выход цифро-аналогового преобразователя соединен со входом блока выделения разности, выход которого соединен с информационным входом порогового эл мента, выход-порогового элемента со единен со вторым входом блока управ ления, управляющие вхо.цы цифрового Коммутатора, порюгового злемента, блока развертки кода, блока приведения кода к минимальной форме и вход второго регистра соединены ссоответствующими выходами блока управления, выход блока развертки кода соединен с первым информационным входом цифрового коммутатора, выход которого соединен со входом цифроаналого- вого преобразователя, выход второго регистра соединен со вторым входом первого регистра, выход которого соединен с информационным входом блока развертки кода, вторым информационным входом цифрового коммутатора; и информационным входом блока приведения кода к минимальной форме. Источники информации, принятые во внимание при экспертизе 1.Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия, 1975, стр. 298, рис. 7-7а. 2,Темников Ф.Е. Теоретические основы информационной техники. MJ, Энергия, 1971, стр. 116 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Цифро-аналоговый преобразователь | 1978 |

|

SU947955A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU928632A1 |

Авторы

Даты

1980-08-23—Публикация

1978-06-07—Подача