1

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

Цель изобретения - повьшение достоверности аналого-цифрового преобразователя ,

.На фиг. 1 приведена функциональная схема аналого-цифрового преобразователя (АЦП); на фиг. 2 - функциональная схема блока управления; на фиг. 3 и 4 - граф-схема алгоритма работы устройства.

Аналого-цифровой преобразователь содержит входную шину 1, блок 2 сравнения, цифроаналоговый преобразователь 3 (ЦАП), второй регистр 4 (2РГ), первый блок 5 развертки кода (1БРК), первый блок 6 элементств ИЛИ, второй блок 7 элементов ИЛИ второй блок 8 элементов И (1БЛЭ И), второй блок 9 развертки кодов (2ВРК блок 10 управления, генератор. 11 та тактовых импульсов, выгодные информационные шины 12, Выходные конТ-г рольные шины 13. Блок 10 управления содержит выходы 14-22 с первого по девятый и входы 23-25 с первого по третий,АЦП содержит также п.ервый блок элементов И 26 и первый регистр 27 (1РГ).

Блок 10 управления (фиг.. 2) выполнен на первом и втором регистрах 28 и 29, инверторе 30, постоянном запоминающем устройстве 31 (ПЗУ).

Цифроаналоговый преобразователь (ЦАП) 3 должен быть построен на основе избыточного измерительного кода (ИИК), например кода Фибоначчи или золотой пропорции. Аналого- цифровые преобразователи, построенные на основе избыточных измерительных кодов, обладают многозначностью выходной характеристики, что позволяет проводить контроль их метрологических характеристик. В основе контроля лежит представление одной аналоговой величины различным кодовыми комбинациями и сравнение последних между собой. При этом, если веси разрядов А1Щ не имеют отклонений от требуемых значений, то этим кодовым комбинациям будет соответствовать один аналоговый эквивалент. Если веса разрядов А1Щ имеют отклонения от требуемых значений то различным кодовым комбинациям

23368

будут соответствовать различные аналоговые эквиваленты.

Данное обстоятельство лежит в основе контроля предлагаемого анало5 го-цифрового преобразователя. При- чем различные кодовые комбинации, : необходимые для проведения контроля, получаются при уравновешивании входного сигнала с различными длительно10 стями такта кодирования.

Известно, что для АЦП, построенного на основе неизбыточного двоичного кода, существует минимально возможная длительность такта пораз15 .рядного кодирования t ;„, при которой аналого-цифровое преобразование будет проводиться правильно. Величина t. - при условии, что выходной сигнал ЦАП устанавливается

20 по экспоненциальному закону, определяется соотношением

Чп,-.( + Ь

где € - постоянная времени ЦАП;

п - количество тактов поразрядного кодирования. Если длительность такта поразрядного кодирования будет меньше значения tj ;, то возможно, что

уравновешивание произойдет неверно вследствие появления ошибок уравновешивания типа неправильное включение разряда.

Для аналого-цифровых преобразователей содержащих в цепи обратной связи ЦАП построенный на основе избыточных измерительных кодов, вследствие наличия избыточности у последнего, появление ошибок кодирования типа неправильное включение разряда не вызовет недоуравно- вешивания входного сигнала Аg компенсирующим сигналом ЦАП А.

Дпя того, чтобы при аналого-цифровом преобразовании исключить

ошибку кодирования типа неправильное включение разряда в процессе уравновешивания А сигналом А вводят асимметрию, заключающуюся в том,

что на каждом if-M такте поразрядного кодирования одновременно с -м разрядом с весом 0,g включают группу некоторых младших разрядов, имеющих суммарный вес ЛО.доп Значение л Q.,on определяется по формуле 6-

.

1 0

На основании значений 1 синтезируется код Kg младших разрядов, который при изготовлении устройства заносится в блок постоян- ной памяти.

Если отношение между весами разрядов используемого кода является числом постоянным, то для формирования в процессе уравновешивания на каждом последующем J-M такте кодовой комбинации осуществляется сдвиг исходной кодовой

комбинации Кп на один разряд впра AoftВО.

Совместное включение 1-го и группы некоторых младших разрядов приводит к тому, что действующий вес 1-го разряда увеличивается. При этом, если разность , в конце предьщзпдего такта уравновешивания была близка к значению 1-го разряда, то в текущем такте блок сравнения сформирует логический нал, вызьюающий выключение 1-го разряда и дальнейшее уравновешивание ведется разрядами с номерами меньщими 1.

Таким образом, исключаются ошибки кодирования типа неправильное включение разряда.

При преобразовании входной аналоговой величины в код аналого-цифровым преобразователем, содержащим

ЦАП, построенный на основе неизбыточного двоичного кода, такая асиметрия процесса уравновешивания принципиально невозможна. В этом случае ошибка кодирования неправильное выключение разряда приведет к тому, что входную аналоговую-величину Aj нельзя будет уравновесить сигналом А с точностью до младшего разряда ЦАП. Поэтому результат преобразования Ag в цифровой эквивалент Kjb, будет неверньв. Если ЦАП аналого-цифрового преобразователя реализовать на основе избыточного измерительного кода, то появляется возможность осуществить правильное аналого-цифровое преобразование при ошибках кодирования типа неправильное выключение разряда. Введение же асииметрии в процесс уравновешивания позволяет исключить ошибки кодирования типа неправильное включение разряда.

Данные обстоятельства позволяют значительно уменьшить время каждо-

2233684

го J-ro- такта поразрядного кодирования . При этом на каждом такте урав- i новешивания нет необходимости осуществлять точное, например до полови- 5 ны младшего разряда, сравнение А и компенсирующего А аналоговых сигналов. Достаточно на один такт поразрядного уравновешивания отводить время, необходимое для установления О переходных процессов в ЦАП и блоке сравнения с погрешностью SQ . Значение SQ зависит от избыточности кода, на основании которого построен ЦАП, и опр еделяется по формуле

, .

где tf - отношение между соседними членами кода, на основании которого построен ЦАП.

20 Для чисел Фибоначчи при (oi 0,61803...) погрешность Q, выраженная в процентах, будет равна Q 23,6%..

Таким образом, построение ЦАП,

25 на основе ИИК и незначительное изме- Heitne алгоритма поразрядного кодирования позволяют прюизводить правильное аналого-цифровое преобразование при значительном уменьшении

30 длительности такта кодирования по отношению к номинальному значению. Данное обстоятельство используется для контроля аналого-цифрового преобразователя.

35 Работа устройства происходит в

режиме непосредственного преобразования входного сигнала в код в двух циклах. Причем длительность одного такта поразрядного кодирования в пер

40 вом цикле равна t, (t, ), а длительность одного такта поразрядного кодирования во втором цикле равна tjCtj tTj ;).

В первом цикле преобразование входной аналоговой величины в код происходит классическшч методом поразрядного ура виовеншвания с помощью блоков 2, 3, 4, 16, 6, 10 и 11, причем второй регистр 4 находится в нулевом состоянии в течение всего цикла кодирдвания.

Сравнение компенсирующего сигнала А и входного аналогового сигнала АИ производится при помои блока 2 сравнения, причем выходной сигнал Y: этого блока подчиняется следующему соотношению

т,,,ь

если А.„ А I.;

А ° . J

если Aft,A,j.

Процесс кодирования заканчивается на п-м такте поразрядного кодирования. При этом входной аналоговый сигнал Ag уравновешен компенсирующим сигналом ЦАП 3 с точностью до половины младшего разряда ЦАП 3 и на выходных информационных шинах 12 устройства появится код К(, являющийся цифровым эквивалентом входного аналогового сигнала Ag

На (п+1)-м такте происходит запись кода К, из первого регистра 26 во второй блок 9 развертки кода и по сигналу блока 10 управления управляемьш генератор 11 переменной частоты изменяет частоту задающих импульсов с ff. на f.

Во втором цикле на первом такте преобразования.входной аналоговой величины А ц в код Kg по сигналу . блока 10 управления устанавливается в единичное состояние (п-О-й разряд первого регистра 27 и во второй регистр 4 записывается кодовая комбинация Кдд, , которая поступает на первый блок 6 логических элементов ИЛИ. Затем кодовые комбинации через первый блок 6 логических элементов ИЛИ поступают на вход ЦАП 3, на выходе которого появится компен сирующий аналоговый сигнал А, Q n-i +0лоп, 1, где 0. п-1 - вес старшего разряда ЦАП.

Сравнение компенсирующего сигнал А |(, и входного аналогового сигнала А g производится при помош1и блока 2 сравнения.

На втором такте аналого-цифрового преобразования по сигналу блока 10 управления содержимое второго регистра 4 сдвигается на один разряд вправо, в результате чего на выходе второго регистра 4 появится кодовая комбинация Кдр„ , . Одновременн устанавливается в единичное состояние (п-2)-й разряд первого регистра 27. При этом на выходе ЦАП 3 появится компенсирующий сигнал А.

Работа устройства на любом j-м такте происходит аналогично. В первом регистре 27 устанавливается в единичное состояние (п-)-й разряд, содержимое второго регистра 4 сдвигается на один разряд вправо, в результате чего на выходе второго ре

233686

гистра 4 появится кодовая комбинация Кдд|,, , На выходе ЦАП 3 появится компенсирующий аналоговый сигнал Ац, который сравнивается с сигна- J лом А ЦК при помощи блока 2 сравнения. По сигналу У(п-)-й разряд либо остается в единичном состоянии либо устанавливается ,в ну(Y-1)

левое состояние (),

10 Процесс кодирования заканчивается на п-м такте поразрядного кодирования . При этом входной аналоговый сигнал А gj уравновешен компенсирующим сигналом А. ЦАП 3 с точно15 стью до половины младшего разряда и на выходных информационных шинах 12 устройства появится код К , являющийся цифровым эквивалентом входного аналогового сигнала А . На

20 (п+О-м такте происходит запись кода К из первого регистра 16 в пер- вьй блок 5 развертки кода.

Над содержимыми блоков 5 и 9 раз вертки кодов вьтолняется операция

25 вычитания. В формировании разности кодовых комбинаций участвуют первый блок 5 развертки кода, второй блок 9 развертки кода, второй блок 8 элементов И и блок 10 управления. Вы30 полнение операции вычитания производится путем развертки кодовых комбинаций в первом блоке 5 развертки кода и во втором блоке 9 развертки кода и установки в нулевое состоя25 ние совпадающих значащих разрядов кода, причем установка в нулевое состояние совпадающих разрядов производится после полной развертки кода. Указанный процесс происходит до подо явления нулевой кодовой комбинации хотя бы в одном из блоков развертки кода.Признаком появления нулевой кодо- Ч вой комбинации является отсутствие сигналов совпадения значащих разрядов

45 кода, поступающих с выхода второго блока 8 логических элементов И.

После выполнения операции вычитания содержимое одного из блоков 5 или 9 через второй блок 7 элементов

50 ИЛИ и первый блок 26 логических элементов И, при наличии разрешающего сигнала от блока 10 управления, поступает на контрольные выходные шины 13 устройства. Наличие ненулево55 вого кода на контрольном выходе 13 свидетельствует о наличии и величи- . не отклонений весов разрядов ЦАП от требуемых значений.

Блок 10 управления может быть синтезирован различными методами. Например, он может быть вьтолнен на основе автомата с памятью или по принципу программного управления.

Один из возможных вариантов реализации блока управления приведен на фиг. 2. Для формирования управляющих сигналов применена последовательная схема с использованием ПЗУ.

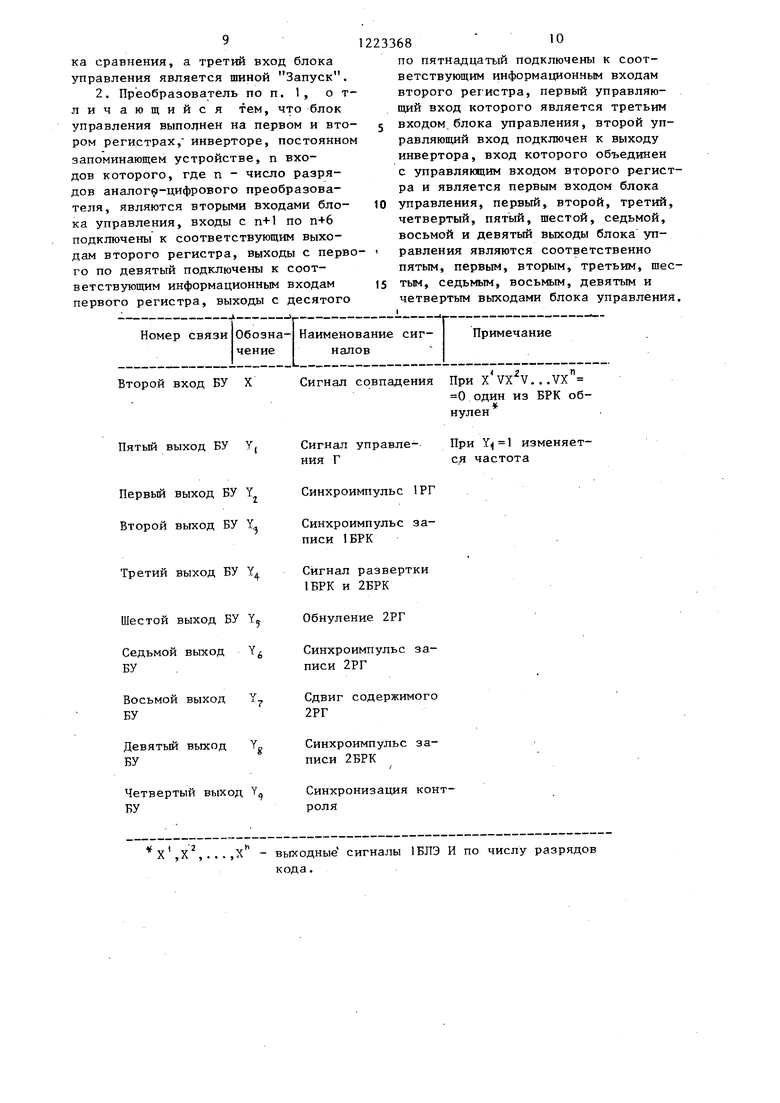

Необходимые для управления функционирования A1JJI управляющие и условные сигналы приведены в таблице

Алгоритм функционирования устройства в соответствии с вьшеприве- денным описанием работы для показан на фиг. 3 и 4.

Алгоритм состоит из вершин:

1.в.1-17 - обнуление 2РГ и уравновешивание входной аналоговой величины при t

2.

2.В.18 - изменение частоты Г с

f на fp в 2РГ переписывается из БШТ дополнительная кодовая комбинация и в 2БРК переписывается содержимое 1РГ;

3.в.19-35- происходит уравновешивание входной аналогово величины при t it- ,„„ ;

4.в.36 - в 1БРК переписывается

содержимое 1РГ;

5.в.37-39- вьтолняется операция вычитания путем установки в нулевое состояние совпадающих значащих разрядов кода;

6.в.40 - сигнал разрешения для

поступления информации на контрольный выход.

Формула из об р е т е н и

1. Аналого-цифровой преобразователь, содержащий блок сравнения, певый вход которого является входной щиной, второй вход подключен к выходу цифроаналогового преобразова- теля, блок управления, первый выход которого подключен к управл яющему входу первого регистра, выходы которого подключены к соответствующим первьм информационным входам первого блока развертки кодов, первый и второй управляющие входы которого под223368

ключены соответственно к второму к третьему выходам блока управления, четвертый выход которого подключен к первому входу первого блока элементов J И, выходы которого являются выходными контрольньв т шинами, отличающийся тем, что, с целью повьшения достоверности преобразования, в него введены первый и второй

0 блоки элементов ИЛИ, второй блок зле- ментов И, второй блок развертки кодов, второй регистр, блок постоянной памяти, генератор тактовых импульсов, вход которого подключен к пятому вы15 ходу блока управления, а выход - к первому входу блока управления, шестой, седьмой и восьмой выходы которого подключены соответственно к первому, второму и третьему управляющим

2Q входам второго регистра, информационные входы которого подключены к соответствующим выходам блока постоянной памяти, а выходы - к соответствующим первым входам первого блока

25 элементов ИЛИ, выходы которого подключены к соответствующим входам цифроаналогового преобразователя, вторые входы объединены с соответствующими первыми информационными входа- ми второго блока развертки кодов и подключены к соответствующим выходам первого регистра, которые являются выходными информационными шинами первый управляющий вход второго блока развертки кодов подключен к девя тому выходу блока управления, второй управляющий вход объединен с вторым управляющим входом первого блока развертки кодов, а вторые информационные входы объединены с соответствующими вторыми информационными входами первого блока развертки кодов, вторыми входами блока управления и подключены к соответствующим выходам второго блока элементов И, первые 5 входы которого объединены с соответствующими первыми входами второго блока элементов ИЛИ и подключены к соответствующим выходам первого блока развертки кодов, а вторые входы 0 объединены с соответствующими вторыми входами второго блока элементов ИЛИ и подключены к соответствующим выходам второго блока развертки кодов, выходы второго блока элементов 5 ИЛИ подключены к соответствующим вторым входам первого блока элементов И, при этом информационный вход первого регистра подключен к выходу бло30

0

у

ка сравнения, а третий вход блока управления является шиной Запуск.

2. Преобразователь по п. 1, отличающийся тем, что блок управления выполнен на первом и втором регистрах, инверторе, постоянном запоминающем устройстве, п входов которого, где п - число разрядов аналог9 цифрового преобразователя, являются вторыми входами блока управления, входы с п+1 по п+б подключены к соответствующим выходам второго регистра, выходы с первого по девятый подключены к соответствующим информационным входам первого регистра, выходы с десятого

Второй вход БУ X

Сигнал совпадения

Пятый выход БУ Y,

Сигнал управления Г

Первьй выход БУ Y Синхроимпульс 1РГ

выход БУ Y

выход БУ Y

Синхроимпульс записи 1БРК

Сигнал развертки 1БРК и 2БРК

Шестой выход БУ Y Обнуление 2РГ

выход Y

выход Y

выход Y

й выход Y

Синхроимпульс записи 2РГ

Сдвиг содержимого 2РГ

Синхроимпульс записи 2БРК

/

Синхронизация контроля

, . .. Д выходные сигналы 1БЛЭ И по числу разрядов кода.

23368 10

по пятнадцатый подключены к соответствующим информационным входам второго рег истра, первый управляющий вход которого является третьим

5 входом.блока управления, второй управляющий вход подключен к выходу инвертора, вход которого объединен с управляющим входом второго регистра и является первым входом блока

10 управления, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока уп равления являются соответственно пятым, первым, вторым, третьим, шес15 тым, седьмым, восьмым, девятым и четвертым вьтходами блока управления.

При ...vx

0 один из БРК обнулен

При Y 1 изменяется частота

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1288913A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Оно позволяет повысить достоверность преобразования за счет применения в аналого-цифровом преобразователе (АЦП) поразрядного кодирования избыточных измерительных кодов (ник). Построение циф- роанапогового преобразователя на основе ИИК, а также введение первого и второго блоков элементов ИЛИ, второго блока элементов И, второго блока развертки кодов, второго регистра, блока постоянной памяти и генератора тактовых импульсов позволяют проводить ускоренный метрологический самоконтроль АЦП, не ухудшая быстродействия АЦП в режиме преоб.- разования входного сигнала, что обеспечивает повышение достоверности преобразования. 2 з.п. ф-лы, 4 ил. (Л

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-07—Публикация

1984-08-01—Подача