(5) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU928632A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

1

Изобретение относится к вычислительной и цифровой измерительной технике и используется для преобразования аналоговых величин в цифровые.

Известен преобразователь напряжения в код с системой самоконтроля нуля, содержащий нуль-орган, преобразователь код-напряжение, регистр, ключи, триггеры, схемы И, ИЛИ, НЕ Cl

Недостатком данного устройства является ненадежность метрологического, контроля линейности выходной характеристики.

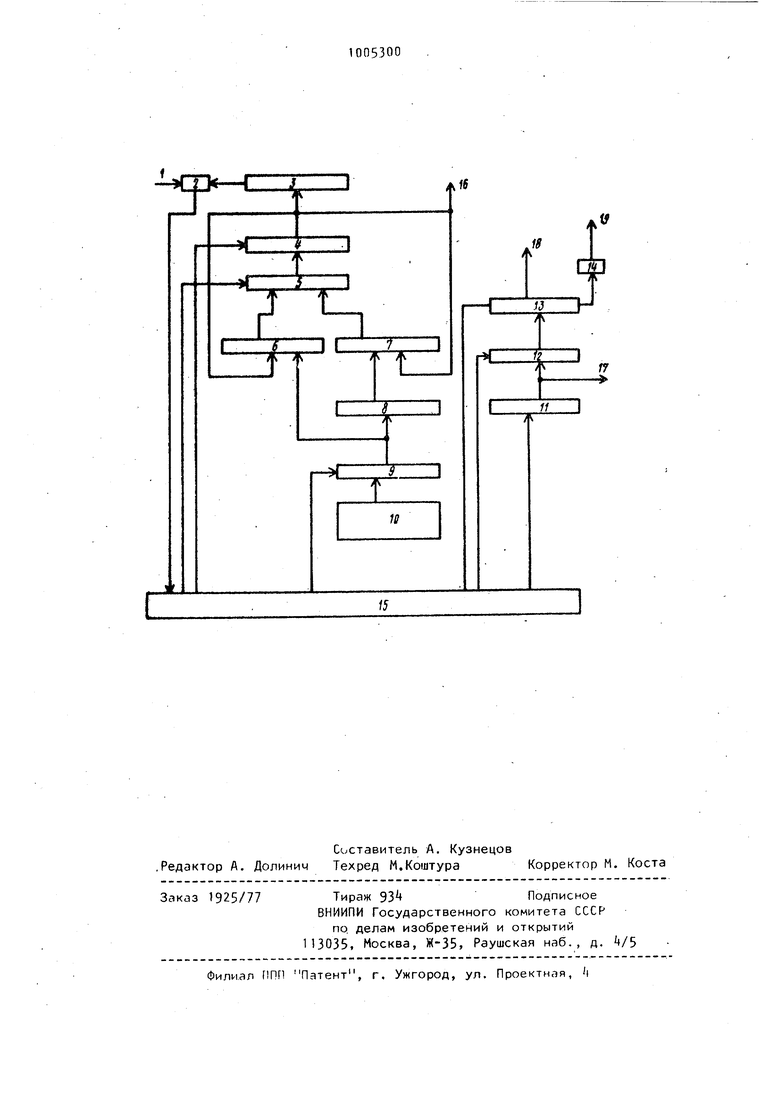

Известен аналого-цифровой преобразователь в кодах золотой пропорции , соде рх{а1ци и блок управления, цифро-аналоговый преобразователь, схему сравнения, блок развертки кода, блок элементов И по числу разрядов кода, блок элементов ИЛИ по числу разрядов кода, второй блок развертки кода, блок определения знака и блок приведения кода к минимальной форме, при-, чем первый вход схемы сравнения является входом аналого-цифрового пре-. образователя, второй вход схемы сравнения .соединен с выходом цифро-аналогового преобразователя, выход схемы сравнения соединен с первым входом блока управления, первый выход блока управления соединен с первым входом первого блока развертки кода, выход которого соединен со входом цифро-аналогового преобразователя, входом блока определения знака, первым входом блока элементов И, первым входом блока элементов ИЛИ и первым входом второго блока развертки кода, второй выход блока управления соеди5 нен со вторым входом второго блока развертки кода, выход которого соединен со вторым входом блока элементов ИЛИ и вторым входом блока элементов И, выход блока элементов И соединен с третьим входом второго блока развертки кода, вторым входом первого блока развертки кода и вторым входом блока управления, выход блока элементов ИЛИ соединен с информационным входом блока приведения кода к минимальной форме, третий выход блока управления соединен с управляющим входом блока приведения кода к мини.мальной форме, выход которого является первым выходом аналого-цифрового Преобразователя, выход блока определе ния знака является вторым выходом аналого-цифрового преобразователяС2 3. Недостатками такого аналого-цифрового преобразователя являются низкое по сравнению с двоичным преобразователем быстродействие в режиме, преобразования входной аналоговой величины в код золотой р-пропорции, а также необходимость специализированного вычислителя, функционирующего в кодах золотой р-пропор- . ции, для обработки результатов преобразования и метрологического контро ля. Цель изобретения - увеличение бы родействия аналого-цифрового преобразования и расширение функциональных возможностей аналого-цифрового преобразователя. Поставленная цель достигается те что в аналого-цифровой преобразователь, содержащий блок формирования знака, выход которого соединен с пе вой контрольной шиной, элемент срав нения, первый вход которого соедине с входной шиной аналого-цифрового преобразователя, второй вход - с выходом ц ифро,-а на лого во го преобразователя, а выход - со входом блока управления, первый выход которого со динен с первым входом блока развертк кода, выход которого соединен с входом цифро-аналогового преобразовател и первой информационной шиной, введены цифровой коммутатор, первый и второй сумматоры, первый и второй блок обращения кодов, накопительный сумматор, блок адресации, регистр и постоянное запоминающее устройство, выход .которого соединен с информационным входом блока адресации, управляющий вход которого соединен со вторым выходом блока управления, выход - с первым входом первого сумматора и входом первого блока обраще ния кодов, выход которого соединен с первым входом второго сумматора, вторые входы первого и второго сумматора соединены с выходом блока раз вертки кода, а выходы соединены соответственно с первым и вторым информационными входами цифрового коммутатора, управляющий вход которого соединен с третьим выходом блока управления, а выход - с информационным входом блока развертки кодов, при этом управляющий вход регистра соединен с четвертым выходом блока управления, а выход соединен со второй информационной шиной и с информационным входом второго блока обращения кодов, управляющий вход которого соединен с пятым выходом блока управления, а выход соединен с информационным входом накопительного сумматора, управляющий вход которого соединен с шестым выходом блока управления, первый выход - со второй контрольной шиной, а второй выход соединен со входом блока формирования знака. На чертеже представлена функциональная схема аналого-цифрового преобразователя. Схема содержит входную шину 1, элемент сравнения 2, цифроаналоговый преобразователь 3, блок развертки кодов k, цифровой коммутатор 5, первый сумматор 6, второй сумматор 7, первый блок обращения кодов 8, блок адресации9, постоянное запоминающее устройство 10, регистр 11, второй блок обращения кодов 12, накопительный сумматор 13 блок формирования знака , блок управления 15, первая информационная шина 16 аналого-цифрового преобразователя, с которой снимается цифровой эквивалент входной аналоговой величины в р-коде, вторая информационная шина 17 аналогоцифрового преобразователя, с которой снимается двоичный цифровой эквивалент входной аналоговой величины, первая и вторая контрольные выходные шины 18 и 19 аналого-цифрового преобразователя, на которых формируется соответственно величина и знак отклонения весов разрядов цифро-аналогового преобразователя 3 от номинальных значений. Входная шина 1 аналого-цифрового преобразователя, на которую подается преобразуемая аналоговая величина, соединена, с первым входом элемента сравнения 2, второй вход которого соединен с выходом цифро-аналогового преобразователя 3 вход которого соединен с первыми входами сумматоров 6. и 7 предназначенных для сложения чисел в р-кодах, и с выходом блока k предназначенного для выполнения операции развертки над р-кодами, и явля ется первым информационным выходом 16 аналого-цифрового преобразователя Выходы блока 6 и блока 7 соединены соответственно с первым и вторым информационными входами цифрового коммутатора 5 выход которого соединен с информационным входом блока . Выход постоянного запоминающего устройства 10, в котором хранятся двоич ные веса разрядов в р-крдах, соедине с информационным входом блока 9, осу ществляющего выборку информации на блоке 10. Выход блока Э соединен со вторым входом блока 6 и входом блока 8, необходимого для получения обратных р-кодов. Выход блока обращения кодов 8 соединен со вторым входом блока 7. Выход регистра 11, в котором формируется двоичный цифровой эквивалент входной аналоговой величины, является вторым информационным выходом 17 аналого-цифрового преобразователя и соединен с информационным входом блока 12, предназначенног для получения по команде блока уп- равления 15 обратных двоичных кодов. Выход блока 12 соедине с информационным входом двоичного накопительного сумматора 13, первый выход кото рого является первым контрольным выходом 18 аналого-цифрового преобразователя, а второй выход соединен со входом блока 1, формирующего знак результата вычитания. Выход блока И является вторым контрольным выходом 19 аналого-цифрового преобразователя Вход блока управления 15, обеспемивающего работу устройства, соединен с выходом элемента сравнения 2. Выходы с первого по шестой блока 15 соединены соответственно с управляющими входами блока 5, блока , блока 9, блока 13, блока 12 и блока 11. В аналого-цифровом преобразователе веса разрядов цифро-аналогового преобразователя пропорциональны весам разрядов кадов с иррациональными основаниями, к которым относятся коды золотой р-пропорции и коды Фибоначчи. Связь между весами разрядов р-кодов определяется реккурентным соотношением .g /Е-. Р где oLP - вес Е-го разряда; р .0,1,2,... Аналого-цифровой преобразователь работает в двух режимах: режиме поверки, в котором определяются коды огрешностей весов разрядов цифроналогового преобразователя 3, и в режиме непосредственного преобразования входной аналоговой величины А в двоичный код и р-код. в режиме преобразования устройство работает следующим образом. Входная аналоговая величина АХ со входа 1 поступает на первый вход элемента сравнения 2, на второй вход которого поступает компенсирующий аналоговый сигнал А, формирующийся на выходе цифрю-аналогового преобразователя 3. Разность указанных величин преобразуется в цифровой код по методу поразрядного уравновешивания, причем уравновешивание входной аналоговой величины Ау происходит по двоичному алгоритму, т.е. входная аналоговая величина АХ представляется в виде A,t EIan2. . г-0 где Эр - двоичная цифра в -м разряде;п 0,1,2,... На первом такте поразрядного уравновешивания в блок развертки кодов Ц, -который в данном случае выполняет функции регистра, и на первые входы комбинационных сумматоров 6 и 7 по команде из блока управления 15 поступает т-разрядная кодовая комбинация в коде золотой р-пропорции или р-коде Фибоначчи, соответствующая старшему двоичному весу 2 . Одновременно по команде блока управления 15 блок адресации 9 производит выборку из постоянного запоминающего устройства 10 т-разрядного р-кода, соответствующего более младшему двоичному весу , и подает его на второй вход комбинационного сумматора 6 и на вход блока 8, на выходе которого формируется обратный р-код, который затем поступает ла второй вход комбинационного сумматора 7. Таким образом, на первом такте аналого-цифрового преобразования входная аналоговая величина Ajj сравнивается . с весом 2. В этом же такте на выходе комбинационного сумматора 6 формируется р-код, соответствующий сумме двоичных весов , а на выходе вычитателя, образованного блоками 8 и 7, формируется р-код, соответствующий разности двоичных весов 2 2. По результату срабатывания эле мента сравнения 2 блок управления 15 через цифровой коммутатор 5 в сле дующий такт поразрядного сравнения подключает на вход блока выход сумматора 6 (если ) или выход блока 7 (если ((). Одновременно блок 9 производит выборку из блока 10 цифрового эквивалента веса 2 в р-коде и подает его на вход сумматора 6 и вычитателя (блоки 8 и 7), на выходе которых формируется соответственно сумма и разность содержимого блока k и цифрового эквивалента веса 2 в р-коде. В процессе уравновешивания- входной аналоговой величины А в блоке 4 за п тактов сформируется ее т-разрядный цифровой эквивалент в коде золотой р-пропорции или р-коде Фибоначчи. Одновременно в регистре 1 за п тактов преобразования будет сформирован- п-разрядный двоичный циф ровой эквивалент входной аналоговой величины Aj( известным способом. Режим поверки заключается в определении величин отклонений весов разрядов цифро-аналогового преобразователя 3 от требуемых значений при условии, что (р+1) младших разрядов преобразователя точные. В этом режиме на вход аналого-цифрового преобразователя поступает ступенчатонарастающий аналоговый сигнал, i-я ступень которого используется для поверки i-ro разряда цифро-аналогового преобразователя 3. Процесс поверки любого разряда со стоит из двух этапов. На первом этап производится преобразование i-й ступени в т-разрядный р-код и п-разрядный двоичный код описанным выше способом. По команде из блока управлени 15 п-разрядный двоичный код записывается из регистра 11 в накопительны сумматор 13. На втором этапе происходит повтор ное кодирование величины i-й ступени но при этом блок управления 15 запре щает включение i-ro поверяемого разр да цифро-аналогового преобразователя 3 путем выполнения операции разверт ки в блоке k. В результате кодирования в блоке и блоке 11 сформируютс .соответственно т-разрядный р-код и П-разрядный двоичный код, соответствующие входной аналоговой величине и .не включающие погрешности i-ro Поверяемого разряда. По команде из блока управления происходит вычитание двоичных цифровых эквивалентов входной ана,логовой величины, полученных на первом и втором этапах поверки с помощью блока обращения ксэдов 12, накопительного сумматора 13 и блока формирования знака l. В результате вычитания в блоке 13 сформируется двоичный код величины отклонения 1-го разряда цифро-аналогового преобразователя 3 от требуемого значения, а в блоке 1 - знак погрешности I-го разряда, причем величина отрицательной расстройки будет представлена в обратном двоичном коде. Введение новых блоков и связей позволяет повысить быстродействие аналого-цифрового преобразования по К JnlEl сравнению с прототипом 8одоо р где т(р) - число разрядов в р-коде.; п - число двоичных разрядов при одинаковом диапазоне представленных чисел; dp - основание системы счисления р-кодов и является действительным положитель. ным корнем уравнения Х Ь и расширить функциональные возможности формирования двоичных цифровых эквивалентов входной ве.гн1чины и погрешностей преобразования. При этом наличие двоичного выхода в аналого-цифровом- преобразователе позволяет широко использовать стандартные двоичные вычислители на элементах средней степени интеграции, а также микропроцессорную элементную базу для обработки результатов метрологического контроля и цифровой коррекции. Формула изобретения Аналого-цифровой. преобразователь, содержащий блок формирования знака, выход которого соединен с первой контрольной шиной, элемент .сравнения, первый вход которого соединен с входной шиной аналого-цифрового преобразователя, второй вход - с выходом цифро-анаяогового преобразователя, а выход - с входом блока управления, первый выход KOToporQ соединен с первым входом блока развертки кода, выход которого соединен с вхо/: ом цифроаналогового преобразователя к первой информационной шиной, отличающийся тем, что, с целью увеличения быстродействия и расширения функциональных возможностей, в него введены цифровой коммутатор, первый и второй блоки обращения кодов, накопительный сумматор, блок адресаций, регистр и постоянное за помин аклчее устройство, выход которого соединен с информационным входом блока адресации, управляющий вход которого соединен с вторым выходом блока управления , а выход - с первым входом первого сумматора и входом первого блока обращения кодов,выход которого сое.динен с первым входом второго сумматора, вторые входы первого и второго сумматоров соединены с выходом блока развертки кода, а их выходы соединены соответственно с первым и вторым информационными входами цифрового коммутатора, управляющий вход которого соединен с третьим выходом блока управления, а выход - с информационным входом блока развертки кодов, при этом управляющий вход регисра соединен с четвертым выходом блока управления, а выход соединен с второй информационной шиной и с информационным входом второго блока обращения кодов, управляющий вход которого соединен с пятым выходом блока управлений, а выход соединен с информационным входом накопительного сумматора, управляющий вход которого соединен с шестым выходом блока управления, первый выход - с второй контрольной шиной, а второй выход - с входом блока формирования знака.

Источники информации, .принятые во внимание при экспертизе

кл. Н 03 К 13/02, 1979 (прототип).

Авторы

Даты

1983-03-15—Публикация

1981-07-27—Подача