1

Изобретение относится к импульсной технике, и в частности, может быть использовано в ТТЛ-интегральных микросхемах.

Цель изобретения - повышение поме хоустойчивости и быстродействия ТТЛ- элемента.

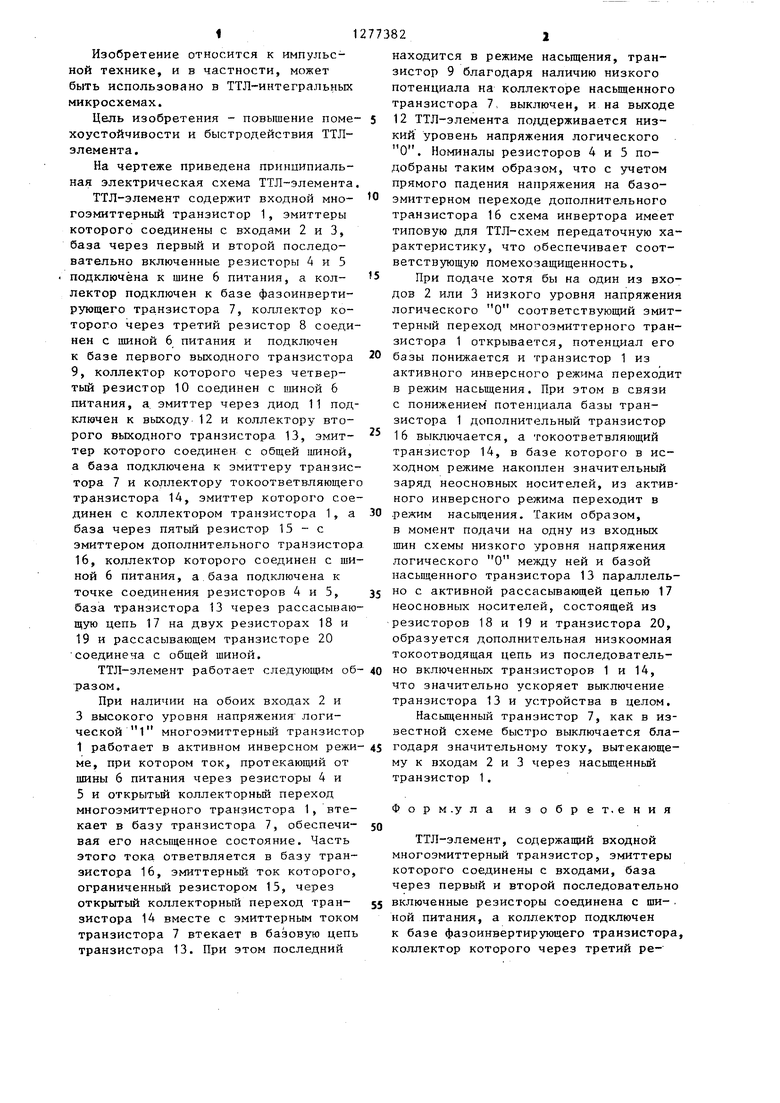

На чертеже приведена принципиальная электрическая схема ТТЛ-элемента

ТТЛ-элемент содержит входной мно- гоэмиттерный транзистор 1, эмиттеры которого соединены с входами 2 и 3, база через первый и второй последовательно включенные резисторы 4 и 5 подключена к шине 6 питания, а коллектор подключен к базе фазоинверти- рующего тра.нзистора 7, коллектор которого через третий резистор 8 соединен с шиной 6 питания и подключен к базе первого выходного транзистора 9, коллектор которого через четвертый резистор 10 соединен с шиной 6

питания, а. эмиттер через диод 11 подключен к выходу 12 и коллектору второго выходного транзистора 13, эмиттер которого соединен с общей цгиной, а база подключена к эмиттеру транзистора 7 и коллектору токоответвхшющего транзистора 14, эмиттер которого соединен с коллектором транзистора 1, а база через пятый резистор 15 - с эмиттером дополнительного транзистора 16, коллектор которого соединен с шиной 6 питания, а база подключена к точке соединения резисторов 4 и 5, база транзистора 13 через рассасывающую цепь 17 на двух резисторах 18 и 19 и рассасывающем транзисторе 20 соединена с общей шиной.

ТТЛ-элемент работает следуюцщм образом.

При наличии на обоих входах 2 и 3 высокого уровня напряжения логической 1 многоэмиттерньй транзистор

1 работает в активном инверсном режи- 45 годаря значительному току, вытекающеме, при котором ток, протекаю1ции от шины 6 питания через резисторы 4 и 5 и открытый коллекторный переход многоэмиттерного транзистора 1, втекает в базу транзистора 7, обеспечивая его насыщенное состояние. Часть этого тока ответвляется в базу транзистора 16, эмиттерный ток которого, ограниченньй резистором 15, через открытый коллекторный переход транзистора 14 вместе с эмиттерным током транзистора 7 втекает в базовую цепь транзистора 13. При этом последний

находится в режиме насыщения, транзистор 9 благодаря наличию низкого потенциала на коллекторе насыщенного транзистора 7. выключен, и на выходе 12 ТТЛ-элемента поддерживается низкий уровень напряжения логического О. Номиналы резисторов 4 и 5 подобраны таким образом, что с учетом прямого падения напряжения на базо- эмиттерном переходе дополнительного транзистора 16 схема инвертора имеет типовую для ТТЛ-схем передаточную характеристику, что обеспечивает соответствующую помехозащищенность.

При подаче хотя бы на один из входов 2 или 3 низкого уровня напряжения логического О соответствующий эмит- терный переход многоэмиттерного транзистора 1 открывается, потендиал его базы понижается и транзистор 1 из активного инверсного режима переходит в режим насьш ения. При этом в связи с понижением потенциала базы транзистора 1 дополнительный транзистор

16 выключается, а токоответвляющий транзистор 14, в базе которого в исходном режиме накоплен значительный заряд неосновных носителей, из активного инверсного режима переходит в

режим насыщения. Таким образом, в момент подачи на одну из входных шин схемы низкого уровня напряжения логического О ней и базой HacbmjeHHoro транзистора 13 параллельно с активной рассасьшающей цепью 17 неосновных носителей, состоящей из резисторов 18 и 19 и транзистора 20, образуется дополнительная низкоомная токоотводящая цепь из последовательно включенных транзисторов 1 и 14, что значительно ускоряет выключение транзистора 13 и устройства в целом.

Насыщенный транзистор 7, как в известной схеме быстро выключается бламу к входам 2 транзистор 1.

и 3 через нacьш eнный

Форм.ула изобрет.ения

ТТЛ-элемент, содержащий входной многоэмиттерный транзистор, эмиттеры которого соединены с входами, база через первый и второй последовательно включенные резисторы соединена с ши-. ной питания, а коллектор подключен к базе фазоинвертирующего транзистора, коллектор которого через третий ре-

312773824

зистор соединен с шиной питания игоэмиттерного транзистора, а коллекподключен к базе первого выходноготор подключен к эмиттеру фазоинвертитранзистора, коллектор которого черезрующего транзистора и базе второго

четвертый резистор соединен с пшнойвыходного транзистора, о т л и ч апитания, а эмиттер через диод подклю- 5ю щ и и с я тем, что, с целью повычен к выходу и коллектору второго вы-шения помехоустойчивости и быстродейходного транзистора, эмиттер которогоствия, в него введен дополнительный

соединен с общей шиной и через рас-транзистор, коллектор которого соедисасывающую цепь с его базой, база то-нен с шиной питания, база подключена

коответвляющего транзистора соединена 10к точке соединения первого и второго

с первым выводом пятого резистора,резисторов, а эмиттер - к второму

эмиттер - с коллектором входного мно-вьгооду пятого резистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТТЛ-инвертор | 1981 |

|

SU1035802A1 |

| Входной каскад транзисторно-транзисторной логической схемы | 1979 |

|

SU1012764A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Троичный триггер на ТТЛ-инверторах | 1989 |

|

SU1727197A1 |

Изобретение относится к импульсной технике и может быть использовано в ТТЛ-интегральных микросхемах. Цель изобретения - повышение помехоустойчивости и быстродействия устройства. Для достижения поставленной цели- в устройстве введен дополнительньй транзистор 16, коллектор которого- соединен с шиной 6 питания, база подключена к точке соединения первого и второго резисторов 4,5, а эмиттер - к второму выводу пятого резистора 15, Кроме того, устройство содержит транзисторы 1,7,13,14,20, резисторы 8, 10,18,19, входы 2,3, выход 12, диод 11. Техническими преимуществами предложенного устройства являются получение уровня помехоустойчивости, соответствующего типовым значениям ТТЛ- элементов, и более высокое быстродействие по времени задержки выключения схемы. 1 ил. с (Л Ь9 СО 00 ю

| Букреев И.П | |||

| и др | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU314307A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-15—Публикация

1985-07-30—Подача