кВЫХОДУ первого дешифратора нуля и второму информационному входу блока элементов И, выход которого нодклю-: чем к второму входу сумматора, выход второго дешифратора нуля подключен к управляющему входу первого коммутатора , вторая группа информационных входов которого подключена к выходу сумматора, а выход подключен к информaциoинo ry входу регистра результата, первый выход генератора тактовых импульсов соединен с тактовым входом триггера и первым входом первого элемента И, второй выход генератора такт кьг:- импульсов подключен к первым входам второго и четверто1о элементов И, прямой выход триггера подключен к вторым входам первого, четвертого элементов И и входам синхронизации регистров номера функции и тра текущих значений аргумеита, прямой и инперсньй энакс,вые выходы блока вьгчитапия подключены к третьим вхо-. дам соответственно первого и четвертого элементов И, выход первого элемента И подключен к счетному входу счетчика номеров участков, выходы Больше и Равно блока сравнения подключены соответственно к второму ВХОДУ второго элемента И и первому входу третьего элемента И, соединенного с четвертым входом четвертого элемента И, выход которого соединен входом синхронизации регистра приращения аргумента, регистра номера участка, регистра степени полинома, регистра номера функции, счетчика степени полинома, первому входу элемента ИЛИ и входу сброса триггера, выход второго элемента И подключен к счетному входу счетчика степени полинома и второму входу элемента ИЛИ, выход которого через элемент задержки подключен к входу синхронизации , буферного регистра и к второму входу третьего элемента И, выход которого подключен к входу синхронизации регистра результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Многофункциональный преобразователь | 1986 |

|

SU1429128A1 |

| Многофункциональный преобразователь | 1986 |

|

SU1401479A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1374218A2 |

| Аналого-цифровой функциональный преобразователь | 1988 |

|

SU1508249A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Функциональный преобразователь | 1979 |

|

SU842852A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ФУНКЦИЙ, содержащее счетчик номеров участков, соединенш 1й выходом с информационным входом регистра номера участка и с первой группой адресных входов первого блока памяти, выход . кода узловых значений аргумента которого подключен к вычитающему входу блока вычитания, подключенному выходом разности к информационному входу регистра приращенчй аргумента, выход счетчика степени полинома подключен к первому входу блока сравнения и первой группе адресных входов второго блока памяти, подключенного второй группой адресных входов к выходу регистра номера участка, выход блока умножения подключен к первому входу сумматора, выход которого подключен к информационному входу буферного регистра, элемент задержки, генератор тактовых импульсов, единичный вход триггера является входом запуска устройства, выход регистра результата является выходом устройства, о.т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в него введены первый и второй регистры номера функции, регистр текущих значений аргумента, регистр степени полинома, третий блок памяти, два дешифратора нуля, два коммутатора, группа элементов И, четыре элемента И и элемент ИЛИ, информационные входы регистра тек5шщх значений аргумента и первого регистра номера функции являются соответственно первым и вторым информационными входами устдойства, выход .регистра текущих значений аргумента подключен к суммирующему входу блока вычитания и к первой группе адресных входов третьего блока памяти, вторая группа адресных i входов которого подключена к выходу первого регистра номера функции, ин(Л формационному входу второго регистра номера функции и второй группе адресных входов первого блока памяти, сое-, диненного выходом кода степени полинома с информационным входом регистра степени полинома, выход которого подключен к второму входу блока срав00 нения и входу первого дешифратора ную ля, выход второго регистра номера О1 функции подключен к третьей группе 00 адресных входов второго блока памяти, о выход кода коэффициен1 ов которого подключен к первым группам информационных входов первого и второго коммутаторов и к первому входу блока эле- . ментов И, выход второго коммутатора подключен к первому входу блока умножения, соединенного вторым входом с выходом регистра приращений аргумента, а выходом - с информационным входом буферного регистра, подключенного выходом к второй группе информационных входов второго коммутатора, управляющий вход которого подключен

1

Изобретение относится к автоматике и вычислительной технике, в частности к полиномиальньц сплайн-аппроксиматорам, и может быть использовано в автоматизированных системах управления при воспроизведении широкого класса функциональных зависимостей независимого аргумента.

Цель изобретения - повьш1ение быстродействия устройства.

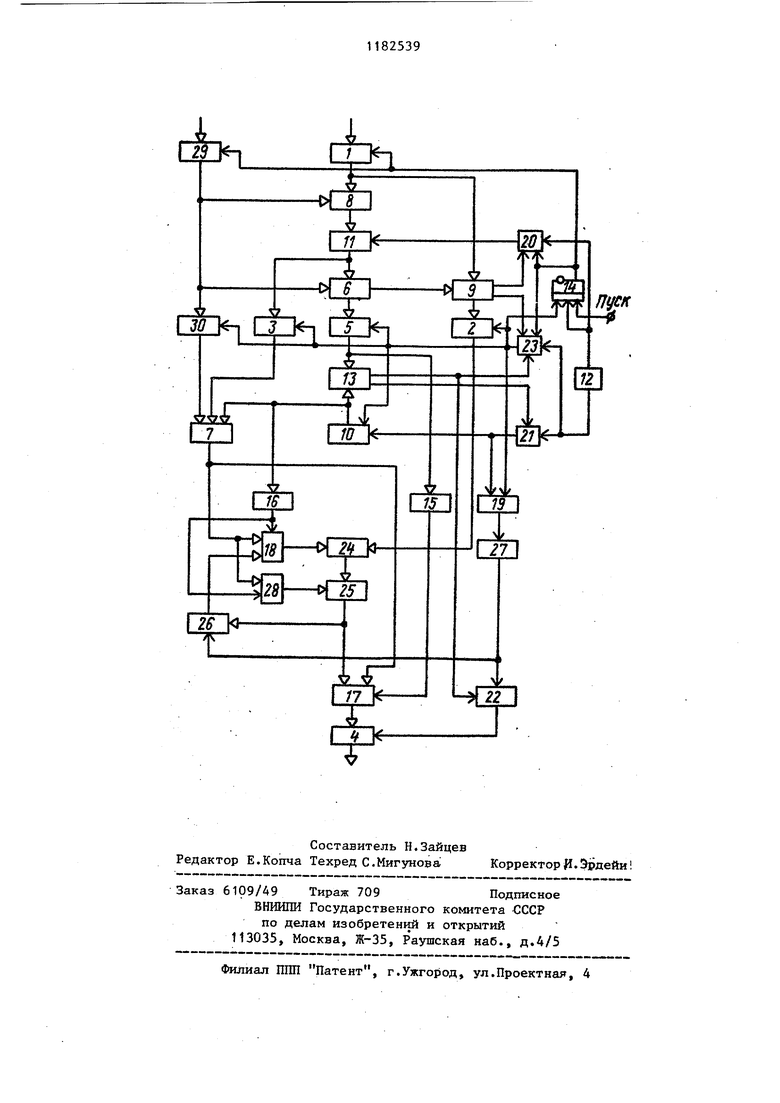

На чертеже изображена функциональнгш схема устройства для воспроизведения функций.

Устройство для воспроизведения функций содержит регистр 1 текущих значений аргумента, регистр 2 приращений аргумента, регистр-3 степени полинома, регистр 4 результата, регистр 5 номера участка,три блока 6-8 памяти, блок 9 вычитания, счетчик 10 степени полинома, счетчик 11 номеров участков, генератор 12 тактовых импульсов, блок 13 сравнения, триггер 14, два дешифратора 15 и 16 нуля, два коммутатора 17 и 18,

элемент ИЛИ 19, четыре элемента И 20-23, блок 24 умножения, сумматор 25, буферный регистр 26, элемент 27 задержки, блок 28 элементов И, пер5 вьй 29 и второй 30 регистры номера функций.

Принцип действия устройства для воспроизведения функций основдн на кусочно-полиномиальной сплайн-аппроксимации воспроизводимых функций при произвольном характере разбиения на участки аппроксимации и задания степени полинома на каждом из участков аппроксимации.

Устройство работает следующимобразом.

В исходном состоянии обнулены регистры 1-5, а также регистры 29 и 30, счетчики 10 и 11 и триггер 14 (цепи приведения в исходное состояние на блок-схеме не изображены). В блок. 6 памяти записаны коды узловых значений абсцисс х,-.- воспроизво димых функций , (х) и ст-зпеней га,, аппроксимирунжщх полиномов (где j номер воспроизводимой функцииj i номер участка аппроксимации). В блок 7 памдти записаны коды коэффициентов А g аппроксимации (,т..), а в блок 8 памяти - коды i; предва рительной установки адресов счетчика 1 1 . Работа устройства начинается пода чей пускового напряжения на единичный вход триггера 14 После прихода на тактирующий вход триггера 14 импульса с первого выхода генератора 1 триггер переключается в единичное состояние (триггер 14 переключается задним фронтом тактового импульса ) . Сигнал с выхода триггера 14 поступае на управляющие входы регистров 1 и 29,первый вход элемента И 20 и третий вход элемента И 23. В регистры 1 и 29 заносятся коды текущих значений аргумента х и номера j воспроизводимой функции. Код аргумента с выхода регистра 1 поступает на первый (суммирующий) вход блока 9 вычитания. В соответствиис кодом старших разрядов аргумента и кодом номера функции, поступающими на адресные вх ды блока 8 памяти, из блока памяти в счетчик 11 считывается код i - Этот код COOT варительнои установки ветствует номеру участка аппроксимаЦИК, узловое значение абсциссы которого является наибольшим из всех узловых значений абсцисс, для которы выполняется неравенство х..х, где хJ - текущее значение аргумента в младших разрядах которого записаны единицы (узловые значения абсцисс за писаны в блок 6 памяти упорядоченно по возрастающей последовательности). В соответствии с кодами, поступающими на адресные входы блока 6, на его выходы считываются параметры аппроксимации для i -го участка. В блоке 9 формируется разность между текущим значением аргумента и узловым значением абсциссы с первого выхода блока 6 пам}5ТИ.Если эта разность (х-х-отрицательна, то на прямом выходе знакового разряда блока 9 вычитания появляется единичный сигнал, отпирающий элемент И 20. Тактовые импульсы с первого выхода генератора 12 начинают поступать на счетньй (вычитающий) вход счетчика 11 и осуществлят. 55

последовательную выборку из блока 6 памяти узловых значений абсцисс и степеней полиномов. После того, как

11825394

с первого выхода Гхпока 6 памяти и блок 9 вычитания поступит код узловой пред2,3,5 и 30 будет дано только после завершения процедуры вычисления текзгщего значения функции. абсциссы х- текущего участка аппроксимации, для которого X е х j , i+,j) на прямом выходе знакового разряда блока 9 появится нулевой сигнал, запирающий элемент И 20. Одновременно с этим единичньй сигнал с инверсного выхода знакового разряда блока 9 (единица на инверсном выходе формируется при положительных и нулевых значениях разности) поступает на четвертый вход элемента И 23. Поскольку на первом и третьем входах элемента И 23 присутствуют единичные сигналы с выхода Равно блока 13 и выхода триггера 14, то тактовый импульс с второго выхода генератора 12 (генератор вырабатывает две синхронизированные друг с другом последовательности тактовых импульсов с частотами следования и fjjj, , для которых выполняется соотношение где ,2,3...) пройдет на выход элемента И 23. Выходной импульс элемента И 23 поступает на управляющие входы регистров 2,3,5,30 и счетчика 10, первьш вход элемента ИЛИ 19 и вход принудительного обнуления триггера 14 (R -типа с тактируемым S входом). При этом в регистры 2,3,5 и 30 будут записаны коды (х-х-,), т-:, i и j соответственно, подтвердится нулевое состояние счетчика 10, и задним фронтом импульса с выхода элемента И 23 триггер установится в нулевое состояние. Если устройство работает в режиме асинхронного обмена (на единичньй вход триггера 14 пусковое напряжение подается непрерывно), то после обнуления триггера 14 и появления на выходе элемента И 23 нулевого сигнала триггер 14 под воздействием очередного тактового импульса с первого выхода генератора, 14 вновь перейдет в единичное состояние, разрешая считывание новых значений кода аргумента и номера функции и определение соответствующих параметров аппроксимадии. Однако разрешение на считывание новых кодов приращения аргумента, .степени полинома, номера участка и номера функции в регистры

Вычисление текущего значения функции осуществляется следующим образом.

Если на данном участке аппроксимации функция воспроизводится полиномом нулевой степени y A jJ, то с второго выхода блока 6 памяти в регистр 5 будет записан нулевой код. При этом выходным сигналом дешифратора 15 нуля (вьтолненного, например, на элементе 11ПИ) коммутатор 17 под-. ключит информационньй вход регистра 4 к выходу блока 7 памяти, элемент И 22 будет открыт сигналом с выхода. Равно блока 13 сравнения, а элемент И 21 будет закрыт сигналом с выхода Больше блока 13. Выходной импульс элемента И 23, поступивший на первый вход элемента ИЛИ 19, после задержки элементом 18 проходит через элемент И 22 на управляющий вход регистра 4. В результате в ре- гистр 4 записьшается текущее значение функции, равное коэффициенту ЛУ, поступающему с выхода блока 7 памяти.

Если же на данном участке аппроксимации функция воспроизводится полиномом степени , то в регистре 5 будет записано ненулевое значение кода степени. Поэтому выходным сигналом дешифратора 15 коммутатор 17 подклю чит информационньй вход регистра 4 . к выходу сумматора 25. Единичным сигналом с выхода Больше и нулевым сигналом с выхода Равно блока 13 сравнения будет открыт элемент И 21 и закрыт элемент И 22 соответственно. Импульс, поступивший с выхода элемента И 23 на первый вход элемента ИЛИ 19проходит элемент ИЛИ 19 и элемент 27 задержки и поступает на вход синхронизации буферного регистра 26.

В начальньй момент времени при нулевом состоянии счетчика .10 выходной сигнал дешифратора 16 нуля запирает блок 28 элементов И и подключает первьй вход блока 24 умножения через коммутатор 18 к выходу блока 7 памяти. На выходе блока 24 умножения и соответственно на выходе сумматора 25

устанавливается код, равный произведению приращения (х-х-- ) с выхода регистра 2 на значение старшего коэффициента аппроксимации с выхода блока 7 памяти. Этот код записываетс по заднему фронту тактирующего импульса в регистр 26.

Далее при наличии единичного сигнала на выходе Больше блока 13 сравнения на выход элемента И 21 начинают поступать тактовые импульсы с второго выхода генератора ,12. Импульсы с выхода элемента И 21 поступают на счетньй (суммирующий) вход счетчика 10 и второй вход элемента ИЛИ 19 Первый из этих импульсов изменяет состояние счетчика. -10, в результате изменяется состояние выходного сигнала дешифратора 16. Первый вход блока

24умножения подключается к выходу регистра 26, а первый вход сумматора

25- к выходу блока 7 памяти. Код регистра 26 умножаете в блоке 24 ни код приращения аргумента регистра 2, полученное произведение суммируется в сумматоре.25 с кодом следующего значения А коэффициента аппроксима ции блока 7 памяти и записывается в регистр 26 по заднему фронту импульса с выхода элемента 27 задержки. Указанные действия продолжаются до ;Тех nopt пока значения кодов регистра 5 и счетчика 10 не станут равными друг другу. В этом случае состояния выходов блока 13 сравнения кодов изменяются на противоположные. Элемент И 21 запирается нулевым сигналом с выхода Больше блока 13, а единичньй сигнал с выхода Равно блока 13 подает на первьй вход эле мента И 23 разрешение на начало нового цикла вычислений и отпирает элемент И 22. Тактирующий импульс с выхода элемента 27 задержки проходит через элемент И 22 на «управляющий вход выходного регистра 4, записывая

в него выходной ко; сумматора 2:5, равный у(....,. (Ao iJx+A,) лх+... ). л х+АЙ/, где j .

.j,

ntffK

| Генератор функций хаара | 1979 |

|

SU783778A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор функций Хаара | 1980 |

|

SU947847A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1985-09-30—Публикация

1984-04-25—Подача