1

Изобретение относится к области вычислительной техники и может быть использовано при разработке быстродействукицих устройств для умножения чисел в любой позиционной системе счисления, удобных для изготовления в составе больших интегральных схем (БИС).

Известно устройство для умножения чисел 1}, содержащее регистры множимого и множителя, сумматор частичных произведений, цепи сдвига на оДин разряд в регистре множителя и в сулалаторе частичных произведений, блок управления, выходы которого соединены с ynpasiляющими входами сумматора частичных произведений, регистров множимого и множителя.

Недостатком известного устройства является его низкое быстродействие, так как в каждом такте работы устройства обрабатывается только одна двоичная цифра (разряд) множителя .

Наиболее близким к изобретению аналогом является устройство,для умножения, содержащее регистры мно1Жимого и множителя, накапливающий

2

сумматор, п одноразрядных узлов умножения (п - разрядность множимого) , п-разрядный комбинационный сумматор и блок управления, причем входы одноразрядных узлов умножения соединены с выходами соответствующих разрядов регистра 1«шожимого и с выходом первого разряда регистра множителя, а выходы

10 соединены со входами комбинационного сумматора, выходы которого подключены ко входам накапливающего cyNwaTOpa, а выходы блока управления подключены к управляющим

15 входам регистров множимого и множителя и накапливающего сумматора U:.

Это устройство может производит 20 перемножение двух чисел в любой

системе счисления с основанием N 72. ОсобЬ1й интерес представляет умножение чисел в двоичнокодированной . системе с основанием , где 25 каждь) разряд операнда представля, ется совокупностью k двоичных разрядов.

Недостатком этого устройства является недостаточное быстродействие, определяемое, в частности.

быстродействием n-разрядного комбинационного сумматора.

Целью изобретения является повышение быстродействия.

Для достижения поставленной цели устройство для умножения, содержащее регистры множимого и множителя, накапливающий сумматор, n одноразрядных узлов умножения (п-разрядность множимого), n одноразрядных сумматоров и блок управления, выходы которого соединены с управляющими входами регистров и накапливающего сумматора, первый вход каждого одноразрядного узла умножения соединен с выходом соответствующего разряда регистра множимого, а второй вход - с выходом первого разряда регистра множителя, первый выход i-ro одноразрядного узла умножения (,..., n) соединен с первым входом соответствующего одноразрядного сумматора, второй вход которого подключен ко второму выходу (1+1)-го одноразрядного узла умножения, второй выход первого одноразрядного узла умножения соединен со входом младшего разряда накапливающего сумматора, входы остальных разрядов которого подключены к выходам одноразрядных сумматоров, содержит n узлов запоминания переноса, вход каждого из которых подключен к выходу переноса соответствующего одноразрядного сумматора, а выход - со входом переноса этого же одноразрядного сумматора, управляющие входы узлов запоминания переноса соединены с одним из выходов блока управления.

На чертеже приведена структурная схема быстродействующего устройства для умножения чисел.

Числа представленыв в двоичнокодированной системе счисления с основанием N 2, т.е. каждый разряд множимого и множителя закодирован с помощью k двоичных разрядов.

Устройство содержит т-разрядные двоичные регистры 1, 2 соот етственно множимого и множителя (где (m-fk)-разрядный накапливакиций сумматор 3, цепи однотактного сдвига на k разрядов в регистре 2 и в сумматоре 3 (на чертеже не показаны), блок 4 управления, выходы которого соединены с управлякяцими -входами накапливаквдего сумматора 3 произведений, регистров 1, 2 соответствено множимого и множителя, n узлов одноразрядного умножения 5 (k-разрядного двоичного умножения), n одноразрядных сумматоров 6 (в данном случае - k-разрядных двоичных сумматоров) , причем первый вход 1-го узла умножения 5 (,. ..,п) соединен с шиной 7 значения k младших двоичных разрядов регистра множител 2, второй вход соединен с шиной 8 зчения соответствующих k двоичных рарядов регистра множимого 1, а его вход 9 значения k старших двоичных разрядов произведения соединен с первым входом соответствующего сумматора 6, второй вход которого

соединен с выходом 10 значения k младших двоичных разрядов произведения (i+l)-ro узла умножения 5, а вход переноса соединен с выходом i-ro узла запоминания переноса 11, вход которого соединен с выходом

12значения переноса сумматора 6, а управляющий вход соединен с выходом блока управления 4, выход

13значения суммц сумматора б со.единен с соответствующим входом накапливающего сумматора 3, младший вход которого соединен с выходом 10 значения k младших двоичных разрядов произведения первого узла умножения 5.

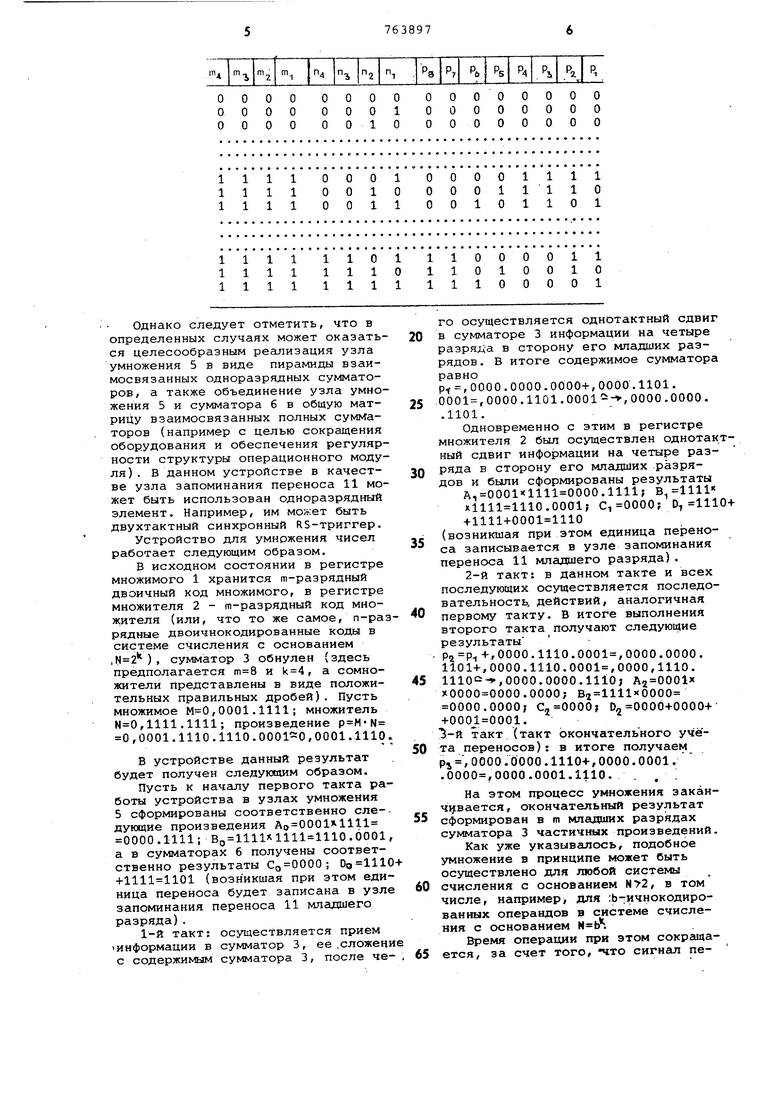

В данном устройстве регистр множимого 1 может быть реализован на RS-триггерах, регистр множителя 2 - на D-триггерах, накапливающий сумматор 3 - на D- либо IК-триггерах с блоком ускоренного образования разрядных переносов, блок управления 4 - в виде управляющего автомата. Узел умножения 5 выполнен в виде логического шифратора k-разрядных кодов сомножителей в 2k-pa3рядный код их произведения, синтез которого может быть проведен хорошо известными методами с использованием таблицы истинности. Ниже приведены фрагменты таблицы истинности для узла k-разрядного умножения 5, причем для определенности принято, ЧТО .. В таблице разряды множимого, поступающие по шине 8, обозначены как т4, т, т, т , разряды множителя, поступающие по шине 7, как П4 I п, п, п,., а разряды 2.k-разрядного произведения на выходах 9, 10, узла k-разрядного умножения 5 через pg , р , р , р ,

Р« РЬ Р Р

000

000 000 000 000 О 01

000

о о

000 о о 000 000 000 о о

о 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

1111 1101 11000011 1111 1110 11010010 1111 1111 11100001

Однако следует отметить, что в определенных случаях может оказаться целесообразным реализация узла умножения 5 в виде пирамиды взаимосвязанных одноразрядных сумматоров, а также объединение узла умножения 5 и сумматора 6 в общую матрицу взаимосвязанных полных сумматоров (например с целью сокращения оборудования и обеспечения регулярности структуры операционного модуля) . В данном устройстве в качестве узла запоминания переноса 11 может быть использован одноразрядный элемент. Например, им может быть двухтактный синхронный RS-триггер.

Устройство для умножения чисел работает следующим образом.

В исходном состоянии в регистре множимого 1 хранится т-разрядный двоичный код множимого, в регистре множителя 2 - т-разрядный код множителя (или, что то же ceiMoe, п-разрядные двоичнокодированные коды в системе счисления с основанием ,), сумматор 3 обнулен (здесь предполагается и , а сомножители представлены в виде положительных правильных дробей). Пусть множимое ,0001.1111; множитель ,1111.1111; произведение 0,0001.1110.1110.,0001.1110

В устройстве данный результат будет получен следующим образом.

Пусть к началу первого такта работы устройства в узлах умножения 5 сформированы соответственно следующие произведения 0000.1111; В(з 11ИЧ111 1110.0001 а в сумматорах б получены соответственно результаты Со 0000; +1111 1101 (возникшая при этом единица переноса будет записана в узле запоминания переноса 11 младшего разряда).

1-й такт: осуществляется прием

Информации в сумматор 3, ее .сложени

с содержимым сумматора 3, после чего осуществляется однотактный сдвиг в сумматоре 3 информации на четыре

0 разряда в сторону его младших разрядов . В итоге содержимое сумматора равно

р,0000.0000.0000+,0000.1101. ,0001 ,0000.1101.0001--,0000.0000.

Одновременно с этим в регистре множителя 2 был осуществлен однотак.тный сдвиг информации на четыре разряда в сторону его младших .разря0дов и были сформированы результаты

А,0001x1111 0000.llllj В 1111

х1111 111С.0001 С,0000; 0| 1110+

+1111+0001 1110

(возникшая при этом единица перено5са записывается в узле запоминания переноса 11 младшего разряда).

2-й такт: в данном такте и всех последующих осуществляется последовательность, действий, аналогичная

0 первому такту. В итоге выполнений второго такта получают следующие результаты

- +f0000.1110.0001,0000.0000. 1101+,0000.1110.0001,0000,1110.

5 lllQC-,0000.0000.lllO; A2 0001x xOOOO 0000.0000; B2 llll 0000 0000.0000; С„ 0000; 0„ 0000+0000+ +OOOJ.0001.

-й такт (такт окончательного учёта переносов): в итоге получаем

0

Pj ,oooo.ooao.1110+,0000.0001.

.0000,0000.0001,1110. .

На этом процесс умножения закаичцвается, окончательный результат

5 сформирован в m младших разрядах сумматора 3 частичных произведений.

Как уже указывалось, подобное умножение в принципе может быть осуществлено для любой системы счисления с основанием , в том

0 числе, например) для :Ь-ичнокодированных операндов в системе счисления с основанием

Время операции при этом сокраща5ется, за счет того, -что сигнал па

Авторы

Даты

1980-09-15—Публикация

1978-01-25—Подача