пы которых соединены с соответствующими выходами второго регистра множителя, выходы первого и второго комбинационных сумматоров подключены к соответствующим входам второй группы соответственно первого и второго сумматоров результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1981 |

|

SU991414A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее первый и второй регистры множимого, информационные входы которых подключены соответстэ н-нр к первому и второму входам множимого устройства, первый и второй регистры множителя, информационные входы которых подключены соответственно к первому и-второму входам множителя устройства, регистр сдвига, входы занесения и сдвига которого являются п.ервым и вторым управляющими входами регистров множимого и множителя, первый и второй сумматоры результата, сумматор в избыточной системе счисЛенин, первый и вторЪй регистры результата, выходы k + 1 (где k разрядность входных операндов ) младших разрядов которых подключены к входам первой группы соответственно первого и второго сумматоров результата, выходы разрядов со второго по (k+2)-й первого и второго сумматороы результата соединены с соответствующими входами первого и второго регистров результата соответственно, ВЫХОДЫ старшего (k+2)-ro разряда которых подключе1ы соответственно к первсму и втбюму входам сумматора в избыточной системе счисления, выходы которого являются выходами результата устройства, а третий и четвертый входил подключены к выходам переноса соответственно, первого и второго сумматоров результата, отличающееся тем, что, с целью упрощения, оно содержит регистр задержки, четьфе блока элементов 2И-2И-2ИЛИ и два комбинат ционных сумматора, причем первый и второй входы регистра задержки соединены соответственно с первым и вторым входами мнозкителя устройства, а первый и второй выходы (Л подключены соответственно к первым и ВТО1Ж1М входам первого и второго блоков элементов 2И-2И-2ИЛИ, у которых входы первой группы подключены к соответствующим выходам соответственно первого и второго регистров мнбжимого, а входы.второй группы подключены к соответствующим выходам соответственно второго- и первого регистров множимооо го, выходы первого и второго блоков элементов 2И-2И-2ИЛИ соединены со с соответствующими входгши первой 4 группы первого и второго комбинационных сумматоров соответственно в О разрядах с первого по k-й, входы второй группы которых в разрядё1Х qo второго по k+1 -и подключены к соответствующим выходам соответственно третьего и четвертого блоков элементов 2И-2И-2ИЛИ, первые и вторые вхо которых подключены соответственно к первому и второму входам множимого устройства, выходы первого регистра множителя подключены к соответствующим входам первой группы соответственно третьего и четвертого блоков элементов 2И-2И-2ИЛИ, входы второй груп

1

Устройство относится к вычислительной технике и может быть при,манено в качестве решающего узла цифровой вычислительной машины.

Известно устройство умножения двоичных чисел, представленных последовательным кодом, содержащее 2п-раэрядный сумматор,(n-l)-разрядные регистры множимого и множителя и элементы И fl.

Однако в этом устройстве результат получается через п циклов вычисления.

Известно также устройство для умножения, содержащее регистры множимого и множителя, регистр результата, сумматор результата, сумматор сомножителей, блок анализа разрядов, регистр сдвига, элементы И и элементы ИЛИ, в котором производится ввод сомножителей поразряд- . но, старшими разрядами вперед 2 .

Однако в этом устройстве каждый разряд результата получается за три работы, т.е. устройство имеет низкое быстродействие.

Наиболее близким к предлагаемому является устройство ддя умножения, содержащее регистр сдвига, выходы которого подключены к информационным входам первого и третьего коммутатора, управляющие входы которых соединены соответственно с выходом элемента ИЛИ и со вторым входом множителя устройства, а выходы подключены ко входрм соответственно регистра множителя и регистра знака множителя, выходы регистра множителя соединены с первыми входами первого и вторрго блоков элементов И, вторые входы которых соединены с выходами соответственно первого и второго регистрой множимого, входы которых подключены соответственно к первому и второму входу множимого устройства, выходы блоков элементов И подключены к информационным входам второго коммутатора, управляющие входы которого соединены с выходами регистра знака множителя, а первая и вторая группа выходов соединены с первой группой соответственно первого и второго сумматоров результата, вторые группы входов которых подключены к выходам младших рарядов соответственно первого и второго регистров результата, первые входы первой и второй групп сумматору в избыточной системе счисления подключены к выходам переноса

соответственно первого и второго сумматоров результата, выходы разрядов которых соединены со входами соответственно первого и второго регистров результата, выходами старшего результата подключенных ко вторым входам первой и второй групп сумматора в избыточной двоичной системе счисления, выходы которого подключены к выходам устройства, входы элемента ИЛИ подключены ко входам множителя устройства .

Устройство производит умножение двух чисел, которые представлены в избыточной двоичной системе счисления, в которой результат вычисления произведения выводится последовательным кодом, начиная со старщего разряда, в процессе вычисления. Недостатком известного устройства является сложность алгоритма

:умножения, что вызывает большие аппаратурные затраты.

Целью изобретения является упрощение устройства.

Поставленная цель достигается .тем, что устройство для умножения, содержащее первый и второй регист- . ры множимого, информационные входы которых подключены соответственно к

первому и второму входам множимого устройства, первый и второй регистры множителя, информационные входы которых подключены соответственно к первому и второму входам множителя устройства, регистр сдвига, входы занесения и сдвига являются первым и вторым управляющими входами устройства, а.выходы соединены с соответствующими управляющими вхо-. дами регистров множимого и множителя, первый и второй сумматоры результата, сумматор в избыточной системе счисления, первый и второй регистры результата, .выходы k+1 (где k - разрядность входных операндов) младших разрядов которых подключены ко входам первой группы соответственно первого и второго сумматоров результата, выходы разрядов со второго по Xk+2)-ft первого и второго сумматоров результа-.

та соединены с соответствующими входами пер.вого и второго регистров результата соответственно, выходы старшего (К-ь2)-го разряда которых подключены соответственно к первомуи второму входам сумматора в избыточной системе счисления выходы которого являются выходами результата устройства, а третий и четвертый входы подключены к выходам переноса соответственно первого и второго сумматоров результат содержит регистр задержки, четыре блока элементов 2И-2И-2ИЛИ и два комбинационных Сумматора, причем первый и второй входы регистра задержки соединены соответственно с первым и вторым входами множителя устройства, а первый и второй выходы подключены соответственно к первым и вторым входам первого и второго блоков элементов 2И-2Иг2ИЛИ у которых входы первой группы подключены к соответствующим выходам соответственно первого и второго регистров множимого, а входы второй группы подключены к соответствующим выходам соответственно второго и первого регистров множимого, выходы первого и второго блоков элементов 2И-2И-2ИЛИ соединены с соответствующими входами первой группы первого и второго комбинационных сумматоров соответственно в разрядах с первого по k-й, входы второй группы которых в разрядах со второго пo(k+i)-й подключены к соответствующим выходам соответственно третьего и четвертого блоков элементов 2И-2И-2ИЛИ, первый и вторые входы которых подключены соответственно к первому и второму входам множимого устройства, выходы первого регистра множителя подключены к соответствующим входам первой группы соответственно третьего и четвертого блоков элементов 2Й-2И 2ИЛИ, входы второй группы которых соединены с соответствующими выхоДс1ми второго регистра множителя, выходы первого и второго комбинационных сумматоров подключены к соотвёТ ствующим входам второй группы соответственно первого и второго сумматоров результата.

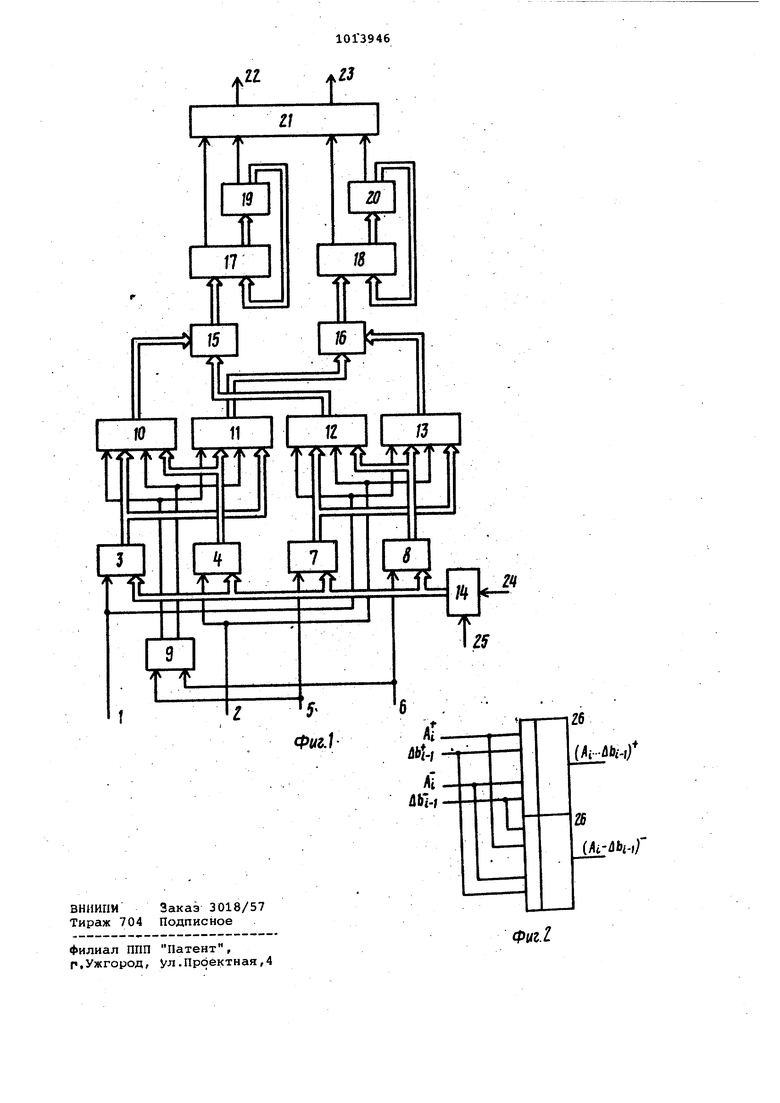

На фиг. 1 приведена структурная схема устройства} на- фиг. 2 - два элемента 2И-2И-2ИЛИ.

Устройство для умножения имеет входы 1 и 2 множимого устройства, первый и второй регистры 3 и 4 множимого-, первый и второй входы 5 и б множителя устройства, первый и второй регистры 7 и 8 множителя, ретистр 9 задержки, блоки 10-13 элементов 2И-2И-2ИЛИ, регистр 14 сдвига, комбинационные сумматоры 15 и 16,:сумматоры 17 и 18 результата, регистры 19 и 20 результата, сумматор 21 в двоичной избыточной системе счисления и выходы 22 и 23 устройства.

Входы 1 и 2 множимого устройства соединены с информационными входами соответственно первого и второго, регистров 3 и 4 множимого, входы 5 и 6 множителя устройства соединены

Q с информационными входами соответственно первого и второго регистров 7 и 8 множителя и с первым и вто- . . рым входами регистра 9 задержки, первый и второй выходы которого подключены соответственно к первым и вторым входам первого и второго блоков 10 и 11 элементов 2И-2И-2ИЛИ, а первые и вторые входы третьего и четвертого блоков 12 и 13 элементов 2И-2И-2ИЛИ подключены соответственно к первому и второму входам 1 и 2 множимого устройства, уп равляющие входы регистров 3, 4 и 7 и 8 множимого и множителя подключены к выходам регистра 14 сдвига,

5 входы занесения 24 и Сдвига 25 которого являются первым и вторым управляющими входами устройства, йыходы первого регистра 3 множимого прдключены ко входам первой групп пы первого блока 10 элементов

2И-2И-2ИЛИ и входам второй группы второго блока 11 элементов 2И-2Й2ИЛИ, выходы второго регистра 4 множимого подключены ко входам второй группы первого блока 10 элементов

2И-2И-2ИЛИ и ко входам первор группы второго блока 11 элементов 2И 2И-2ИЛИ, выходы первого регистра 7 множителя подключены ко входам :первой группы третьего блока 12

0 элементов 2И-2И-2Ш1И и ко входам второй группы четвертого блока 13 элементов 2И-2И-2ШШ, выходы : второго регистра 8 множителя подключена ко входам -второй группы третьего блока 12 элементов .

2И-2И-2ИЛИ и ко входам первой группы четвертого блока 13 элементов 2И-2И-2ИЛИ, выходы первого и второго блоков 10 и 11 элементов

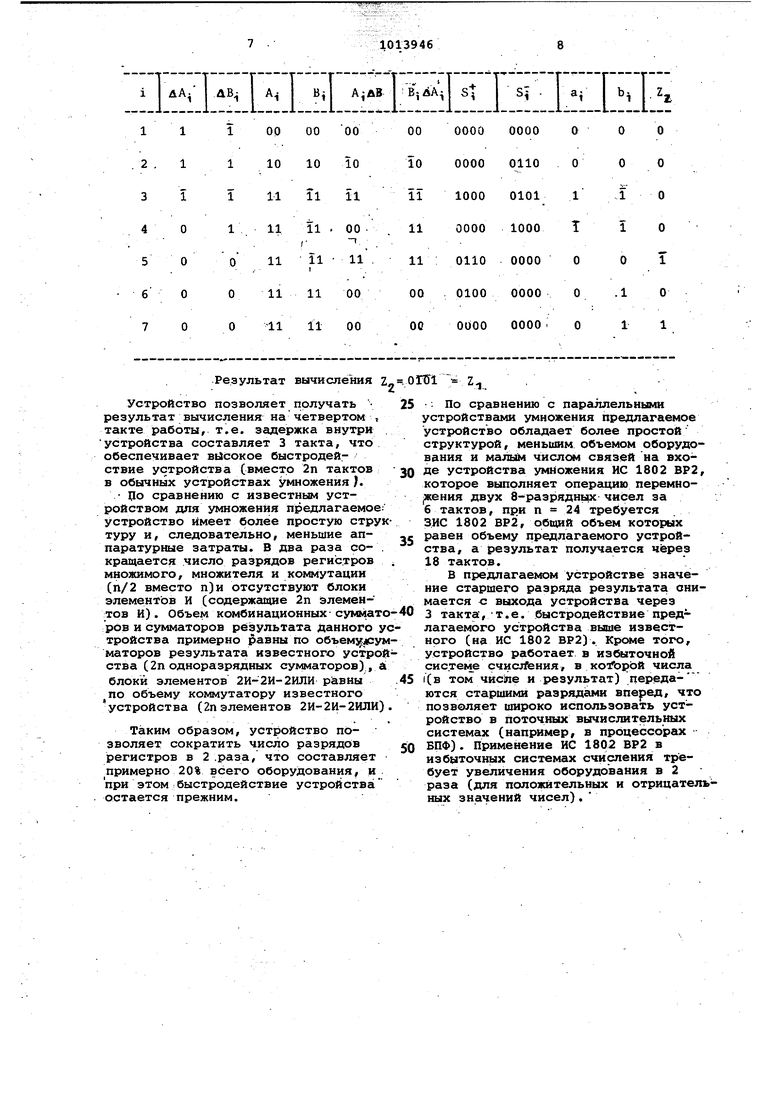

0 2И-2И-2ИЛИ соединены с соответствующими входами первой группы соответственно первого и второго комбинационных сумматоров 15-и 16, у . . которых входы второй труппы подключены к соответствующим выходам третьего и четвертого блоков 12 и 13 элементов 2И-2И-2ИЛИ сортветственно, а выходы соединены с соответствующими входами первой группы соответственно первого и второго сумматоров 17 и 18 результата, входы второй группы которых соединены с соответствующими выходами младших разрядов соответственно первого и второго регистров 19 и 65 20 результата, входы KOTOIMX соедийены с соответствующими выходами первого и второгоСумматоров 17 и 18 результата соответственно, выходы переноса которых подключены соответственно к первому и второму входам сумматора 21 .в избыточной двоичной системе счисления, третий и четвертый входы которого подключе ны к выходам старшего разряда соответственно первого и второго регист ров 19 и 20 результата, а выходы сумматора 21 в избыточной двоичной системе являются выходами устройства. На фиг. 2 изображены два элемент 2И-2И-2ИЛИ 26. Алгоритм работы устройства задается формулой ,.,2-(А.ДВ., В. ДА). где А- - текущее значение множимого В- - текущее значение множителя ДА- - значение i-ro разряда множимого;ЛВ - значение (i-l)-ro разряда множителя. В нулевом такте работы устройства регистры 3 и 4 множимого, регистры 7 и 8 множителя и регистры 19 и 20 результата сбрасываются в нулевое состояние, а в первый разряд регистра 14 сдвига заносится единица, которая в первом такте поступит на управляющие входы старшег k-ro разряда регистров 3,4 и 7, 8 и сдвинется во второй разряд per гистра 14 сдвига. Во-втором такте единица с выхода второго разряда регистра 14 сдвига поступит на управляющие входы (k-l)-ro разряда регистр 14 сдвига осуществляет преобразование последовательного кода множимого А и множителя В в параллельный. Значения множимого А и множителя В последовательным кодом в избыточной двоичной системе счисления, ста шими разрядами вперед, поступают на входы 1,2 и 5,6 устройства. Значени множителя В задерживаются на один тактрегистром 9 задержки. В регист рах 3 и 4 множимого и в регистрах. 7 и 8 множителя накапливается , . разрядов множимого А и множителя В. Первый и второй блоки 10 и 11 эл ментов 2И-2И-2ИЛИвыдают текущие зн чения произведения () и (А,-ДВ,) .(фиг. 2), которые подаютс на входы первой группы соответствен первого и второго комбинационных су маторов 15 и 16, на входы второй гр пы которых поступают текущие значе ния произведения . ) (BjflA- ) Первый комбинационный сумматор 15, первый сумматор 17 результата и первый регистр 19 результата представляют собой сумматор-накопитель для положительных значений произведения АВ, а второй комбинационный сумматор 16, второй сумматор 18 результата и второй регистр 20 результата- сумматорнакопитель для отрицательных значений произведения АВ. Код текущего произведения (A:jAB- Л поступает на входы первой группы с первого по k-й разряд, а код текущего произведения (В.,-лА.( ) поступает на входы второй группы со второго по (k+1)-и разряд первого комбинационного сумматора 15, с выходов которого ()-й разрядный код подается н-а входы второй группы первого сумматора 17 результата, на входы первой Группы которого со второго по (k+2)-разряд подаются значения ;(k-i-1) младашх разрядов суммы 5 , пол5 ченной на выходах сумматора 17 в предыдущем (1-1}-м такте работы устройства, с выходов (k+1) младших разрядов регистра 19 результата. Значение старшего (k-f-3)-ro разряда полученной суммы S. с выходов переноса сумматоров 17 и 18 результата подаются на первый и второй входы сумматора 21, работающего в избыточной системе счисления, образуя положительные значения чисел А и В-|, отрицательные значения которых А и ВТ- образуются зна.чениями (k+2)-ro разряда суи№1ы S.J . , которые поступают на третий и четвертый входы сумматора 21 с выходов старшего (k+2)-ro разряда регистров 19 и 20 результата. Значения .(k+Z) младших разрядов суммы Sj с выходов разрядов сумматора 17 и 18 заносятся в регистрыа19 и 20 результата. Сумматор 21 суммирует числа А. и В и вьщает результат произведения А-В последовательнь1м кодом, .старшими разрядами вперед, на выходы 22 (положительных значений) и 23 (отрицательных значений)результата устройства. Для пояснения работы устройства перемножим два числа А ИТО и В 1111 (п 4): 0000 1Г11 1111 1111 Z. 01010010 Z 0101 или округляя до п 4 i j ДА. I ДВ I A I BJ I В,ЛАИ St

Результат вычисления z.orffl Z Устройство позволяет получать результат вычисления на четвертом , такте работы, т.е. задержка внутри устройства составляет 3 такта, что обеспечивает BilcoKoe быстродействие устройства (вместо 2п тактов в обычных устройствах умножения Ь Цо сравнению с известным устройством для умножения предлагаемое устройство имеет более простую стру туру и, следовательно, меньшие аппаратурные затраты. В два раза сокращается число разрядов регистров множимого, множителя и коммутации (п/2 вместо п)и отсутствуют блоки элементов И (содержгицие 2п элемен,тов И). Объем комбинационных суммат ров и сумматоров результата данного тройства примерно равны по объем лру маторов результата известного устро ства (2п одноразрядных сумматоров), блоки элементов 2И-2И-2ИЛИ равны по объему коммутатору известного устройства (2п элементов 2И-2И-2ИЛИ Таким образом, устройство позволяет сократить число разрядов регистров в 2 .раза, что составляет примерно 20% всего оборудования, и при этом быстродействие устройства остается прежним.

1-. Г S . I a I b I - По сравнению с параллельными устройствами умножения предлагаемое устройство обладает более простой структурой, меньшим объемом оборудования и малым числом связей на входе устройства умножения ИС 1802 ВР2, которое выполняет операцию перемноркения двух 8-разрядных чисел за 6 тактов, при п 24 требуется ЗИС 1802 ВР2, общий объем которых равен объему предлагаемого устройства, а результат получается через 18 тактов. В предлагаемом устройстве значение старшего разряда результата снимается с выхода устройства через 3 такта,т.е. быстродействие предлагаемого устройства выше известного (на ИС 1802 ВР2) . Крсяке того, устройство работает в избыточной системе , в числа |(в том числе и результат) переда- ются старшими разрядами вперед, что позволяет широко использовать устройство в поточных вычислительных системах (например, в процессорах БПФ). Применение ИС 1802 ВР2 в избыточных системах счисления требует увеличения оборудования в 2 раза (для положительных и отрицательных значений чисел).

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения п-разрядных чисел,представленных последовательным кодом | 1975 |

|

SU631919A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-25—Подача