(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1978 |

|

SU896617A2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения в избыточной системе счисления с запоминанием переноса | 1985 |

|

SU1252773A1 |

Изобретение относится к области вычислительной техники и может быть ислользовано при разрабоке быстродействующих устройств для умножения чисел в любой позиционной системе счисления, удобных для изготовления в составе больших интегральных схем.

Иавестно устройство для умножения чисел, содержащее п-разрядные репистры МНожимого и множителя, сумматор частичных произведений, цепи сдвига на один разряд в регистре множителя и в сумматоре частичных произведений, блок управления, выходы которого соединены с управляющими входами суммато.ра частичных произведений, регистров множимого и множителя 1.

Недостатком такого устройства является его низкое быстродействие, так как в каждом такте работы устройства обрабатывается только одна двоичная цифра (разряд) множителя.

Наиболее близким является устройство для у.множения, содержащее регистры множимого и .множителя, нажапливающий :суМ|Матор, .комбияа:П/ион,ный су1М,матор и /г-одноразрядных умиожителей (п - число разрядов множимого), причем первые входы одноразрядных умножителей соединены с выхода.ми соответствующих разрядов регистра множимого, а вторые входы - свыходо.м первого разряда регистра миож1Ителя, управляющие входы сдвига регистра множителя и накапливающего сумматора соединены с первы-м и вторым управляющими входами зстройства, управляющие входы одноразрядных з ножителей соединены с третьим управляющим входом устройства, входы каждого разряда комбинационного сумматора подключены к выходу старшего разряда соответствующего одноразрядного умножителя и к выходу младшего разряда последующего одноразрядного умножителя, вы.ходы ко.м15 бинационного сзмматора и младшего разряда первого одноразрядного умнолсителя подключены ко входам накапливающего сумматора 2.

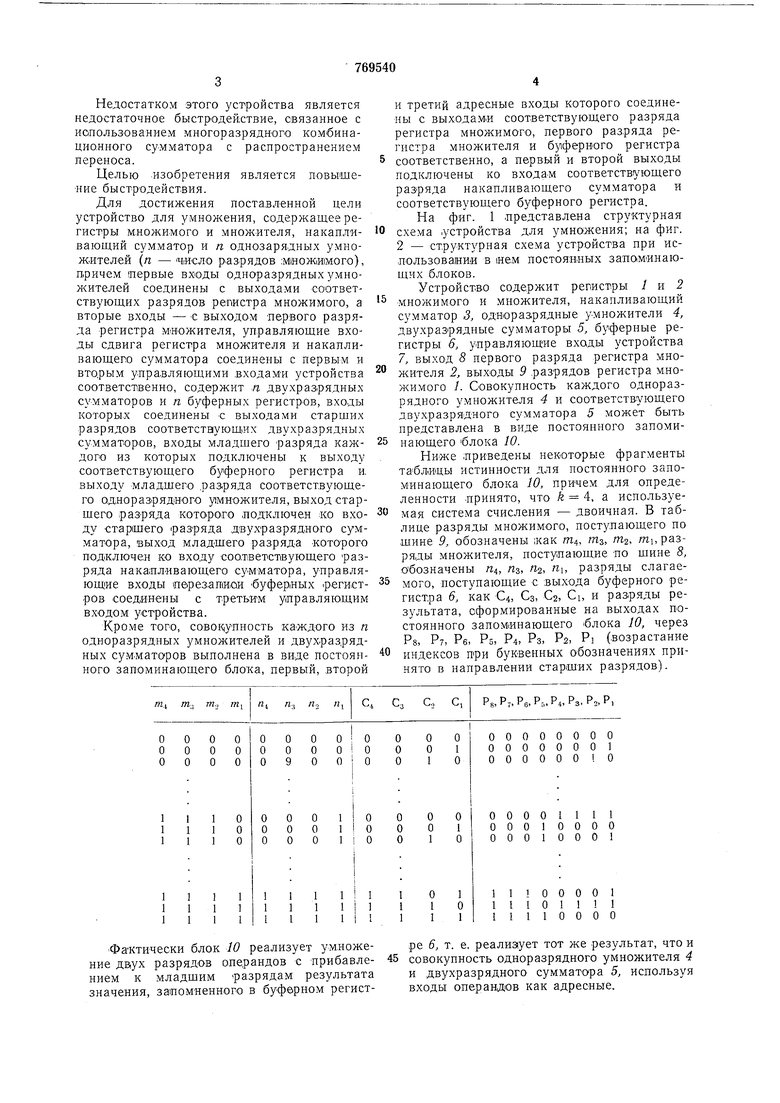

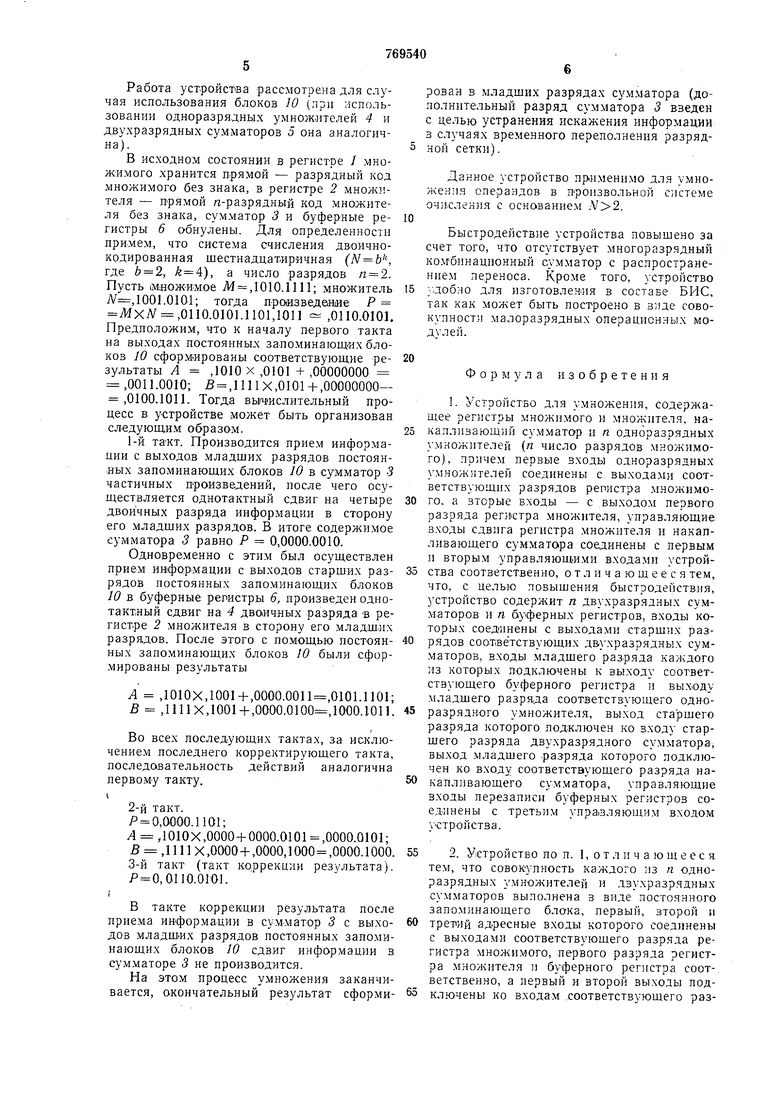

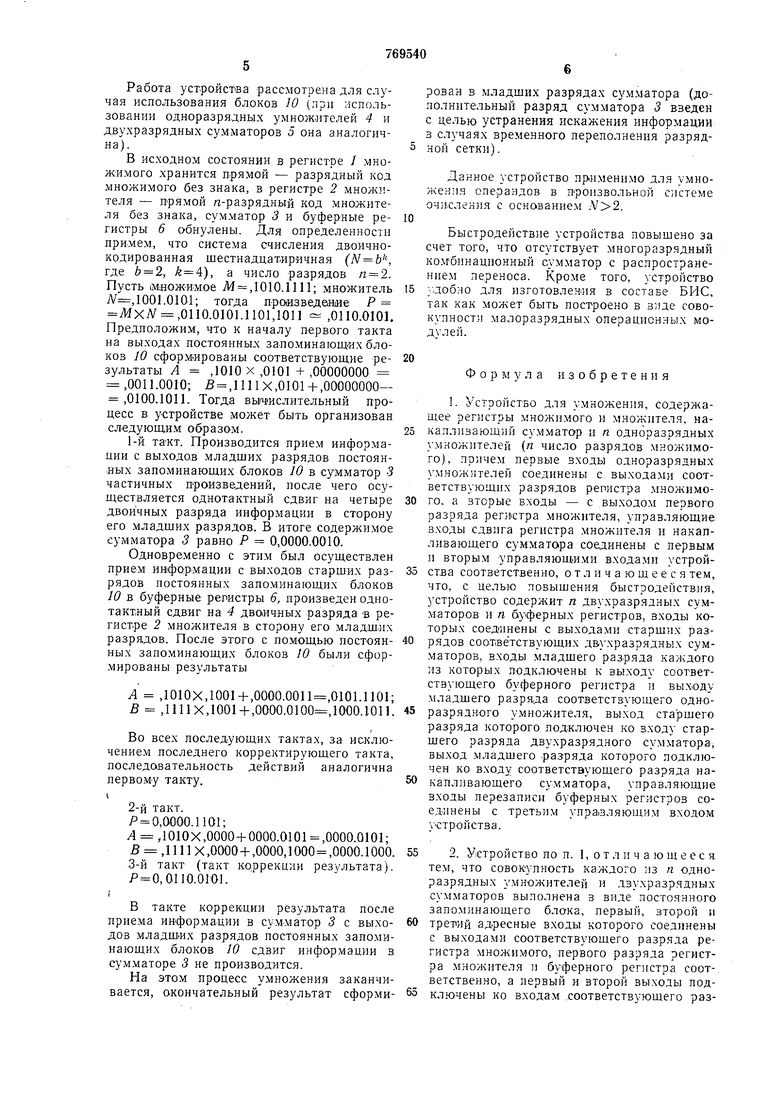

20 Это устройство предназначено для пере.множения операндов в произвольной системе счисления ;с основанием . В частности, интересен использования 6-ичло:кодированной системы счисления с основанием (когда 6-ичные разряды группируются по k), при использовании которой имеется возможность повысить быстродействие устройства при.мерно в k раз по сравнению со случаем использова30 йия &-ИЧной системы счисления. Недостатком этого устройства является недостаточное быстродействие, связанное с использованием многоразрядн-ого комбинацио.нного сумматора с распространением переноса. Целью изобретения является повышение быстродействия. Для достижения поставленной цели устройство для умножения, содержащее регистры М.НОЖИМОГО и множителя, накапливающий сумматор и п однозарядных умножителей (п - число разрядов Мйожймого), причем первые входы одноразрядных умножителей соединены с выходами соответствующих разрядов регистра множимого, а вторые входы - -с выходом первого разряда регистра м-ножителя, управляющие входы сдвига регистра множителя и накапливающего сумматора соединены с первым и вторым управляющими входами устройства соответственно, содержит п двухразрядных сумматоров и п буферных регистров, входы которы.х соединены с выходами старших разрядов соответстаующ.их двухразрядных сумматоров, входы младщего разряда каждого из которых подключены к выходу соответствующего буферного регистра и, выходу младщего раз.ряда соответствующего одноразрядного у1множителя, выход старщего разряда которого подключен «о входу старшего разряда двухразрядного сумматора, выход младщего разряда которого подключен ко входу соответствующего разряда накапливающего сумматора, управляющие входы перезаписи буферных .р-еги-стров соединены с третьим управляющим входом устройства. Кроме того, совоК|уппость каждого из п одноразрядных умнол ;ителей и двухразрядных cyMwaToipOB выполнена в виде постоянного запоминающего блока, первый, второй Фактически блок 10 реализует умножение дв|ух разрядов операндов с прибавле-45 нием к младщим разрядам результата значения, запомненного в буферном регистИ третий адресные входы которого соединены с выходами соответствующего разряда регистра множимого, первого разряда регистра множителя и буферного регистра соответственно, а первый и второй выходы подключены ко входа-м соответствующего разряда накапливающего сумматора и соответствующего буферного регистра. На фиг. 1 представлена структурная схема (устройства для умно1жения; на фиг. 2 - структурная схема устройства при использовании в яем постоянных запоминающих блоков. Устройство содержит регистры 1 vi 2 множимого и множителя, накапливающий сумматор 3, однораз-рядные у-множители 4, двухразрядные сумматоры 5, буферные регистры 6, управляющие входы устройства 7, выход 8 первого разряда регистра множителя 2, выходы 9 разрядов регистра множимого 1. Совокупность каждого одноразрядного умножителя 4 и соответствующего двухразрядного сумматора 5 может быть представлена в виде постоянного запоминающего блока 10. Ниже приведены некоторые фрагменты таблицы истинности для постоянного запоминающего блока 10, причем для определенности принято, что 4, а используемая система счисления - двоичная. В таблице разряды множимого, поступающего по щине 9, обозначены жак Шл, т, т, mi, разряды множителя, поступающие по щине 8, обозначены п, Пз, 2, п, разряды слагаемого, поступающие с выхода буферного регистра 6, как С4, Сз, Сг, Сь и разряды результата, сформированные на выходах постоянного запоминающего блока 10, через PS, Р, Рб, PS, Р4, РЗ, Р2, PI (возрастание индексов при буквенных обозначениях принято в направлении старших разрядов). ре 6, т. е. реализует тот же результат, что и совокупность одноразрядного умножителя 4 и двухразрядного сумматора 5, используя входы операндов как адресные. Работа уст.ройстаа рассмотрена для случая использования блоков 10 (лри использовании одноразрядных умножителей 4 и двухразрядных сумматоров 5 она аналогична). В исходном состоянии в регистре / множимого хранится прямой - разрядный код множимого без знака, в регистре 2 множителя - прямой я-разрядный код множителя без знака, сумматор 3 и буферные регистры 6 обнулены. Для определенности примем, что система счисления двоичнокодированная шестнадцатиричная (N b, где 6 2, 4), а число разрядов /г 2. Пусть 1М:ножимое Af ,1010.1111; множитель Л,1001.0101; тогда произведеиие Р МХЛ ,0110.0101.1101,1011 ,0110.0101. Предположим, что к началу первого такта на выходах постоянных запоминающих блоков 10 сфорМИрованы соответствующие результаты Л ,1010 X ,0101 + ,00000000 ,0011.0010; S ,l 111 Х,0101+ ,00000000- ,0100.1011. Тогда вычислительный процесс в устройстве может быть организован следующим образо м. 1-й такт. Производится прием информации с выходов младших разрядов постоянных запоминающих блоков 10 в сумматор 3 частичных произведений, после чего осуществляется однотактный сдвиг на четыре двоичных разряда информации в сторону его младших разрядов. В итоге содержимое сумматора 3 равно Р 0,0000.0010. Одновременно с этим был осуществлен прием инфорМации с выходов старших разрядов постоянных запоминающих блоков 10 в буферные регистры 6, произведен однотакхный сдвиг на 4 двоичных разряда в регистре 2 множителя в сторону его младших разрядов. После этого с помощью постоянных запоминающих блоков 10 были сформированы результаты А ,1010Х,1001+,0000.0011,0101.1101; В ,1111Х,1001+,0000.0100,1000.101. Во всех последующих тактах, за исключением последнего корректирующего такта, последовательность действий аналогична первому такту. 2-й такт. Р 0,0000.1101; Л Д010Х,0000+0000.0101 ,0000.0101; 5 ,1111X,0000+ ,0000,1000,0000.1000 .3-й такт (такт коррекции результата). Я 0, 0110.0101. I в такте коррекции результата после приема информа.ции в сум.матор 3 с выходов младших разрядов постоянных запоминающих блоков 10 сдвиг информации в сумматоре 3 не производится. На этом процесс умножения заканчивается, окончательный результат сформи ован в младших разрядах сумматора (доолнительный разряд сумматора 3 введен целью устранения искажения информации случаях временного переполнения разрядой сетки). Данное устройство пр-нменимо для умноен;1я операндов в произвольной с)1стеме числекия с основанием . Быстродействие устройства повышено за чет того, что отсутствует многоразрядный о.гбинационный сумматор с распространением переноса. Кроме того, устройство злобно для изготовлена я в составе БИС, так как может быть построено в совокупност) малоразрядных операционных модулей. Формула изобретения . Устройство для умножения, содержащее регистры множимого и множителя, накаплнвающ)1Й сум.матор и п одноразрядных -множителей (п число разрядов множимого), пржчем первые входы одноразрядных умножителей соединены с выходами соответствующих разрядов регистра .множимого, а вторые входы - с выходом первого разряда регистра множителя, управляющие входы сдвига регистра множителя и накапливающего сумматора соединены с первым и вторым управляющими входами устройства соответственно, отличающееся тем, что, с целью повышения быстродействия, устройство содержит л двухразрядных сумматоров и п буферных регистров, входы которых соединены с выходами старших разрядов соответствующих двухразрядных сумматоров, входы младшего разряда каждого из которых подключены к выходу соответствующего буферного регистра и выходу младшего разряда соответствующего одноразрядного умножителя, выход старшего разряда которого подключен ко входу старшего разряда двухразрядного сумматора, выход младшего разряда которого подключен ко входу соответствующего разряда накапливающего сумматора, управляющие входы перезаписи буферных регистров соединены с третьим упра.вляющим входом устройства. 2. Устройство по п. 1, о т л и ч а ю щ е е с я. тем, что совокупность каждого мз п одноразрядных умножителей и двухразрядных сумматоров выполнена в виде постоянного запоминающего блока, первый, второй и третий адресные входы которого соединены с выходами соответствующего разряда регистра множимого, первого разряда регистра множителя и буферного регистра соот-. ветственно, а первый и второй выходы подключены ко входам .соответствующего разряда накаштивающего суммато,ра и Соответствующего буферного регистра соответственно. Источна-1ки информации, принятые во внимание лри экспертизе: 1. Майоров С. А. и др. Принципы организации цифровых машин. Л., «Машиностроение, 1974, с. 297. 2. Авторское свидетельство по заявке № 1412260/18-24, кл. G 06 F 7/39, 1971 (прототип).

I I

Авторы

Даты

1980-10-07—Публикация

1978-01-25—Подача