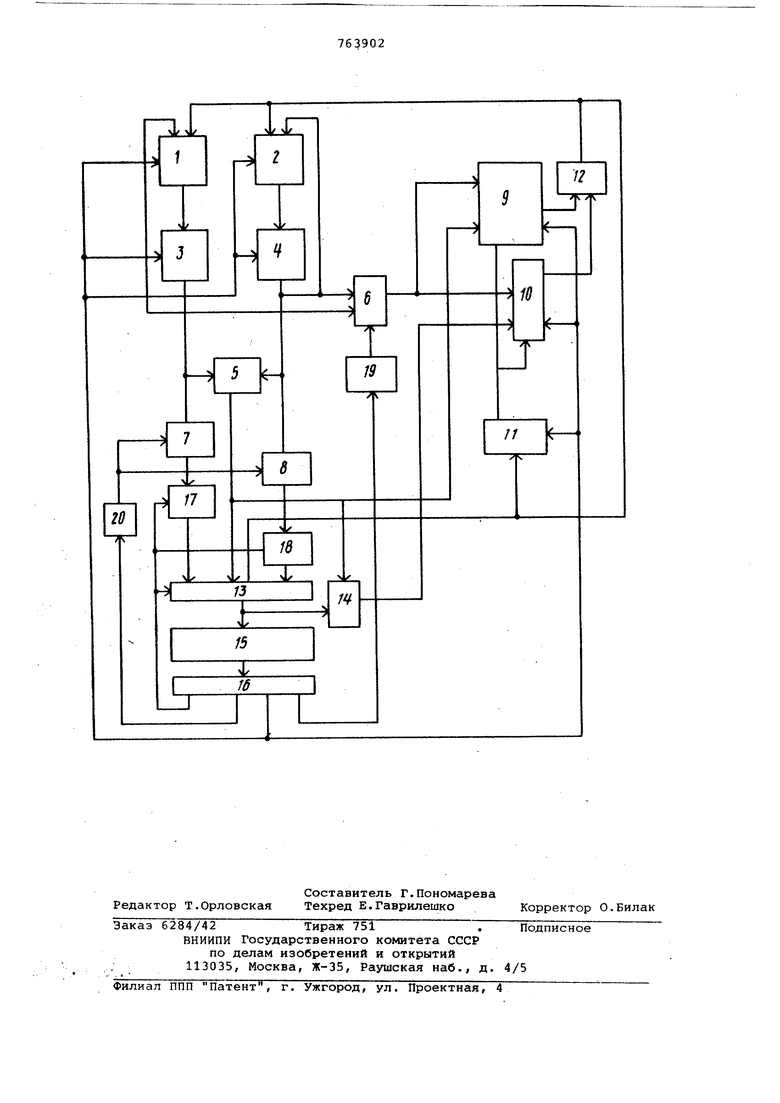

Изобретение относится к цифрово вычислительной технике и может быть применено в электронной вычислительной машине. Известны микропрограммные проце соры с самодиагностикой, содержащие задублированные блоки обработки и локальные памяти, блок упр ления и основную память til 2 . Не достатком известных процессоров является то, что для обеспечения их работоспособности при отказах оборудования требуется дополнитель ное резервирование на уровне устро ств и разработка специальных программ отключения/подключения резер вных процессоров. Наиболее близким техническим ре шением к данному устройству является микропрограммный процессор с самодиагностикой 3, содержащий первую и вторую локальные памяти с первым и вторым б;юками обработки, коммутатор и компаратор данных триггер управления, основную память с регистрами адреса и данных, микропрограммную память с узлами формирования адреса и микроопераций. Недостатком известного решения является сложность оборудования контроля и восстановления работоспособности процессора при возникновении отказа. Цель изобретения - упрощение процессора. Эта цель достигается тем, что микропрограммный процессор с самодиагностикой, содержащий первую и вторую локальные , выходы которых соединены соответственно с информационными входами первого и второго блоков обработки данных, выходы которых соединены соответственно с первыми информационными входсьми первой и второй локальных памятей, с первыми и вторыми информационными входами коммутатора данных и компаратора данных, управляющий вход коммутатора данных соединен с выходом триггера управления, выход KOMiviyTaTopa данных соединен с информационным входом основной памяти, первый управляющий вход которой .соединен с первым выходом управления узла формирования микроопераций, с управляющими входами регистра адреса, первого и второго блоков обработки данных, первой и второй локальных памятей, вторые информационные входы первой и второй локальных памятей соединены с разрядным выходом регистра данных, с информационным входом регистра адреса и с первым информационным входом узла формирования адреса, управляющий вход которого соединен со вторым выходом управления узла формирования микроопераций, вход которого соединен с выходом микропрограммной памяти, вход которой соединен с выходом узла формирования адреса, разрядный выход регистра адреса соединен с адресным входом основной памяти, выход которой соединен с пе вым информационным входом регистра данных, содержит первый и второй те товые компараторы, первый и второй регистры результатов теста, генератор эталона, регистр возврата и память разгрузки, к первому и второ му информационным входам которой подключены, соответственно, выход коммутатора данных и разрядный выход регистра возврата, к адресному и управляющему входам памяти разгрузки подключены разрядный выход регистра адреса и первый выход управления узла формирования микроопераций соответственно, а к выходу памяти разгрузки - второй информационный вход регистра данных, третий выход управления узла формирования микроопераций соединен со входом триггера управления, выход узла формирования адреса соединен с информационным входом регистра возврата, выход компаратора данных подключен ко второму информационному входу узла формирования адреса к управляющему входу регистра возврата и ко второму управляющему вхо ду основной памяти, четвертый выход управления узла формирования микроопераций соединен со входом генератора эталона, выход которого подключен к первым входам первого и второго тестовых компараторов, ко вторым входам которых подключены с ответственно выходы первого и втор го блоков обработки данных, второй выход управления узла формирования микроопераций соединен с управляющими входами первого и второго ре гистров результатов теста, к информационным входам которых подклю чены соответственно выходы первого а второго тестовых компараторов, а выходы первого и второго регистров результатов теста соединены соотве ственно с третьим и четвертым информационными входами узла формиро ния адреса. Сохранение работоспособности пр цессора при обг аружении отказа обо рудования обеспечивается автоматической перезаписью состояния всех запоминающих элементов процессора в паглять разгрузки, причем для дублированных блоков запись состояния каждой половины дубля производится раздельно. После перезаписи начинается выполнение диагностического теста, по результатам которого устанавливаются первый и второй регистры результатов теста, что позволяет локализовать неисправную половину дубля. Затем в процессоре восстанавливается состояние, в котором находилась исправная половина дубля в момент обнаружения отказа, и выполнение вычислений продолжается. При использовании данного устройства на аппаратуру блоков обработки данных и локальных памятей возлагаются только рабочие функции по хранению и обработке данных, что позволяет использовать для реализации указанных блоков типовые средние и большие интегральные схемы. На чертеже показана структурная схема предложенного процессора. В состав процессора входят: первая локальная память 1, вторая локальная память 2, первый блок 3 обработки данных, второй блок 4 обработки данных, компаратор 5 данных, коммутатор 6 данных, первый тестовый компаратор 7, второй тестовый компаратор 8, основная память 9, память разгрузки 10, регистр 11 адреса, регистр 12 данных, узел 13 формирования адреса, регистр 14 возврата, микропрограммная память 15, узел 16 формирования микроопераций, первый регистр 17 результатов теста, второй регистр результатов теста 18, триггер управления 19., генератор эталона 20. Процессор работает следующим образом. При выполнении программы команды считываются из основной памятн 9 в регих:тр данных 12. Код операции из регистра данных 12 поступает в узел 13 формирования адреса . По выработанному в этом узле адресу из микропрограммной памяти 15 считывается первая микрокоманда микропрограммы обработки операндов для данной команды. При выполнении микропрограммы обработки операндов узел 16 формирования микроопераций вырабатывает управляющие воздействия, по которым операнды для данной команды считываются из основной памяти 9 и через регистр данных 12 записываются в первую и вторую локальные Пс1мяти 1 и 2 параллельно. Если в процессоре отсутствуют неисправности, то в каждый данный момент первая и вторая локальные Пс1Мяти 1 и 2 хранят одинаковую информацию. В ходе обработки операнды поступают из первой и второй локальных памятей 1 и 2 в первый

3 и второй 4 блоки обработки данных параллельно и независимо, причем для этих блоков узлом 16 формирования микроопераций задается выполнение одинаковых операций. Результат обработки в зависимости от выполняемой команды записывается либо в первую и вторую локальные памяти 1 и 2, либо в основную память 9 через коммутатор 6 данных. Таким образом, первым 3 и вторым 4 блоками обработки данных выполняется параллельная обработка одинаковых данных. При отсутствии неисправности триггер управления 19 может быть установлен в произвольное состояние например в единичное, при котором через коммутатор б данных разрешается прохождение информации с выхода первого блока 3 обработки данных

Предположим, что при запуске процессора (например, после включения питания) триггер управления 19 устанавливается в единичное состояние. Компаратор 5 данных сравнивает результаты обработки данных в первом 3 и втором 4 блоках обработки данных; при совпадении результатов никаких специальных действий в процессоре не предпринимается и вычисления продолжаются. Если в первом 3 или втором 4 блоке обработке данных либо в первой 1 или второй 2 локальной памяти происходит отказ, компаратор 5 данных обнаружит этот отказ из-за расхождения в результатах обработки, ртказ может быть обнаружен немедленно после его возникновения или со значительной временной задержкой. Независимо от наличия или отсутствия задержки к моменту обнаружения отказа в основной памяти 9 будут находиться корректные команды и данные, даже если триггер управления 19 в течение времени задержки установлен в состояние, соответствующее разрешению прохождения в основную память 9 информации с выхода неисправного блока. Это обусловлено тем, что компаратор 5 данных разрешает выполнять запись информации в основную память 9 только при совпадении сигналов на выходах первого 3 и второго 4 блоков обработки данных. Кроме этого, в момент обнаружения отказа исправные блок обработки данных и локальная память содержат корректную информацию, соответствующую данному моменту обработки. При срабатывании компаратора 5 данных (обнаружен отказ) для адресации микрпрограммной памяти 15 формируется начальный адрес микропрограммы обработки отказа узлом 13 формирования адреса.

Адрес микрокоманды, которая должна была выполняться следующей, если

бы отказ не был обнаружен, запоминается в регистре 14 возврата. Кроме того, в оановную память 9 выдается сигнал, временно блокирующий выполнение операции записи для Предотвращения ошибочного искажения данных в памяти. Блокировка устанавливается только в том случае, когда в последней выполненной микрокоманде была указана, микрооперация записи в основную память

10 9; она автоматически вызывает выполнение записи в основную память 9 в конце микропрограммы обработки отказа.

15

Для микропрограммы обработки отказа в памяти разгрузки 10 предусматривается три области ячеек. Первая область предназначена для сохранения адреса микрокоманды,

0 перед-выполнением которой в процессоре обнаружен отказ, а также для сохранения содержимого регистра 11 адреса. Вторая область служит для сохранения содержимого первой локальной памяти 1 и всех элементов

5 памяти первого блока 3 обработки данных. Третья область аналогична второй и используется для сохранения состояния второй локальной памяти 2 и второго блока 4 обработки

0 данных.

При выполнений микропрограммы o6pa6oTKji отказа блокируется реакция узла 13 формирования адреса на

5 сигналы с выхода компаратора 5 данных и происходит запоминание содержимого регистра 14 возврата и регистра 11 адреса в первой области памяти разгрузки 10, затем по

0 единичному состоянию триггера управления 19 во вторую область памяти разгрузки 10 переписывается информация о состоянии всех запоминающих элементов первого блока 3 обработки данных (например, выход5ной регистр блока обработки, состояние переноса, переполнения и т.п.) и содержимое первой локешьной памяти 1. После этого триггер управления 19 устанавливается в

0 нулевое состояние и в третью об ласть памяти разгрузки 10 переписывается состояние второго блока 4 обработки данных и второй локальной памяти 2. Таким образом, сос5тояние всех запоминающих элементов процессора сохраняется в памяти разгрузки 10, причем корректное состояние записано либо во вторую; либо в третью область памяти разгрузки 10, в зависимости от места

0 отказа.

Локализация места отказа выполняется микропрограммным диагностическим тестом, которому передает управление микропрогрс1мма обработки

5

отказа. Диагностический тест выполняется путем передачи тестовой информации в первую и вторую локальные памяти 1 и 2, в первый 3 и второй 4 блоки обработки данных, затем блокам обработки задается определенная функция. Результаты выполнения этой функции в первом 3 и втором 4 блоках обработки данных раздельно подаются на входы первого и второго тестовых компараторов 7 и 8. Этими компараторами действительные результаты обработки данных в блоках 3 и 4 сравниваются с ожидаемыми в результате тестирования (эталонными) / которые подготавливаются генератором эталона 20 по микрооперациям узла 16 формирования микроопераций. Результаты сравнения в первом и втором тестовых компараторах 7 и 8 накапливаются первым 17 и вторым 18 регистрами результатов теста Весь диагностический тест состоит из целого ряда тестовых проверок, результат каждой из которых фиксируется отдельным битом первого 17 и второго. 18 регистров результатов теста. После завершения выполнения микропрограммы диагностического теста по содержимому этих регистров определяется неисправный блок, а если возможно, неисправный элемент.

Для обеспечения возможности продолжить работу процессора достаточно знать только неисправный блок; локализация неисправности до уровня элементов используется для последующего ремонта оборудования. Предположим, неисправность была обнаружена в первой локальной памяти

1или в первом блоке 3 обработки данных. Микропрограмма диагностического теста в этом случае установит триггер управления 19 в нулевое состояние, сформирует в регистре 11 адреса начальный адрес третье области памяти разгрузки 10 и возвратит управление микропрограмме обработки отказа. Если отказ обнаружен во второй лока:льнойпамяти

2или во втором блоке 4 обработки данных, то управление микропрограмме обработки отказа будет возвращено, с единичным состоянием триггера управления 19 и с подготовленным в регистре 11 адреса начальным адресом второй области памяти разгрузки 10. После этого микропрограмма обработки отказа переписывает в блЬки обработки данных и в локальные памяти информацию из той област памяти разгрузки 10, начальный адрес которой установлен в регистре

11 адреса. В результате элементы памяти исправных блоков установлены в состояние, соответствующее правилно выполнявшейся обработке. Правильность установки элементов памяти неисправных блоков гарантировать

нельзя, однако в этом и нет необходимости, так как в дальнейшем в качестве истинного будет рассматриваться результат работы исправного блока. При завершении микропрограммы обработки отказа из первой области памяти разгрузки в регистр адреса 11 возвращается адрес, хранившийся там в момент обнаружения отказа, и снимается блокировка записи в основную память 9. Запись в основную память 9 выполняется только в том случае, если она была указана в микрокоманде, при выполнении которой был обнаружен отказ компаратором 5 данных. В узел 13 формирования адреса пересылается адрес микрокоманды, которая должна была выполняться после обнаружения отказа, и обработка данных продолжается с того момента, в котором она была приостановлена обработкой отказа. Реакция узла 13 формирования адреса на сигналы несоответствия с выхода компаратора 5 данных остается заблокированной до тех пор, пока отказавшее оборудование не будет отремонтировано {например, нормальная реакция на отказ может быть восстановлена выпонением после завершения ремонта операций приведения процессора в исходное состояние - сброс или сброс при включении питания). Таким же образом восстанавливается нормальная реакция на сигнал компаратора 5 данных при записи в основную память 9, т.е. блокировка записи при обнаружении компаратором 5 данных несовпадения будет выполняться только после ремонта оборудования и приведения процессора в исходное состояние. При использовании данного процессора достигаются:

-упрощение оборудования блоков обработки данных и локальных памятей, что позволяет применить для их реализации типовые средние и большие интегральные схемы;

-реализация избыточного оборудования, вводимого в процессор (память разгрузки, регистры и компараторы), на типовых микросхемах;

,- упрсхдение создания диагностичекого теста за счет ограничения функции блоков обработки данных и локалных памятей функциями обработки и хнения данных; тест может быть реализован меньшей микропрограммой,/так как уменьшено количество функций, требующих проверки, кроме этого, появляется возможность в значительной степени увеличить перечень неисправностей, обнаруживаемых тестом

Формула изобретения

Микропрограммный процессор с самодиагностикой , содержащий первую

И вторую локальные памяти, выходы которых соединены соответственно с информационными входами первого и второго блоков обработки данных, выходы которых соединены соответственно с первыми информационными входами первой и второй локальных памятей, с первыми и вторыми информационными входами коммутатора данных и компаратора данных, управляющий вход коммутатора данных соединен с выходом тригера управления, выход коммутатора данньах соединен с информационным входом основной памяти, первый управляющий вход которой соединен с первым выходом управления узла формирования микроопераций, с управляющими входами регистра адреса, первого и второго блоков обработки данных, первой и второй локальных памятей, вторые информационные входы первой и второй локальных памятей соединены с разрядным выходом регистра данных, с информационным входом регистра ещреса и с первым информационным входом узла формирования адреса, управляющий вход которого соединен со вторым выходом управления узла формирования микроопераций, вход которого соединен с выходом микропрограммной памяти, вход которой соединен с выходом узла формирования адреса, разрядный выход регистра адреса соединен с адресным входом основной памяти, выход которой соединен с первым информационным входом регистра данных, отличающийся тем, что, с целью упрощения процессора, он дополнительно содержит первый и второй тестовые компараторы, первый и второй регистры результатов тести, генератор эталона, регистр возврата и память разгрузки, к первому и второму информационным входам которой подключены соответственно выход коммутатора данных и разрядный выход регистра возврата, к сщресному и управляющему входам памяти раз груз ки подключены разрядный выход регистра адреса и первый выход управления узла формирования микроопераций соответственно, а к выходу памяти разгрузки - второй информационный вход регистра данных, третий выход управления узла формирования микроопераций соединен со входом триггера управления, выход узла формирования адреса соединен с информационным входом регистра

o возврата, выход компаратора данных подключен ко второму информационному входу узла формирования адреса, к управляющему входу регистра возврата и ко второму управля5ющему входу основной памяти, четвертый выход управления узла формирования микроопераций соединен со входом генератора эталона, выход которого подключен к первым входам

0 первого и второго тестовых компараторов, ко вторым входам которых подключены соответственно выходы первого и второго блоков обработки данных, второй вход управления узла формирования микроопераций со5единен с управлякхцими входгичи первого и второго регистров результатов теста, ,к информационным входам которых подключены соответственно выходы первого и второго тестовых

0 компараторов, а выходы первого и второго регистров результатов теста соединены соответственно с третьим и четвертым информационными входами узла формирования адреса.

5

Источники информации, принятые во внимание при экспертизе

1.Экспресс-информация, сер. Вычислительная техника, № 20, 1978, Методы автоматического воз0врата к nporpciMMe в вычислительной машине COPRA.

2.Патент США № 3848116, кл. 235-153АЕ.

3.Патент Великобритании

5

№ 1414095, кл. G 4 А (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Процессор ввода-вывода | 1979 |

|

SU798782A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

Авторы

Даты

1980-09-15—Публикация

1978-10-30—Подача