1

Изобретение относится к запоминающим устройствам и может быть использовано в аппаратуре передачи информадии.

Известны буферные запоминающие устройства с автономным контролем ij и 2.

Одно из известных устройств используется для запоминания информации, представленной в виде групп десятичных чисел, отделяемых друг от друга граничным кодом Щ.

Это устройство содержит регистры сдвига и схему управления ими. Недостатками этого устройства являются сложность схемы управления и невозможность отбраковки ошибочной информации в процессе ее считьюания.

Из известных устройств наиболее близким техническим решением к данному изобретению является буферное запоминающее устройство с автоном ным контролем, содержащее регистры сдвига, реверсивный счетчик, выходы

которого подключены ко входам дещифратсра 2.

Недостатком этого устройства является то, что оно обеспечивает считьшание только правильной (по резуль- татам контроля) информации, так как управление работой устройства осуществляется без учета контрольных сигналов. Однако практика показьтает, что информация, поступающая в аппаратуру пере10дачи данных (АПД), может содержать ошибки, обусловленные как технологическими причинами процесса ее сбора и подготовки, так и сбо51ми при вводе в АПД проконтролированной информации.

Таким образом, в канал наряду с правильной поступает и ошибочная информация, что снижает достоверность передаваемой информации. Кроме того, известное устройство можно использовать

20 в качестве буферного устройства только цля последовательно поступающей информации. В случаях, когда информация поступает в параллельном виде, что при

ередаче данных наиболее часто имеет есто, необходимо соответствующее увеичение объема аппаратуры. Указанные едостатки снижают надежность устройста.

Цель изобретения - повышение наежности устройства.

Указанная дель достигается тем, что устройство содержит дополнительный дешифратор и коммутаторы, причем нформационные входы первого коммутатора входы доиолнительного дешифратора подключены к выходам соответствующих регистров сдвига, вьйсод дополнительного дешифратора соединен с одним из входов реверсивного счетчика и первым управл5пощим входом первого коммутатора, второй управляющий вход которого подключен к выходу дешифратора состояния реверсивного счетчика и одному на входов второго коммутатора, другие входы которого соединены с одним из : входов устройства, а выход - с управляющими входами регистров сдвига.

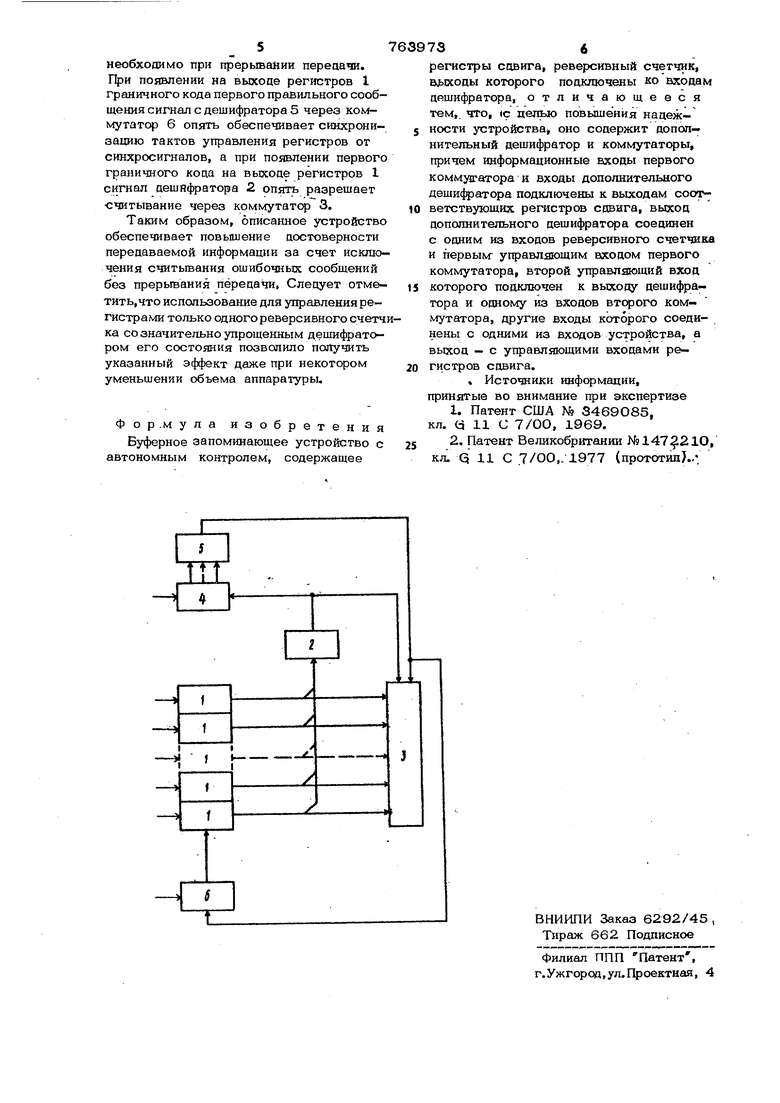

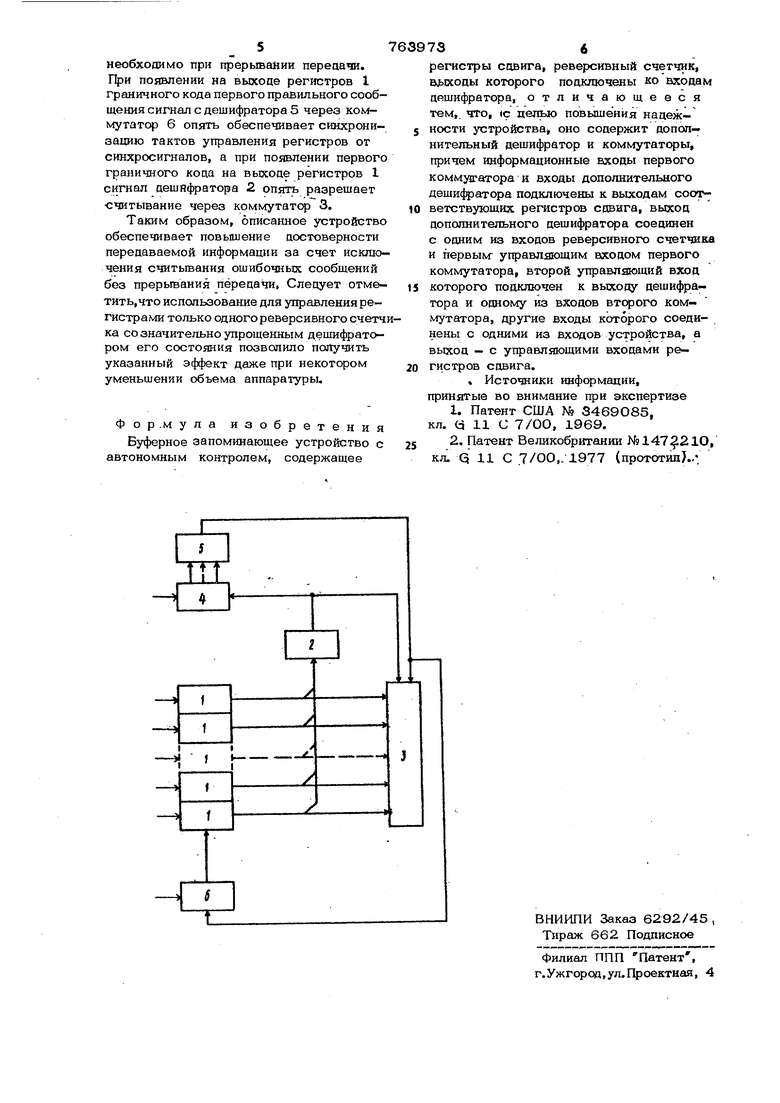

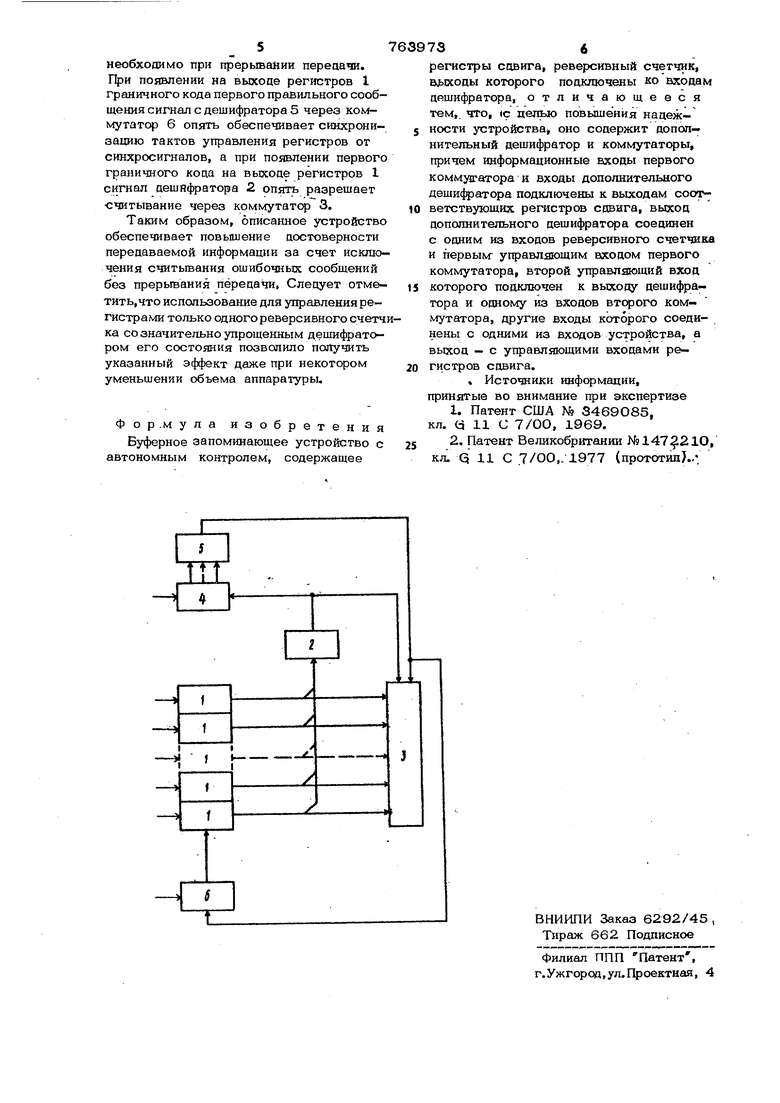

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит регистры сдвига 1, информахшонные входы дсоторых являются входами устройства, а выходы соединены с входами дополнительного дешифратора 2, служащего для опреде-. ления комб1шации граничного кода, и первого коммутатфа 3.

. Выход дешифратора 2 подключен ко входу считывания реверсивного счетчика 4 и к первому управляющему входу коммутатора 3. Вход записи реверсивного счетчика 4 является контрольным входом устройства, а выходы соединены с входами дешифратора 5, служащего для дешифрации нулевого состояния реверсивного счетчика. Выход дешифратора подключен ко второму входу коммутатора 3 и входу управления второго коммутатора 6. Выход коммутатора 6 соединен с управляющими входами регистров сдвига -1, а два других входа соединены с входами устройства.

Устройство работает следующим образом. В исходном состоянии реверсивный счетчик 4 и регистры сдвига 1 установлены в нулевое положение, а коммутатор 6 обеспечивает синхронизацию тактов управления регистрами 1 от сигналов устройства считьтания информации (не показано). С выходов регистров сдвига I через коммутатор 3 считывается код Пусто.

Информация от устройства считьюания, начиная с граничного кода, поразрядно записьтается в регистры сдвига I, первый разряд - в первый регистр, второй

разряд - во второй регистр и т.д. В момент появления второго граничного ко- да, который свидетельствует о конце первого сообщения, при условии правильности записанной в регистры эа

это время информации, на вход реверсивного счетчика 4 из контрольного устройства (не показано) поступает сигнал, записывающий в .него единицу. С приходом граничного кода после

каждого следующего правильного сообщения содержимое реверсивного счетчика 4 увеличивается на единицу. В случае обнаружения ошибки появление граничного кода не сопровождается сигнаfiofys из контрольного устройства, т.е. содержимое реверсивного счетчика 4 не изменяется:.

После заполнения регистров сдвига 1 на их вьсходах появляется граничный

код, что фиксируется дешифратором 2, сигнал с которого поступает на вход считывания реверсивного счетчика 4, уменьшая его содержимое на единицу, и подтверждает разрешение считьшания

информации из регистров через коммутатор 3 в АПД. Таким образом, содержимое реверсивного счетчика 4 соответствует количеству правильных сообщений в регистрах сдвига 1, еще не

считанных в АПД.

В случае записи в регистры сдвига 1 сообщения, содержащего ошибку, после считывания из них в АПД последнего правильного сообщения реверсивный счетчик 4 окажется в нулевом состоянии.

При этом сигнал с дешифратора 5 , поступит на вход коммутатора 3, который с этого момента выдает в АПД служебный код Ожидание , позволяющий не прерывать передачу, т.е. исключает повторение процедуры вхождения в связь после устранения обнаруженной ощнбки (вызов абонента, фазирование и т.д.). Кроме того, так как ь момент обнаружения ошибки производится останов устройства считывания, этот же сигнал через коммутатор б обеспечивает синхронизацию тактов управления регистрами от сигналов АПД.

После устранения ошибки информация вновь вводится в регистры сдвига 1, начиная с забракованного сообщения, а не с начала массива, что было бы необходимо при прерьтайии передачи. Г)и появлении на выходе регистров I граничного кода первого правильного сообщения сигнал с дешифратора 5 через коммутатор 6 onsTTb обеспечивает синхрони зацию тактов управления регистров от синхросигналов, а при появлении первого граничного кода на выходе регистров I сигнал дешифратора 2 опять разрешает считывание через коммутатор 3. Таким образом, описанное устройство обеспечивает повышение достоверности передаваемой информации за счет исключения считьюания ошибочных сообщений без прерьтания передачи. Следует отметить, что использование для управления регистрами только одного реверсивного счетч ка со значительно упрощенным дешифратором его состояния позволило получить указанный эффект даже при некотором уменьшении объема аппаратуры. Фор.мула изобретения Буферное запоминающее устройство с автономным контролем, содержащее 736 регистры сдвига, реверсивный счетчик, в IXOдьc которого подключены ко входам дешифратора, отличающееся тем, что, (С делъю повышения надежности устройства оно содержит дополнительный дешифратор и коммутаторы, причем информационные входы первого комментатора и входы дополнительного дешифратора подключены к выходам соот ветствующих регистров сдвига, выход дополнительного дешифратора соединен с одним из входов реверсивного счетчика и первым управляющим входом первого коммутатора, второй управляющий вход которого подключен к выходу дешифратора и одному из входов второго коммутатора, другие входы которого соединены с одними из входов устройства, а выход - с управляющими входами регистров сдвига. . Источники информации, ринятые во внимание при экспертизе 1. Патент США N9 3469О85 л. (а Ц С 7/00, 1969. 2. Патент Великобритании N9147: 21О, кл. Q Ц С .7/00,. 1977 (прототип)...

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1979 |

|

SU841038A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU985787A1 |

| Устройство для контроля информации | 1983 |

|

SU1174928A2 |

| Устройство для считывания графической информации | 1980 |

|

SU932519A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

Авторы

Даты

1980-09-15—Публикация

1978-01-03—Подача