Изобретение относится к вычислительноя технике и может быть использовано при построении буферных запоминающих устройств, работающих по принципу Стек или по принципу Очередь.

Известно буферное запоминающее устройство с самоконтролем, содержащее регистр адреса, накопитель, регистр числа, блок контроля, дополнительный регистр, коммутатор, счетчик, дополнительный накопитель, дешифратор, блок управления, формирватель кодов, шины адреса, вход устройства, выходную шину 1.

Недостатком этого устройства является наличие дополнительного накопителя, а также сложность.

Наиболее близким к изобретению по технической сущности является буферное запоминающее устройство с самоконтролем, содержащее блок памяти, датчик кода адреса, к выходам которого подключены входы дешифратора, регистры, связанные соответственно с входом и выходом памяти, причем выходы регистров подсоединены к входам блока обнаружения неисправных ячеек памяти, выход которого подключен к входу датчика кода адреса 2.

Недостатком известного устройств является низкая надежность вследствие того, что ойо требует записи в неисправную ячейку кода пробела, чтобы при считывании пропустить ее. В результате комбинация пробела исключается из возможных и при считывании может появиться несоответствие между адресом выбррки и адресом, по которому записана инфор-. мация.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в буферное запоминаняцее устройство с самоконтролем, содержащее накопитель, адресные входы которого подключены к выходам счет.4ика,- а выходы соединены с входами выходного регистра, и формирователь сигналов считывания, вход которого является входом считывания устройства, введены формирователь единичных сигналов, формирователь нулевых сигналов, формирователи управляющих сигналов, элемент ИЛИ, переключатель, дешифраторы и формирователь сигналов ошибки, причем первый и второй входы переключателя соединены соответственно с выходом формирователя единичных сигналов и с выходом формирователя нулевых сигналов, а выходы подключены к информационным входам накопителя, одни из выходов формирователей уп1 аш1Л ощих сигналов соединены соответственно с входами управления записью накпителя, с первым входом элемента ИЛИ-, с управляю1цим входом формирователя сигналов ошибки и с третьим входом переключателя и управляювшми входами первого и второго дешифраторов, информационные входы которых подключены к выходам накопителя а выходы - к входам формирователя сигналов ошибки, выход которого соединен с первыми входами формирователей управляющих сигналов, управляющим входом формирователя сигналов считывания и вторым входом элемента ИЛИ, выход которого подключен к входу счетчика, а третий вход элемента ИЛИ - к тактовому выходу формирователя сигналов считывания, информационный выход которого соединен с управляющим входом выходного регистра и вторыми входами форQ мирователей управляющих сигналов, третий вход и другие выходы которых являются соответственно управляющими входом и выходом разрешения записи устройства, информационными входом и выходом разрешения считывания которого являются соответственно четвертый вход переключателя и управляющий выход формирователя сигналов считывания.

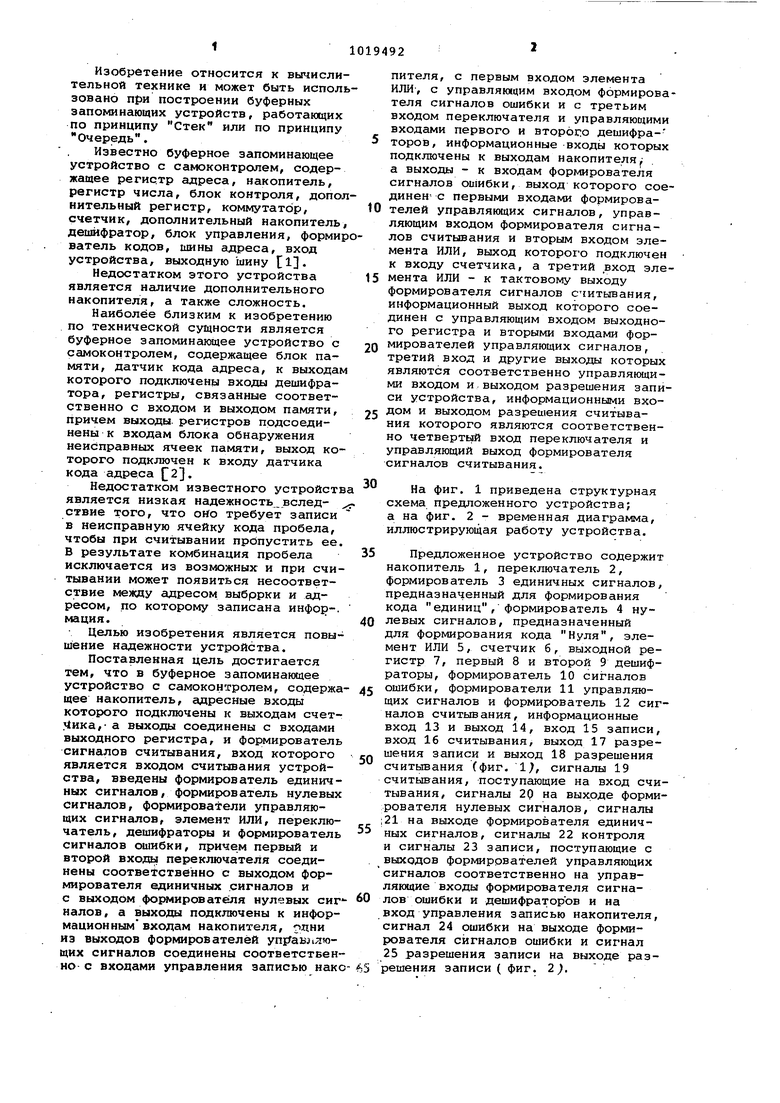

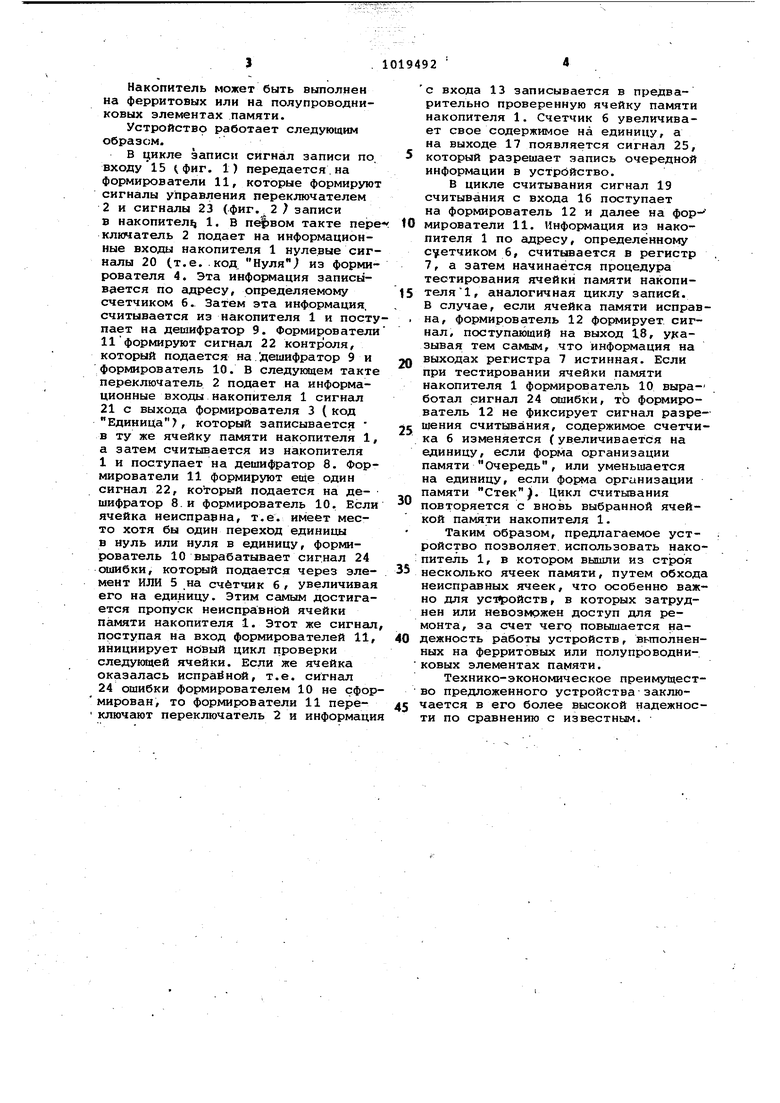

На фиг. 1 приведена структурная схема предложенного устройства; а на фиг. 2 - временная диаграмма, иллюстрирующая работу устройства.

5 Предложенное устройство содержит накопитель 1, переключатель 2, формирователь 3 единичных сигналов, предназначенный для формирования кода единиц, формирователь 4 нулевых сигналов, предназначенный для формирования кода Нуля, элемент ИЛИ 5, счетчик б, выходной регистр 7, первый 8 и второй 9 дешифраторы, формирователь 10 сигналов

С ошибки, формирователи 11 управляющих сигналов и формирователь 12 сигналов считывания, информационные вход 13 и выход 14, вход 15 записи, вход 16 считывания, выход 17 разрешения записи и выход 18 разрешения считывания (фиг. 17, сигналы 19 считывания, поступающие на вход считывания, сигналы 2Q на выходе формирователя нулевых сигналов, сигналы ;21 на выходе формирователя единичных сигналов, сигналы 22 контроля и сигналы 23 записи, поступающие с выходов формирователей управляющих сигналов соответственно на управляющие входы формирователя сигналов ошибки и дешифраторов и на

вход управления записью накопителя, сигнал 24 ошибки на выходе формирователя сигналов ошибки и сигнал 25 разрешения записи на выходе разрешения записи ( фиг. 2).

Накопитель может быть выполнен на ферритовых нли на полупроводниковых элементах памяти.

Устройство работает следующим образом.

В цикле записи сигнал записи по, входу15 фиг. 1) передается.на формирователи 11, которые формируют сигналы управления переключателем 2 и сигналы 23 (фиг.2 ) записи в накопителе 1, В первом такте nepe клкнатель 2 подает на информационные входы накопителя 1 нулевые сигналы 20 (т.е. код. Нуля) из формирователя 4. Эта информация записывается по адресу, определяемому счетчиком 6. Затем эта информация, считывается из накопителя 1 и поступает на дешифратор 9. Формирователи 11формируют сигнал 22 контроля, который подается на дешифратор 9 и формирователь 10. В следуквдем такте переключатель 2 подает на информационные входы накопителя 1 сигнал 21 с выхода формирователя 3 ( код Единица, который записывается в ту же ячейку памяти накопителя 1, а затем считывается из накопителя 1 и поступает на дешифратор 8. Формирователи 11 формируют еще один сигнал 22, который подается на дешифратор 8.и формирователь 10. Если ячейка неисправна, т.е. имеет место хотя бы один переход единицы в нуль или нуля в единицу, формирователь 10 вырабатывает сигнал 24 ошибки, который подается через элемент ИЛИ 5 на счётчик б , увеличивая его на единицу. Этим самым достигается пропуск неисправной ячейки памяти накопителя 1. Этот же сигнал поступая на вход формирователей 11, инициирует нбвый цикл проверки следунлцей ячейки. Если же ячейка оказалась испрайной, т.е. сигнал 24 ошибки формирователем 10 не сформирован, то формирователи 11 переключают переключатель 2 и информаци

с входа 13 записывается в предварительно проверенную ячейку памяти накопителя 1. Счетчик 6 увеличивает свое содержимое на единицу, а на выходе 17 появляется сигнал 25, 5 который разрешает запись очередной информации в устройство.

В цикле считывания сигнал 19 считывания с входа 16 поступает на формирователь 12 и далее на форo мироватеЛи 11. Инфоря ация из накопителя 1 по адресу, определённому сметчиком 6, считывается в регистр 7, а затем начинается процедура тестирования ячейки памяти накопи5 , аналогичная циклу записи.

В случае, если ячейка памяти исправ, на, формирователь 12 формирует сигнал, поступающий на выход 18, указывая тем самым, что информация на выходах регистра 7 истинная. Если

0 при тестировании ячейки памяти накопителя 1 формирователь 10 выработал сигнал 24 ошибки, то формирователь 12 не фиксирует сигнал разрешения считывания, содержимое счетчика 6 изменяется (увеличивает ся на единицу, если форма организации памяти Очередь, или уменьшается на единицу, если форма организации памяти Стек). Цикл считывания

0 повторяется с вновь выбранной ячейкой памяти накопителя 1.

Таким образом, предлагаемое устройство позволяет, использовать накопитель 1, в котором вышли из строя

5 несколько ячеек памяти, путем обхода неисправных ячеек, что особенно важно для устройств, в которых затруднен или невозможен доступ для ремонта, за счет чего повышается на0дежность работы устройств, вьтолненных на ферритовых или полупроводниковых элементах памяти.

Технико-экономическое преимущество предложенного устройствазаключается в его более высокой надежнос5ти по сравнению с известным.

гг

п

п п

IIп п п п

ги

д

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтро-лЕМ | 1979 |

|

SU842980A1 |

| Устройство для контроля оперативной памяти | 1985 |

|

SU1302325A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920848A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| Запоминающее устройство с контролем информации при записи | 1981 |

|

SU1003151A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее иакопитель, адресные входы которого подключены к выходам счётчика, a выходы соединены с входами выходного -регистра, и формирователь сигналов считывания, вход которого является входом считывания устройства, отличающееся тем, что, с целью повшаения надежности устройства, в него введены формирователь.единичных сигналов, формирователь нулевых сигналов, формирователи управляющих сигналов, элемент ИЛИ, переключатель, дешифраторы и формирователь сигналов ошибки, причем первый и второй входы переключателя соединены соответственно с выходом фо{Як ирователя единичных сигнсшов и с выходом формирователя нулевых сигналов, a выходы подключены к информационным входам накопителя, одни из выходов формирователей управляющих сигналов соединены соответственно с входами управления записью накопителя, с первым входрм элемента ИЛИ, с управляющим входом формирователя сигналов сяйибки и с третьим входом переключателя и управляющими входами первого и второго дешифраторов, информационные входы которых подключены к выходам накопителя, a выходы - к входам формирователя сигналов ошибки, выход которого соединен с первыми входами формирователей управляющих сигналов, управляющим входом формирователя сигналов считывания и вторым входом элемента ИЛИ, выход которого подключен к входу счетчика, a третий вход элемента ИЛИ - к тактовому выходу формирователя сигналов считывания, информационный выход которого соединен с управляющим входом выходного регистра и вторыми входами формирователей управлян5щих сигналов, третий вход и другие выходы которых являются соответственно управляющими входом и выходом разСО решения записи устройства, инфор4 мационными входом и выходом разрешения считывания которого являются соответственно четвертый вход переключателя и управляющий выход формирователя сигналов считьюания.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU367460A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-05-23—Публикация

1982-01-05—Подача