(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство с автономным контролем | 1978 |

|

SU763973A1 |

| Устройство формирования зон при записи цифровой информации на магнитный носитель | 1981 |

|

SU959149A1 |

| Устройство передачи и приема сигналов телеинформации | 1978 |

|

SU698032A1 |

| Устройство для передачи ипРиЕМА диСКРЕТНОй иНфОРМАциипО пАРАллЕльНыМ КАНАлАМ СВязипЕРЕМЕННОй длиНы | 1978 |

|

SU794753A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в аппаратуре подготовки и обработки цифровой информации. Известно устройство, которое использует ся для запоминания информации, представленной в виде групп, отделяемых друг от друга граничным кодом. Устройство содержит регистры и схемы управления ими 1. Недостатком этого устройства является невозможность отбраковки ошибочной информации в процессе ее выхода из накопителя. Наиболее близким к изобретению по технической сущности является буферное запоминающее устройство, содержащее регистры сдвига, дешифратор фаничного кода, логический коммутатор, реверсивный счетчик и дешифратор нулевого состояния реверсивного счетчика (2). Однако устройство при обнаружении ошибочной информации требует обязательной остановки ее ввода и коррекции ошибочного сообщения. В то же время на практике коррекция ошибочной информации часто производится таким образом, что забракованные сообщения уже в откорректированном виде повторяются в конце обрабатываемого массива информации, а сами ошибочные сообщения внутри массива не коррек-. тируются. При этом значительно упрощается технология обработки информации, так как. исключается необходимость проведения резки, склейки и ручной коррекции технического носителя. В этом случае устройство, хотя и обеспечивает вывод только правильных сообщений, но так как алгоритм его работы предусматривает обязательную остановку устройства на всех ошибочных сообщениях и возможность возобновления работы только после коррекции ошибок, то при этом существенно ограничивается скорость вывода информации. Указанный недостаток приобретает особое значение в случаях, когда скорость вывода информации из устройства значительно превышает скорость ввода, например в случаях, когда потребителем информации яв.Ляется не аппаратура передачи данных (АПД), а ЭВМ, что характерно для автоматизированных систем обработки информации. При этом прерывание вывода информации во время остановок на ощибочных сообщепнях сушсствсмпю снижает быстродействие исой сисюмы..

Цель пзобретекия -- noBbiuieiine быстродействия устройства.

Поставленная цель достигается тем, что U буцЬерное запоминающее устройство, содержанхее регистра сдвига, блок регистров сдвига, коммутатор информационных сигналов и коммугатор тактовых сигналов, причем выходы блока регисгров сдвига цодключены к входам коммутатора информационных сигналов, выходы которого являются выходами устройства, управляющий вход блока регистров сдвига соединен с выходом комл утатора тактовых сигналов, входы регистра сдвига являются входами устройства, вве;1епы группа э;1ел ептов И и элементы ИЛИ, MIZ и И, причем П1(|)0рмап,ионные входы элементов И гру|нпл подключены к выходам регистра сдвнга, управляющие входы - к первому управляющему входу устройства и первому входу первого элемента И, а выходы - к входам блока регистра сдвига, первый вход второго элемента И соединен с входом элемента НЕ и выходом элемента ИЛИ, входы которого подключены к выходам блока регистров сдвига, выходы первого н второго элементов И подключены соответственно к унравляюш.им входам регистра сдвига и коммутатора информационных сигпалов, вторые входы второго и первого элементов И соединены соответственно с вторым управляющим входом устройства и выходом, коммутатора тактовых сигналов, один из входов которого соедине с выходом эл-емента ИЕ, а другие - соответственно с первым, третьим и четвертым входами устройства.

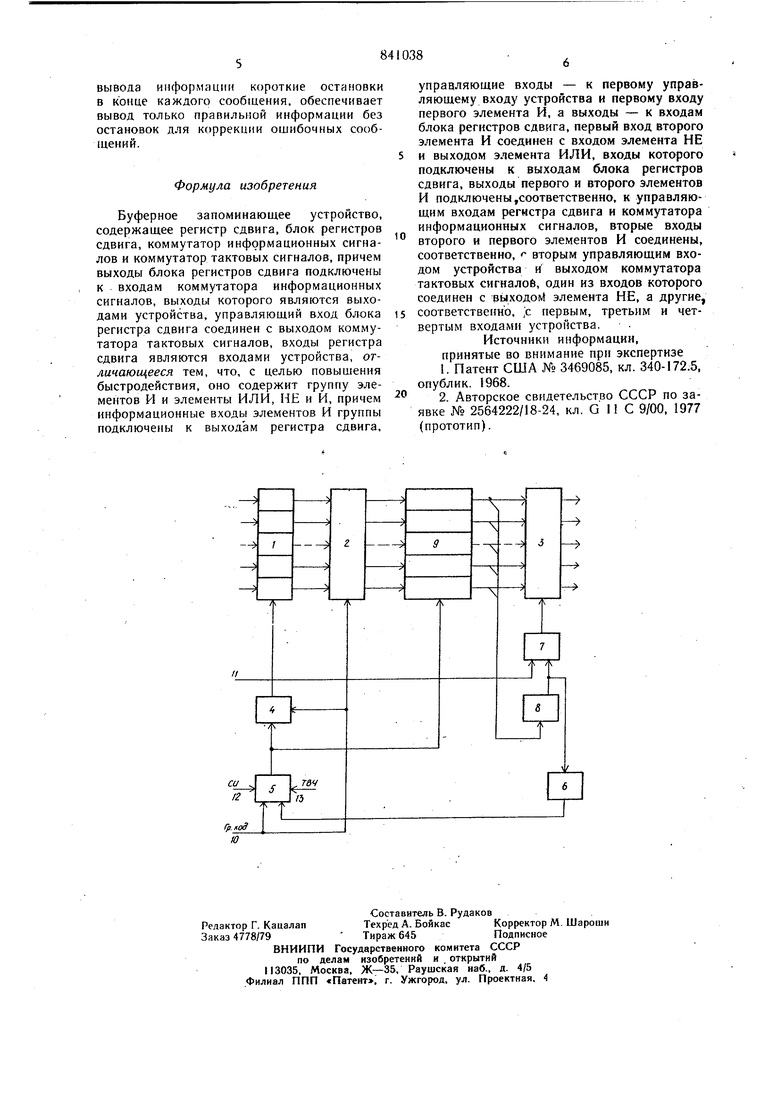

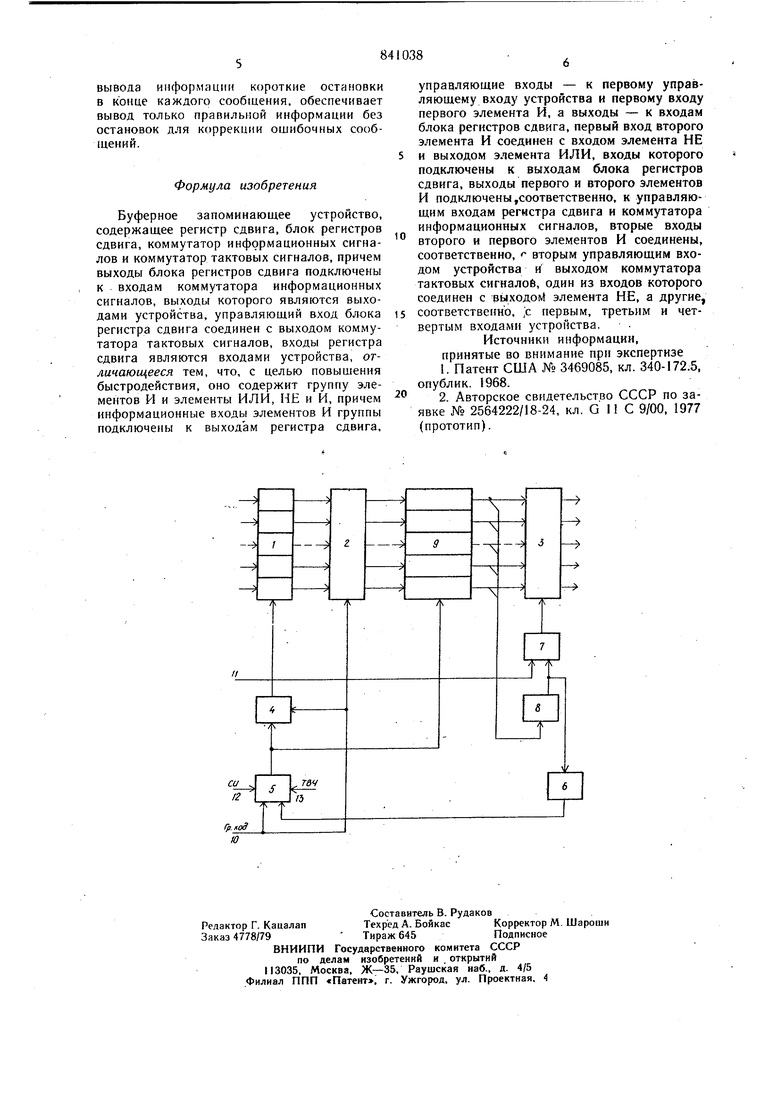

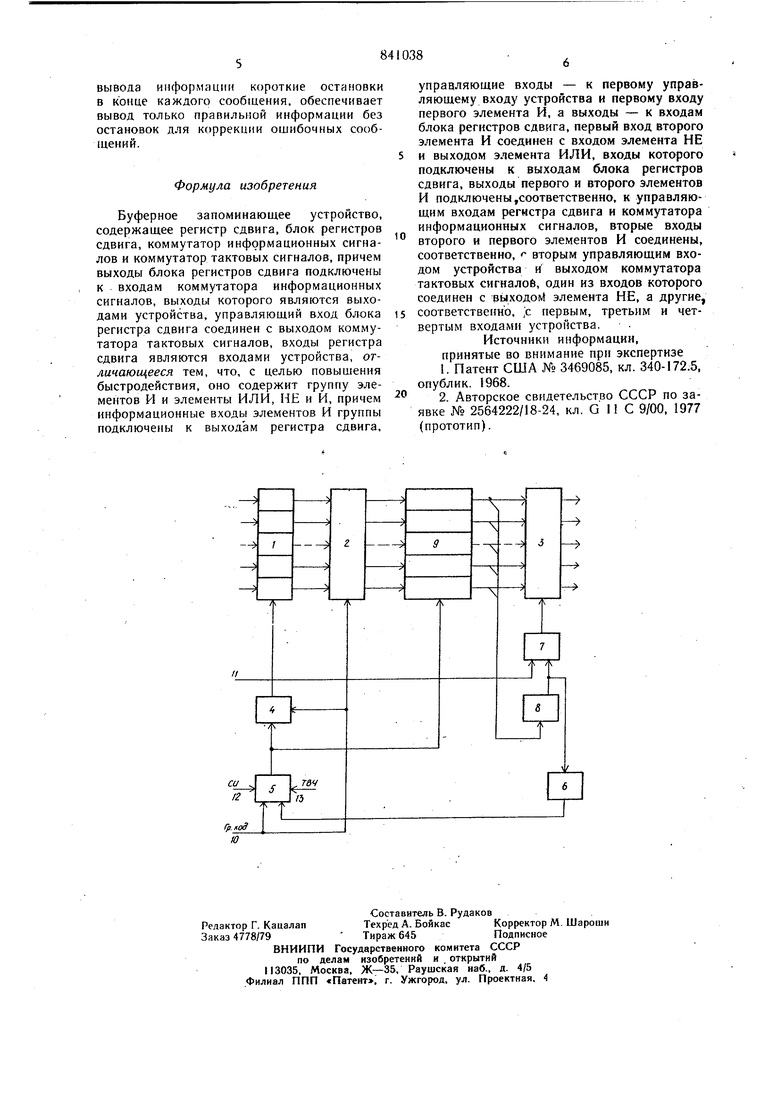

На чертеже представлена структурная схема буферного запоминающего устройства. Устройство содержит регистр 1 сдвига, группу элементов 2 И, коммутатор 3 информационных сигналов, первый элемент 4 И коммутатор 5 тактовых сигналов, элемент 6 НЕ, второй элемент 7 И, элемент 8 ИЛИ и блок 9 регистров сдвнга, представляю иди и последовательно соединенные регистры сдвига.

Информационные входы элементов 2 И цодключены к выходам регистра 1 сдвига, управляющие входы - к первому управляющему входу 10. устройства и первому входу элемента 4 И, а выходы - к входам.блока 9. Первый вход элемента 7 И соединен с входом элемента 6 НЕ и выходом элемента 8 ИЛИ, входы которого цодключены к выходам блока 9. Выходы элементов 4 и 7 И подключены соответственно к управляющим входам регистра 1 и коммутатора 3. Вторые входы элементов 7 и 4 И соединены соответственно с вторым управляющим входом 11 устройства и выходом коммутатора 5, один из входов которого соединен с выходом элемента 6 НЕ, а другие - соответственно с первым 10, третьим 12 и четвертым 13 входами устройства.

ГЗуферное запоминающее устройство работает следующим образом.

В исходном состоянии регистры 1 -и 9 сдвига установлены в нулевое положение, а коммутатор 5 обеспечивает синхроцизацию

тактов управления всеми разрядами регистров от сигналов устройства ввода информации, поступающими на вход 12 (синхроимпульсы СИ). Коммутатор 3 запрещает вывод информации, элементы 2 И открыты. Информация от устройства считывания, начиная с граничного кода, поразрядно записывается врегистр 1 сдвига. В момент появления второго граничного кода, который свидетельствует о конце первого сообщения, производится переключение тактов управлепия. Ири этом подача тактов управления ца первые разряды регистров 1 и 9 сдвига запрещается элементом 4 И, элементы 2 И закрываются, а синхронизация тактов управления осуществляется от сигналов устройства вывода информации, поступающих

на вход 13 (синхросимволы ТВЧ) через коммутатор 5. При этом ввод нового сообщения в регистры 1 и 9 сдвига прекращается, а записанное сообщение продвигается по регистрам 1 и 9 сдвига тактами ТВЧ ив момент появления ца их выходе граничного

кода элемент 8 ИЛИ вырабатывает сигнал, по которому разрещается вывод информации через-коммутатор 3. Действие этого сигнала продолжается до тех пор, пока хотя бы на одном из выходов регистров и 9 при0 сутствует единичный потенциал, что свидетельствует о наличии в них информации. В момент, когда на всех выходах регистров 1 и 9 устанавливаются нулевые потенциалы (информации нет.), действие сигнала на выходе элемента 8 ИЛИ прекращается и

5 через элемент 6 НЕ производится переключение тактов управления от ТВЧ к СИ. В этот же.момент прекращается действие сигнала иа входе 10, т. е. сигнала граничного .кода устройства, и устройство принимает исходное состояние., В случае отсутствия

ошибочных сообщений процесс ввода-вывода информации через устройство цовторяется аналогично оцисанному.

В случае обнаружения ошибочного сообщения в момент появления сигнала на входе 10 устройства по другому его входу II поступает сигнал, который с помощью элемента 7 И запрещает прохождение разрещающего сигнала с выхода элемента 8 ИЛИ на вход коммутатора 3, а следовательно,

0 и в эfвoд ошибочного сообщения из устройства. Ощибочное сообщение выводится из регистров f и 9 сдвига, но к потребителю не поступает. В момент окончания вывода его из регистров 1 и 9 сигналом с выхода элемента 8 ИЛИ через элемент 6 НЕ про5 изводится переключение тактов управления

и устройство принимает исходное состояние.

Таким образом, предлагаемое буферное

запоминающее устройство, используя для вывода информации короткие остановки в конце каждого сообщения, обеспечивает вывод только правильной информации без остановок для коррекции ошибочных сообщений. Формула изобретения Буферное запоминающее устройство, содержащее регистр сдвига, блок регистров сдвига, коммутатор информационных сигналов и коммутатор тактовых сигналов, причем выходы блока регистров сдвига подключены к входам коммутатора информационных сигналов, выходы которого являются выходами устройства, управляющий вход блока регистра сдвига соединен с выходом коммутатора тактовых сигналов, входы регистра сдвига являются входами устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит группу элементов И и элементы ИЛИ, НЕ и И, причем информационные входы элементов И группы подключены к выходам регистра сдвига.

Гр.код управляющие входы - к первому управляющему входу устройства и первому входу первого элемента И, а выходы - к входам блока регистров сдвига, первый вход второго элемента И соединен с входом элемента НЕ и выходом элемента ИЛИ, входы которого подключены к выходам блока регистров сдвига, выходы первого и второго элементов И подключены,соответственно, к управляющим входам регистра сдвига и коммутатора информационных сигналов, вторые входы второго и первого элементов И соединены, соответственно, - вторым управляющим входом устройства и выходом коммутатора тактовых сигналов, один из входов которого соединен с выходол элемента НЕ, а другие, соответственно, ,с первым, третьим и четвертым входами устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3469085, кл. 340-172.5, опублик. 1968. 2.Авторское свидетельство СССР по заявке № 2564222/18-24, кл. G II С 9/00, 1977 (прототип).

Авторы

Даты

1981-06-23—Публикация

1979-10-30—Подача