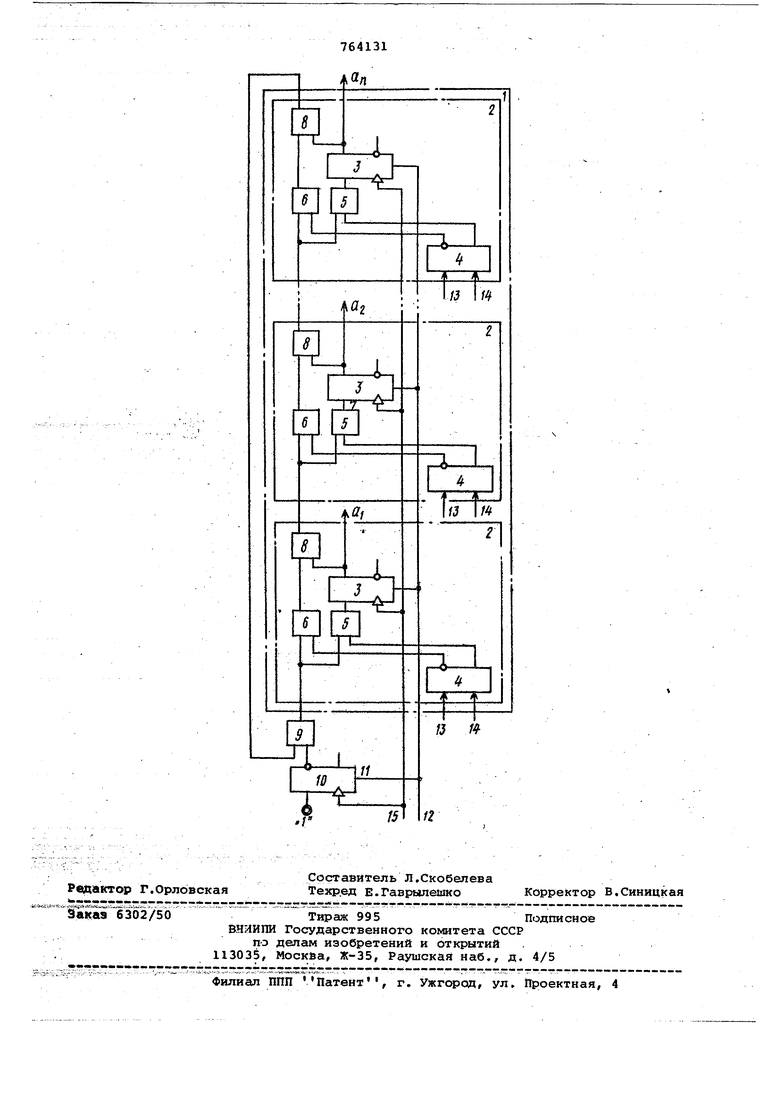

764131 второго элементов И, выход первого элемента И подсоединен к синхронному информационному-входу основного триггера, выход второго элемента И к одному из входов элемента ИЛИ, .второй вход которого подсоединен к единичному выходу основного триггера, а выход - ко вторым входам первого и второго элементов И следующег разряда, причем выход элемента ИЛИ Последнего разряда подключен ко вторым входам первого и второго элементов И первого разряда через общий элемент ИЛИ, введен триггер начальной установки, нулевой выход которого соединен со вторым входом общего элемента ИЛИ, синхронный информационнЫй вход - с шиной логической асинхронные входы установки основных Триггеров всех разрядов.и триггера начальной установки соединены с шиной сигнала установки. На чертеже представлена структурная cxjsMa многоканального коммутатора с переменным циклом опроса.. Многоканальный коммутатор с пере менным циклом опроса содержит п разрядный регистр 1, каждый разряд 2 которого сострит из основного триггера 3, управляющего триггера 4 элементов И 5, б, первые BtSxe f ifcot рых соединены соответственно ничным и нулевым выходами триггера выход элемента И 5 соединен С синх зЭнным информационным ёходом 7 триг гера 3, а выход элемента И 6 - с входом элемента ИЛИ 8, второй вход которого подключен к единичному выходу триггера 3. Выход элемента 8 ;. соединен со вторыми входами элементов И 5 и б следующего разряда, причем выход элемента 8 последнего п-го разряда соединен со вторыми Входами элемёнтов И 5 и б первого разряда через элемент ИЛИ 9, второй вход которого подключен к нулев0141у выходу триггера ДО начальной устанб кй. Триггер 10 однотипен .с триггера ми 3 каждого разряда, на его синхрЪ ный информационный вход постоянно п редается логическая а асинхронный вход 11 устанозвки в 6 со с аналогичными входа:Ми±Щр геров 3 всех разрядов и шиной 12 си нала установки. Ко входам 13 и 14 .управляющих триггеров 4 подключены ходы схемы управления этими триггерами, не представленной на-чё$ тШё; Поскольку в данном устройстве в ка.честве основных триггеров и рй1 гёра йа1чальной установкниСПойь ййёя триггеры потенциально-и шульсного типа, то осуществляется однотактная система синхронизации тактовыми импульсами, поступающими по шине 15. Йыходами разрядов коммутатора являйтЬяёдйнйчные выходы триггеров 3. Устройство работает следующим образ ом ---..-.-..-. Пусть нуждс1ются в опросе все п каналов коммутатора, т.е. все триг,геры 4 в состоянии . После включения устройства и прихода сигнала установки (от схемы управления, от кнопки или любого другого устройства) все основные триггеры 3 разрядов устанавливаются в О, что соответствует запрету опроса всех разрядов KdMMyl:aToi a. Триггер 10 начальной установки также устанавливается в 0 . Уровень логической с нулевого выхода триггера 10 через элемент ИЛИ 9 и элемент И 5 первого разряда, на второй вход которого с триггера 4 поступает разрииающий уровень , подается на вход 7 триггера 3 первого разряда. Элементы И 6 всех разрядов заперты уровнем логического О с нулевых выходов триггеров 4, поэтому на входы 7 триггеров 3 всех остальных разрядов поступает уровень окончания длительности начального сигнала все триггеры 3 и триггер 10 удерживается в состоянии О, коммутатор находится в исходном.состоянии. По окончании сигнала со всех триггеров 3 и триггера 10 снимается сигнал установки, и по фронту первого же тактового импульса триггер 10 и триггер 3 первого разряда устанавливаются в состояние , а в триггеры 3 всех остальных разрядов заносится О, что соответствует сое- тЪянию опроса первого канала. Уровень логического О с нуп.ев,рго выхода Триггера 10 разрешает теперь прохождение через элемейт ИЛИ 9 выходного сигнала элемента ИЛИ 8 последнего разряда, т.е, уровень через элемент ИЛИ 3 и элемент или 5 поступает на вход 7 триггера 3 первого разряда. Уровень с выхода триггера 3 первого разряда через элемент ИЛИ 8 первого разряда и элемент И 5 второго разряда поступает на вйЬд 7 триггера 3 второго разряда. На входах 7 всех остальных триггеров 3 сохраняется уровень О. По приходу второго тактбвЬго импульса в 1 устанавливается только триггер 3 второго разряда, что соответствует состоянию опроса второго канала. Осуществляется подготовка к установке в триггера третьего разряда и т.д. Пусть Запрещен опрос одного или нескольких каналов, например второго и третьего. Триггеры 4 этих разрядов устанавливаются в состояние О По приходу сигнала, как и в предыдущем случае, триггеры 3 и триггер 10 устанавливаются в исходное состояние, подготавливая установление по первому тактовому и «1ульсу триггера 3 первого разряда в . Выходные уровни триггеров 4 второго и третьего разрядов запрещают прохождение сигналов с выхода элемента ИЛИ 8 первого разряда на входы 7 триггеров 3 этих разрядов, поддерживая на них постоянный уровень логического О , и раэрешают прохождение сигналов черезэлементы И 6 и ИЛИ 8 запрещенных разрядов и элемент И 5 четвертого разряда на вход 7 триггера 3 четвертого разряда. После прихода второго тактового кютульса

логическая

переносится с выхода триггера 3 первого разряда в триггер 3 четвертого разряда, во все остальные триггеры 3 заносится логический О, т.е. коммутатор из состояния опроса первого канала переходит сразу в состояние четвертого канала, пропуская состояния опроса второго и третьего каналов.

Формула изобретения

Многокйнальный коммутатор с переменным циклом опроса, содержащий п-раэрядный регистр, каждый разря,ц которого состоит из основного и управляющего триггеров, элемента ИЛИ, первого и второго элементов И, при этом единичный и нулевой выходы управляющего триггера подключены к

первым входам соответственно перврго и второго элементов И, выход первого элемента И соединен с синхронным информационным взводом основного триггера, выход второго элемента И с одним иЭ входов элемента ИЛИ, второй вход которого соединен с единичным выходом основного триггера, а выход - со вторыми входами первого и второго элементов И следующего разряда, причем выхрд элемента ИЛИ последнего раз0ряда подключен ко вторым входам первого и второго элементов И первого разряда через оШий элемент ИЛИ, отличающийся тем,что,с целью повышения надежности работы комму5татора, в него введен триггер начгшьной установки,нулевой выход которого соединен со вторым входом общего . элемента ИЛИ, а синхронный информационный вход - с шиной логической , асинхронные входы установки

0 основных триггеров всех разрядов и триггера начальной установки соединены с шиной сигнала установки.

Источники информации, принятые во внимание при экспертизе

5

1.Авторское свидетельство СССР

I 512578, МКИ Н 03 К 17/02, 30.03.77.

2.Авторское свидетельство СССР

375789, МКИ Н 03 К 17/00, 23.03.73 (прототип).

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для диагностирования шин | 1987 |

|

SU1444640A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для ввода информации | 1988 |

|

SU1539763A1 |

| Адаптивный коммутатор | 1985 |

|

SU1248046A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1483639A1 |

| Устройство для контроля блоков отображения | 1985 |

|

SU1264187A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

Авторы

Даты

1980-09-15—Публикация

1978-07-03—Подача