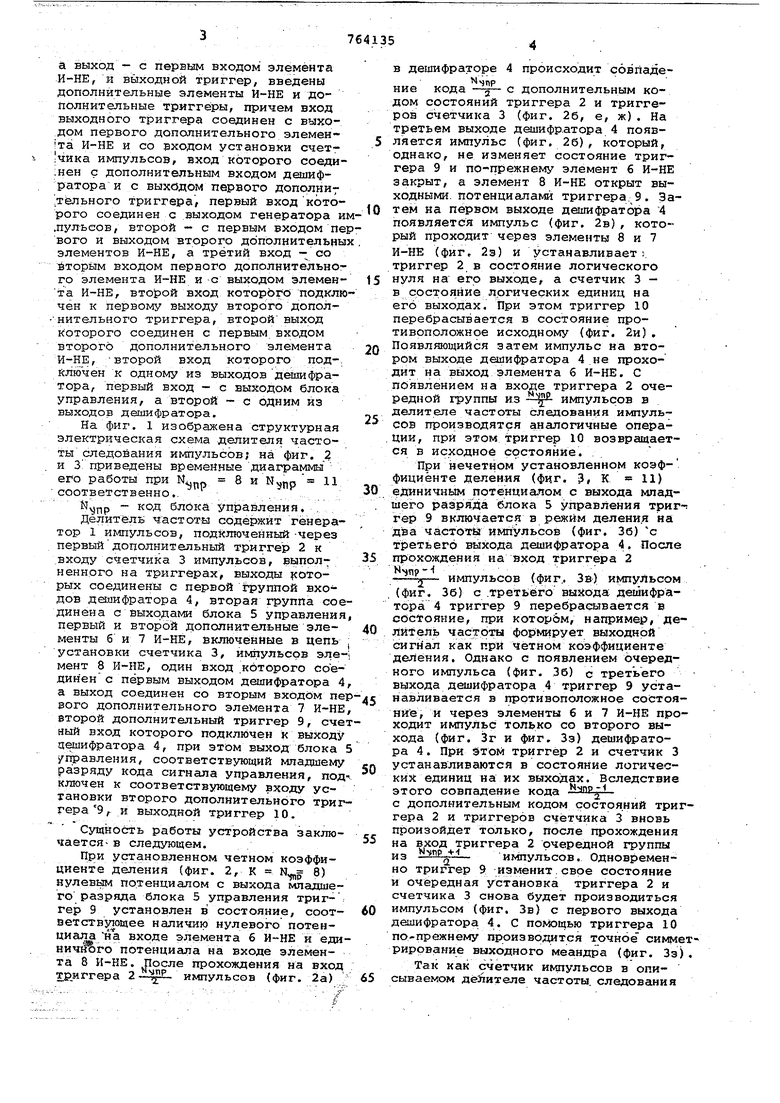

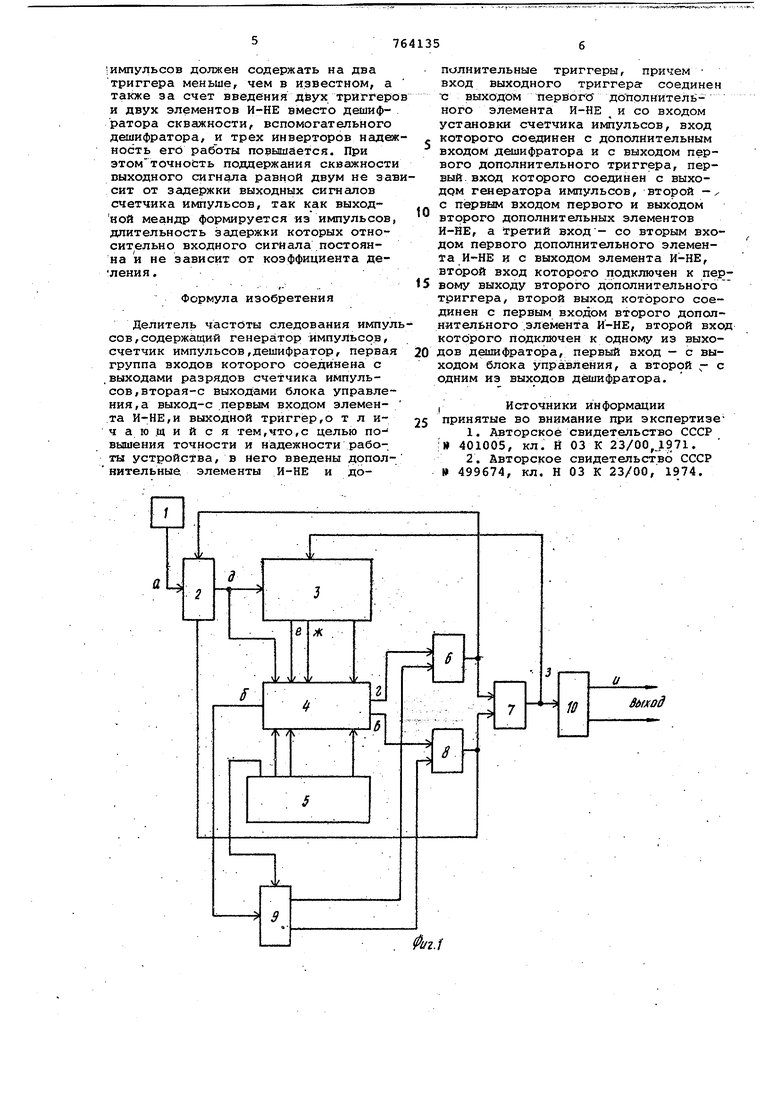

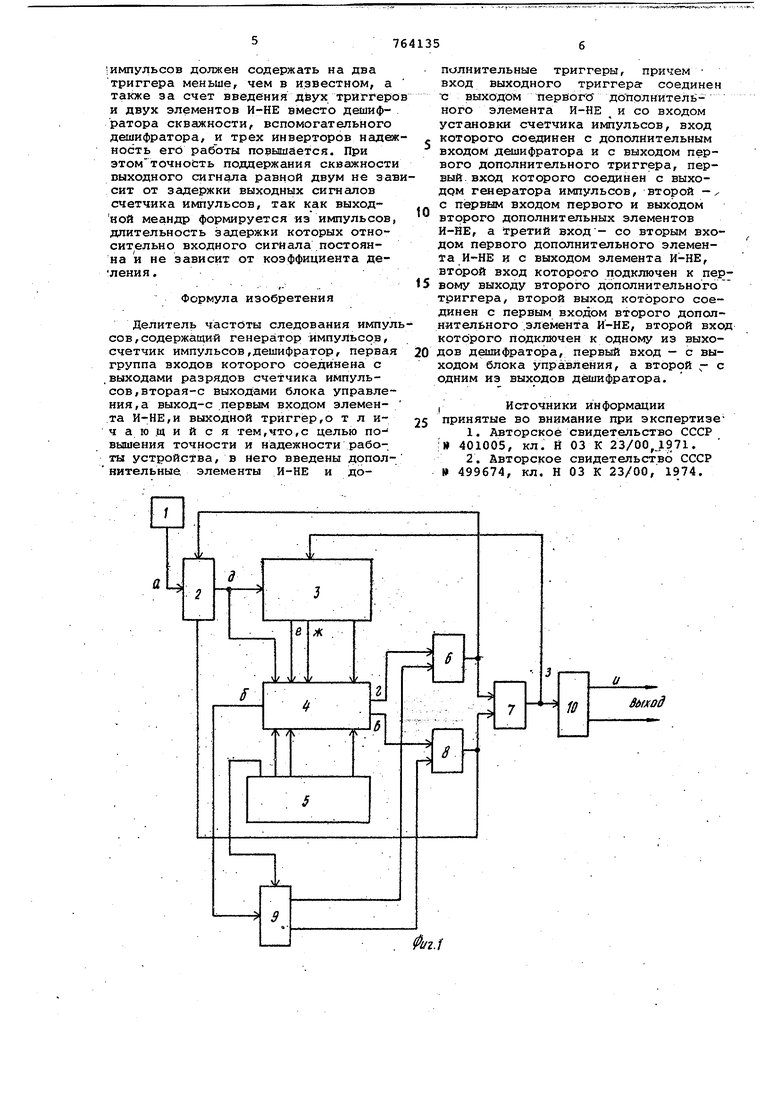

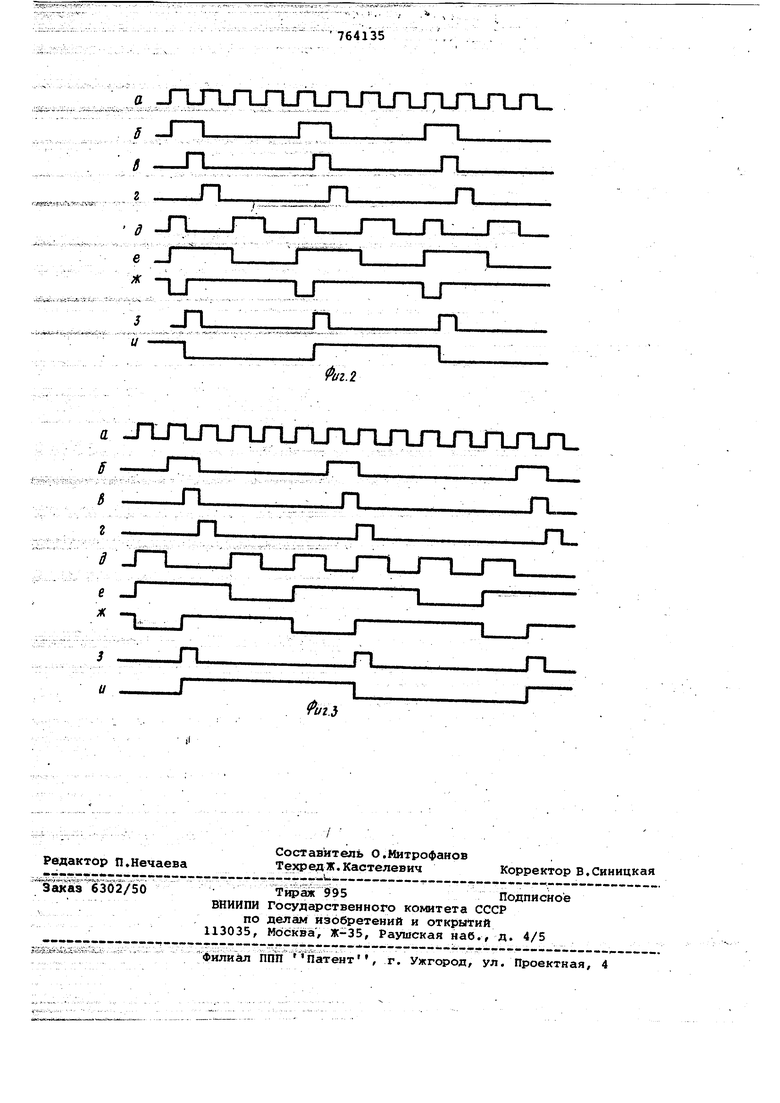

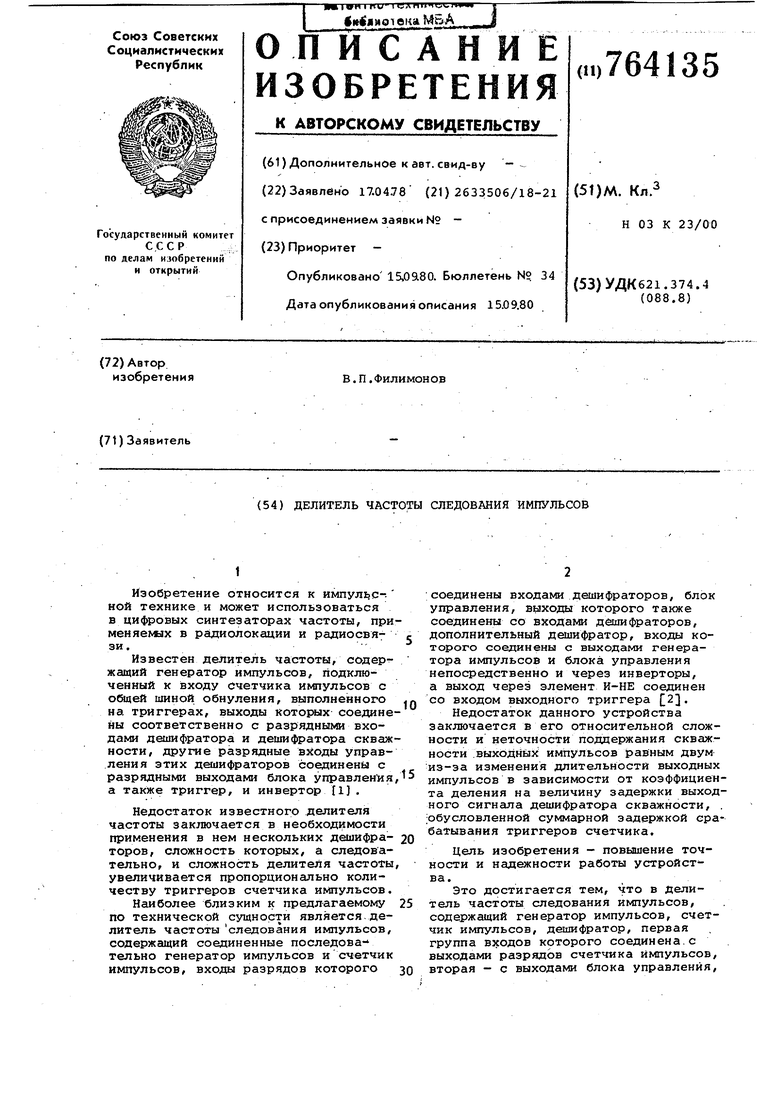

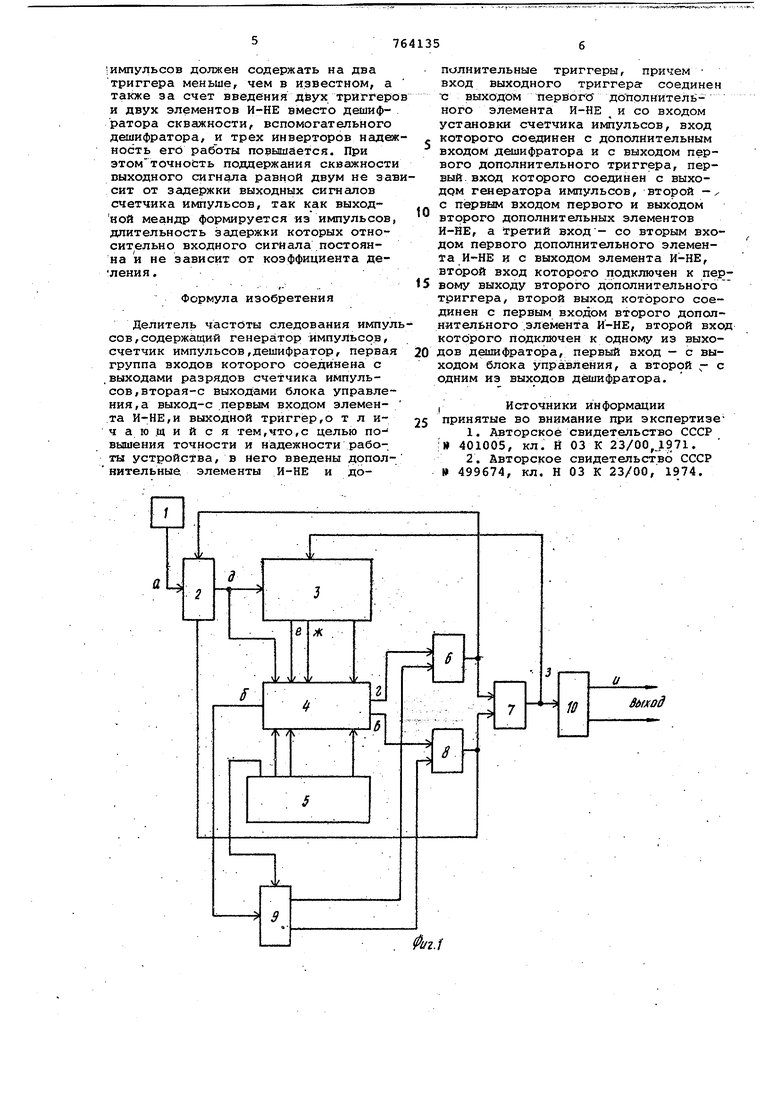

Изобретение относится к импул1зс-ной технике и может использоваться в цифровых синтезаторах частоты, при меняем:1Х в радиолокации и радиосвязи. Известен делитель частоты, содержагций генератор импульсов, подключенный к входу счетчика импульсов с общей шиной обнуления, выполненного на триггерах, выходы которых соедине ны соответственно с разрядными входами дешифратора и дешифратора скваж ности, другие разрядные входы управления этих дешифраторов соединены с разрядными выходами блока управления а также триггер, и инвертор II. Недостаток известного делителя частоты заключается в необход ; мости применения в нем нескольких дешифраторов, сложность которых, а следовательно, и сложность делителя частоты увеличивается пропорционально количеству триггеров счетчика импульсов. Наиболее близким к предлагаемому по технической сущности является делитель частоты следования импульсов, содержащий соединенные последова- тельно генератор импульсов и счетчик импульсов, входы разрядов которого соединены входами дешифраторов, блок управления, выходы которого также соединены со входами дешифраторов, дополнительный дешифратор, входы которого соединены с выходами генератора импульсов и блока управления непосредственно и через инверторы, а выход через элемент И-НЕ соединен со входом выходного триггера 2. Недостаток данного устройства заключается в его относительной сложности и неточности поддержания скважности выходных импульсов равным двум из-за изменения длительности выходных импульсов в зависимости от коэффициента деления на величину задержки выходного сигнала дешифратора скважности, . обусловленной суммарной задержкой срабатывания триггеров счетчика. Цель изобретения - повышение точности и надежности работы устройст Это достигается тем, что в делитель частоты следования импульсов, содержащий генератор импульсов, счетчик импульсов, дешифратор, первая группа входов которого соединена.с выходами разрядов счетчика импульсов, вторая - с выходами блока управления. а выход - с первым входом элемента И-НЕ, и выходной триггер, введены дополнительные элементы И-НЕ и дополнительные триггеры, причем вход выходного триггера соединен с выходом первого дополнительного элемен та И-НЕ и со входом установки счет|чика импульсов, вход которого соеди:нен с дополнительным входом дешифратора и с выхсздом первого дополни .Тельного триггера, первый вход которого соединен с выходом генератора и .пульсов, второй - с первым входом пе вого и выходом второго дополнительны элементов И-НЕ, а третий вход йторым входом первого дополнительного элемента И-НЕ и с выходом элементга И-НЕ, второй вход которого подклю чен к первому выходу второго дополнительного триггера, второй выход Которого соединен с первым, входом второго дополнительного элемента И-НЕ, -второй вход которого под-., ключен к одному из выходов дешифратора, первый вход - с выходом блока управления, а второй - с одним из выходов дешифратора. На фиг. 1 изображена структурная электрическая схема делителя частоты следования импульсов; на фиг. 2 и 3 приведены временные диаграммы его работы при 8 и N,jj,p 11 соответственно... . , vnp °Д блока упрайления, . Делитель частоты содержит генератор 1 и пyльcoв, подключенный -через первыйдополнительный триггер 2 к .входу счетчика 3 импульсов, выпол7. ненн.ого на триггерах, выходы оторых соединены с первой группой входов дешифратора 4, вторая группа сое динена с выходами блока 5 управления первый и второй дополнительныеэлементы б и 7 И-НЕ, включенные в цепь установки счетчика 3, импульсов элемент 8 И-НЕ, один вход которого соединенс первым выходом дешифратора 4 а выход соединен со вторым входим пе вого дополнительного элемента 7 И-НЕ еторой дополнительный триггер 9, сче йый вход которого подключен к выходу дешифратора 4, при этом выход блока /правления, соответствующий младшему разряду кода сигнала управления, под ключен к соответствующему входу установки второго дополнительного триг гера 9, и выходной триггер 10. Сущность работы устройства заключается- в следующем. При установленном четном коэффициенте деления (фиг. 2, К - N 8) нулевым по.тенциалом с выхода младшего разряда блока 5 управления триггер 9 установлен в состояние, соответству1ощее наличию нулевого потенциа входе элемента б И-НЕ и еди ничного потенциала на входе элемента 8 И-НЕ. После прохождения на вход тр.иггера импульсов (фиг. 2а) в дешифраторе 4 происходит совпадение кода -j- с дополнительным кодом состояний триггера 2 и триггеров счетчика 3 (фиг. 2б, е, ж). На третьем выхсэде дешифратора 4 появляется импульс (фиг. 26), который, однако, не изменяет состояние триггера 9 и по-прежнему элемент б И-НЕ закрыт, а элемент 8 И-НЕ открыт выходными, потенциалами триггера. 9. Затем на первом выходе дешифратора 4 появляется импульс (фиг. 2в), который проходит через элементы 8 и 7 И-НЕ (фиг, 2з) и устанавливает, триггер 2 в состояние логического нуля на его выходе а счетчик 3 - в состояние логических единиц на его выходах. При этом триггер 10 перебрасывается в состояние противоположное исходному (фиг. 2и). Появляющийся затем импульс на втором выходе дешифратора 4 не проходит на выход элемента б И-НЕ. С появлением на входе триггера 2 очередной группы из jjP- импульсов в делителе частоты следования импульсов производятся аналогичные операции, при этом триггер 10 возвращается в исходное состояние. При нечетном установленном коэффициенте деления (фиг. 3 К 11) единичным потенциалом с выхода младшего раэряГда блока 5 управления триг-; геР 9 включается в режим деления на два частотй импульсов (фиг. Зб) с третьего выхода дешифратора 4. После прохождения на вход триггера 2 -2I1L- импульсов (фиг,. Зв) импу Льсом (фиг. Зб) с .rpetbiero выхода дешифратора 4 триггер 9 перебрасывается в состояние, при которбм, например, делитель частоты формирует выходной сигнал как при Четном коэффициенте деления. Однако с появлением очередного импульса (фиг. Зб) с третьего выхода дешифратора 4 триггер 9 устанавливается в противоположное состоянйе, и через элементы б и 7 И-НЕ проходит импульс только со второго выхода (фиг. Зг и фиг. Зэ) дешифратора 4 . При этом триггер 2 и счетчик 3 устанавливаются в состояние логических единиц на их выходах. Вследствие этого совпадение кода с дополнительным кодом состояний триггера 2 и триггеров счётчика 3 вновь произойдет только, после прохождения на вход триггера 2 очередной группы из РЛ - импульсов. Одновременно триггер 9 -изменит.свое состояние и очередная установка триггера 2 и счетчика 3 снова будет производиться импульсом (фиг. Зв} с первого выхода дешифратора 4. С помощью триггера 10 по-прежнему производится точное симметриррвани е выходного меандра (фиг. Зэ) . Так как счетчик импульсов в описываемом дёйителе частоты, следования

1импульсов должен содержать на два триггера меньше, чем в известном, а также за счет введения двух триггеро и двух элементов И-НЕ вместо дешифратора скважности, вспомогательного дешифратора, и трех инверторов надежность его рабЪты повьлаается. При этомточность поддержания скважности выходного сигнала равной двум не завсит от задержки выходных сигналов счетчика импульсов, так как выходной меандр формируется из импульсов, длительность задержки которых относительно входного сигнала постоянна и не зависит от коэффициента деления.

Формула изобретения

Делитель частоты следования импулсов , содержащий генератор импульсов, счетчик импульсов,дешифратор, первая группа входов которого соединена с ,выходами разрядов счетчика импульсов, вторая-с выходами блока управления ,а выход-с первым входом элемента И-НЕ,и выходной триггер,о т л ичающийся тем,что,с целью повышения точности и надежности работы устройства, в него введены дополнительныб. элементы И-НЕ и дополнительные триггеры, причем вход выходного триггераг соединен -с выходом первого дбполнитель ного элемента И-НЕ и со входом установки счетчика импульсов, вход которого соединен с дополнительным входом дешифратора и с выходом первого дополнительного триггера, первый, вход которого соединен с выходом генератора импульсов, второй -, с первым входом первого и выходом

0 второго дополнительных элементов И-НЕ, а Третий вход - со вторым входом первого дополнительного элемента И-НЕ и с выходом элемента И-НЕ, второй вход которого подключен к первому выходу второго дополнительного триггера, второй выход которого соединен с первым входом второго дополнительного .элемента И-НЕ, второй вход которого подключен к одному из выходов ди1Шфратора, первый вход - с выходом блока Управления, а второй - с одним из выходов дешифратора.

I Источники информации 5 принятые во внимание при экспертизе1.Авторское свидетельство СССР I 401005, кл. Н 03 К 23/00,.1971.

2.Авторское свидетельство СССР 499674, кл, Н 03 К 23/00, 1974. . Фиг.1 SbfXOd

..: ... . -. ---- - -764135 ;,, ... .

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1984 |

|

SU1231604A1 |

| Делитель частоты следования импульсов | 1978 |

|

SU744992A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Цифровой измеритель скважности прямоугольных импульсов | 1990 |

|

SU1725152A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| Распылитель | 1988 |

|

SU1547857A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

Авторы

Даты

1980-09-15—Публикация

1978-04-17—Подача