которого соединены с управляющими входами соответственно первого и третьего счетчиков импульсов, а третий установочный вход триггера/ noAKjyo4eH к выходу второго элемента И 2 , .

Однако при формировании периодической импульсной последовательности с изменением периода по заданной программе в блок памяти временных интервалов необходимо записать коды временных интервалов для всех периодов последовательности, составляющих цикл программы изменения периода Поэтому при большом числе периодов требуется очень большой объем памяти.

Целью изобретения является уменьшение объема оборудования за счет сокращения объема памяти временных интервалов при формировании пер.иодической импульсной последовательност с переменным периодом.

Поставленная цель достигается тем что в устройство, содержащее три счетчика, соединенные первыми входами с нулевым выходом несимметричного триггера и первым входом первого триггера и установочным входом группы исполнительных элементов, группа входов которой соединена с группой выходов группы элементов И, группа информационных входов которой подключена к группе выходов первого счетчика, второй вход которого соединен с единичным выходом первого триггера, а третий вход - с выходом первого элемента, первым входом соединенного с единичным выходом несимметричного триггера, вход которого является входом устройства, а вторым входом - с выходом генератора импульсов и через элемент НЕ - с первым входом второго и третьего элементов И и управляющим входом .,, группы, элементов И,память временных интервалов, группа выходов которого соединена с группой выходов второго счетчика, вторым входом подключенного к выходу второго элемента И, второй вход которого соединен с первым выходом узла набора програ и ко второму входу первого триггера нулевой выход которого и выход генератора импульсов соответственно соединены со вторым и третьим входами третьего счетчика, подключенного выходом к второму входу третьего элемента И, выход которого соединен С третьим входом первого триггера, память кодов изменения периода, четвертый элемент И , второй триггер и коммутатор, причем первая и вторая группы входов коммутатора соединены соответственно с группами выходов памяти временных интервалов и памяти кодов изменения периода, первым входом соединенной с нулевым выходом несимметричного триггера и

первым входом второго триггера, а вторым входом - со вторым входом второго триггера, третьим входом второго счетчика, четвертым входом первого счетчика и выходом четвертого элемента И, входы которого подключены соответственно ко второму выходу узла набора программ и выходу элемента НЕ, выход третьего элемента И соединен к третьему входу второго триггера, выходом подключенного к входу коммутатора, группа выходов которого соединена с группой входов третьего счетчика.

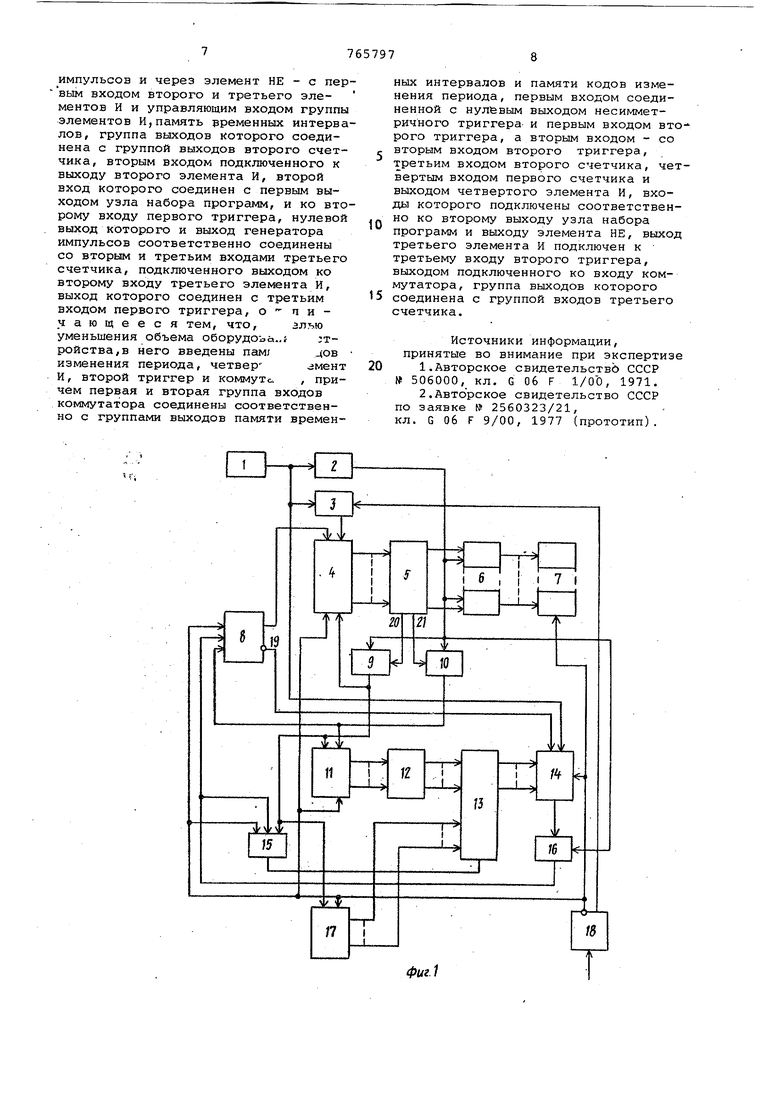

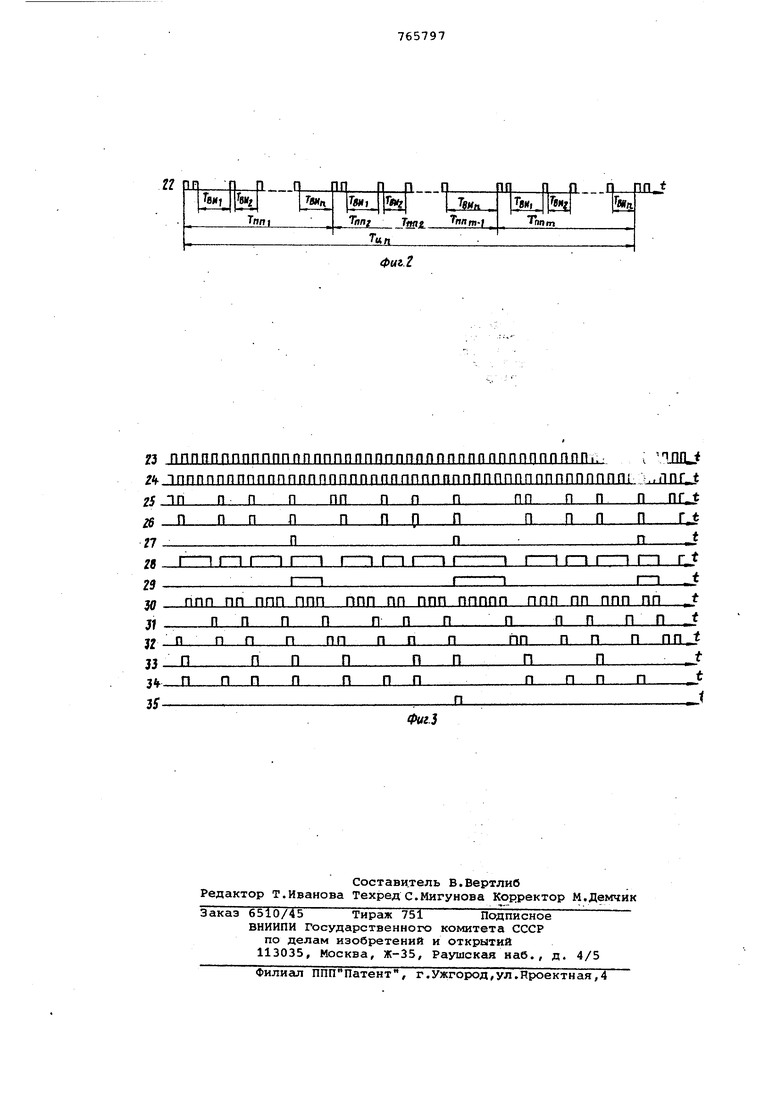

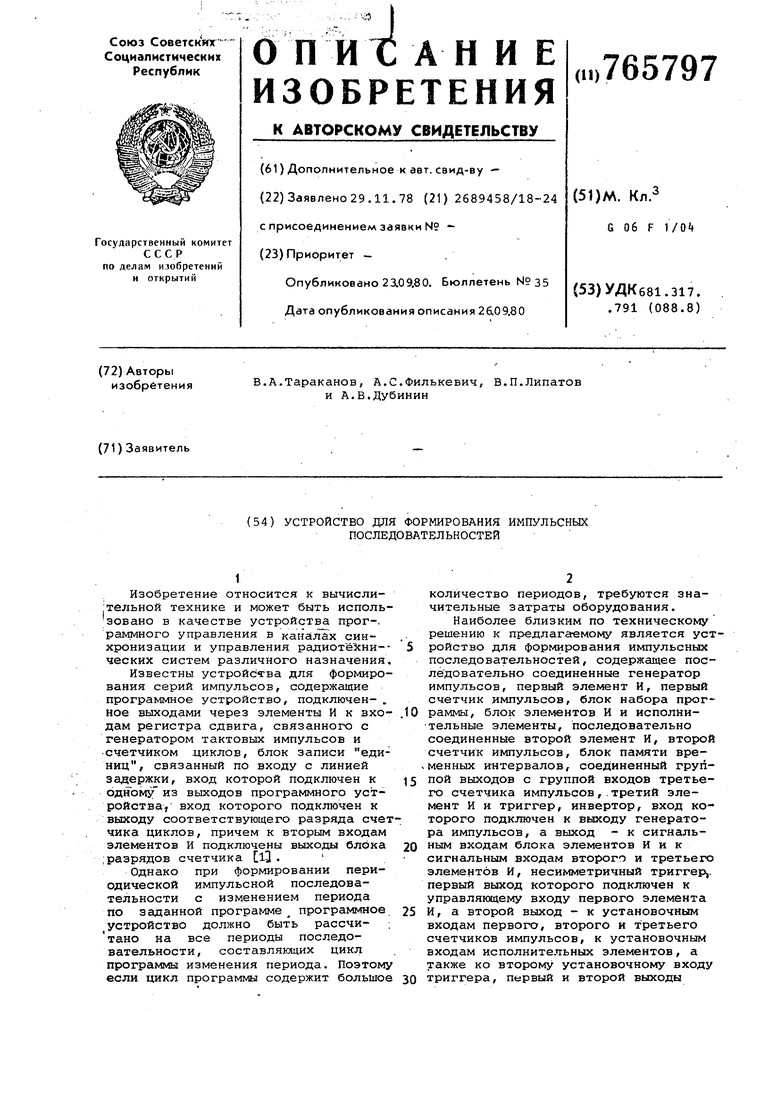

На фиг. 1 показана блок-схема устройства; на фиг. 2- пример периодической импульсной последовательности, а на фиг. 3 - временная диаграмма работыустройства.

Устройство содержит генератор 1 импульсов, элемент НЕ 2, первый элемент И 3, первый счетчик 4 импульсов , узел 5 набора программы, элементы И бгруппы, исполнительные элементы 7 группы, первый триггер 3, четвертый элемент И 9, второй элемент И 10, второй счетчик 11 импульсов, память 12 временных интервалов, коммутатор 13, третий счетчик 14 импульсов, второй триггер 15, тре тий элемент И 16, память 17 кодов изменения периода, несимметричный триггер 18, нулевой выход 19 первого триггера, второй 20 и первый 21 выходы узла 5 набора программы.

На фиг. 2 приняты следуквдие обозначения: Тви - длительность временного интервала, Тр,р, - длительность периода последовательности, Тцп длительность цикла программы изменения периода.

На фиг. 3 приняты следующие обозначения: 2.3 - сигналы,на выходе генератора 1, 24 - сигнг лы на выходе элемента НЕ 2, 25 - сигналы на выходе одного из элементов И 6, 26- : сигналы на выходе элемента И 10, 27 сигналы на выходе эле1У ента И 9, 28 сигналы на втором выходе 19 первого триггера 8, 29 - сигналы на выходе второго триггера 15, 30 - импульсы счета счетчика 14, 31 - -импульсы на выходе элемента И 16, 32 - импульсы счета счетчика 4,33,34 и 35 - сигналы параллельного кода на выходе коммутатора 13.

Устройство работает следующим- образом.

Формирование периодической последовательности рассматривают на примере формирования периодической последовательности с четырьмя временными интервалами и циклом программы в три периода повторения для одного исполнительного Элемента (см.фиг. 3, сигнал 25) .

В момент включения напряжения питания устройства (см.фиг.1) несимметричный триггер самоустанавливает ся в нулевое состояние. При этом на входы триггеров 8,15, счетчиков 4,1 14, а также на исполнительные элеме ты 7 и память 17 подается сигнал, устанавливающий эти элементы в начальные состояния, соответствующие началу работы устройства, а на первый вход элемента И 3 в этот момент подается сигнал, запрещающий прохож дение импульсов 23 генератора 1 на счетный (третий) вход счетчика 4. После установки несимметричного триггера 18 в единичное состояние, на элемент И 3 подается сигнал, раз решающий прохождение импульсов 23 на счетный вход счетчика 4. Для описываемой временной последовательности в начале цикла работы устройства сигналы с единичного выхода триггера 8 формируют импульсы 32 счета счетчика 4. По кодам,вырабатываемым счетчиком 4, из узла 5 набора программы выдается заданная для данного момента времени, кодовая комбинация импульса, один ид разрядов которой после стробирования на элементах И 6 инвертируемыми импульсами 24 ген ератора 1 имеет вид сигнала. 25.. Перед началом первого временного интервала одновременно с последней кодовой комбинацией импульсов узла 5 с выхода 21 выдается сигнал, поступающий на элемент И 10 на выходе которого формируется сигнал 26. Сигнсш 26.поступает на вход триггера 8 и переключает его. С выхода 19 триггера 8 вЕДдается сигнал 28. При этом прекращается выборка из узла 5 и подается разрешающий потенциал на счетчик 14, а счетчик 4 остается в состоянии, в которое он был установлен для выборки из узла 5 последней кодовой комбинации С элемента И 10 сигнал 26 поступает на триггер 8 и вход счетчика 11 и устанавливает в-нем код, при кото- . ром из. соответствующей ячейки памяти 12 выбирается параллельный код данного временного интервала, который через коммутатор 13 сигналами 33,34 и 35 записывается в счетчик 14. Заполнение счетчика 14 импульсами 30 начинает осуществляться послезаписи в этот счетчик кода временного интервала. Простробированный на. элементе И 16 сигнал 31 переполнения счетчика 14 переключает триггер 8, единичный выход которого.разрешает прохождение импульсов 32 на счетчик 4f а нулевой выход запрещает работу счетчика 14. Таким образом начинается формирование кодовых импульсов на выходе узла 5, прекращается формирование первого временного интервала, а счетчик 14 после переполнения остается в нулевом -состоянии. Подобным образом происходит формирование второго и третьего временных интервалов. Перед началом формирования четвертого, последнего, интервала в последовательности одновременном с имйульсом на-выходах- 21 и 20 узла 5 появляется импульс, поступающий на эле.мент И 9, на выходе которого формируется сигнал 27. Сигнал 27 поступает на первый вход триггера 15 и переключает его в единичное состояние. Одног временно сигнал 27 поступает на входы счетчиков 11,4, которые устанавливаются в состояние, соответствующее началу последовательности, и на вход памяти 17, на вглходе которой появ- . ляется код четвертого временного интервала. Сигнал 29 с выхода триггера 15 поступает на вход коммутатора 13j по которому на выходе его появляется код из памяти 17, который записывается в счетчик 14, где происходит преобразование кода непосредственно во временной интервал. Сигнал переполнения счетчика 14 устанавливает триггер 15 в нулевое состояние. В дальнейшем начинается формирование нового периода последовательности. Таким образом, устройство позволяет формировать периодические импульсные последовательности с переменным периодом повторения, введение второго триггера, четвертого элемента И, коммутатора и памяти кодов временных . интервалов, в которой хранятся коды изменяемых временных интервалов и управляемой от узла набора программы, позволяет уменьшить общий объем оборудования устройства, так как число запоминающих ячеек блока памяти временных интервалов равно числу временных интервалов в пеоиоды последовательности без одного, а число ячеек , памяти кодов изменения периодов равно числу периодов, составляющих цикл ггрограммы изменения периода. изобретения Устройство для .формирования им-пульсных последовательностей, содержащее три счетчика, соединенные перйыми входами с нулевым выходом несимметричного триггера и, первым входом первого триггера и установочным входом группы выходных усилителей, группа входов которой соединена с выходами соответствующих элементов И группы, информационные входы которых подключены соответственно к выходаич первого счетчика, второй вход которого срединен с единичным выходом первого триггера, а третий вход - с выходом первого элемента И, первым входом соединенного с единичным выходом несимметричного триггера, вход которого является входом устройства, а вторым входом - с выходом генератора

импульсов и через элемент НЕ - с первым входом второго и третьего элементов И и управляющим входом группы элементов И,память временных интервалов, группа выходов которого соединена с группой выходов второго счетчика, вторым входом подключенного к выходу второго элемента И, второй вход которого соединен с первым выходом узла набора программ, и ко второму входу первого триггера, нулевой выход которого и выход генератора импульсов соответственно соединены со вторым и третьим входами третьего счетчика, подключенного выходом ко второму входу третьего элемента И, выход которого соединен с третьим входом первого триггера, о п и чающееся тем, что, алью уменьшения объема оборудода.. :тройства,в него введены пам; 4Ов изменения периода, четвер змент И, второй триггер и коммутс. , причем первая и вторая группа входов коммутатора соединены соответственно с группами выходов памяти временных интервалов и памяти кодов изменения периода, первым входом соединенной с нулевым выходом несимметричного триггера и первым входом второго триггера, а вторым входом - со вторым входом второго триггера, третьим входом второго счетчика, четвертым входом первого счетчика и выходом четвертого элемента И, входы которого подключены соответственно ко второму выходу узла набора программ и выходу элемента НЕ, выход третьего элемента И подключен к третьему входу второго триггера, выходом подключенного ко входу коммутатора, группа выходов которого 5 соединена с группой входов третьего счетчика.

Источники информации, принятые во внимание при экспертизе 0 1.Авторское свидетельство СССР № 506000, кл. G Об F 1/00, 1971. 2.Авторское свидетельство СССР по заявке № 2560323/21, кл. G Об F 9/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсных последовательностей | 1977 |

|

SU737951A1 |

| Устройство для формирования импульсных последовательностей | 1980 |

|

SU866715A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для тренировки операторов | 1989 |

|

SU1647621A1 |

| Устройство для управления с контролем | 1983 |

|

SU1156074A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Функциональный генератор | 1981 |

|

SU962997A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

Авторы

Даты

1980-09-23—Публикация

1978-11-29—Подача