113

Изобретение относится к области вычислительной техники и может быть использовано при создании микроЭВМ микроконтроллеров и других устройств на основе микропроцессоров.

Целью изобретения является расширение функциональньк возможностей устройства за счет имитации временны характеристик блоков ввода-вывода отлаживаемого устройства.

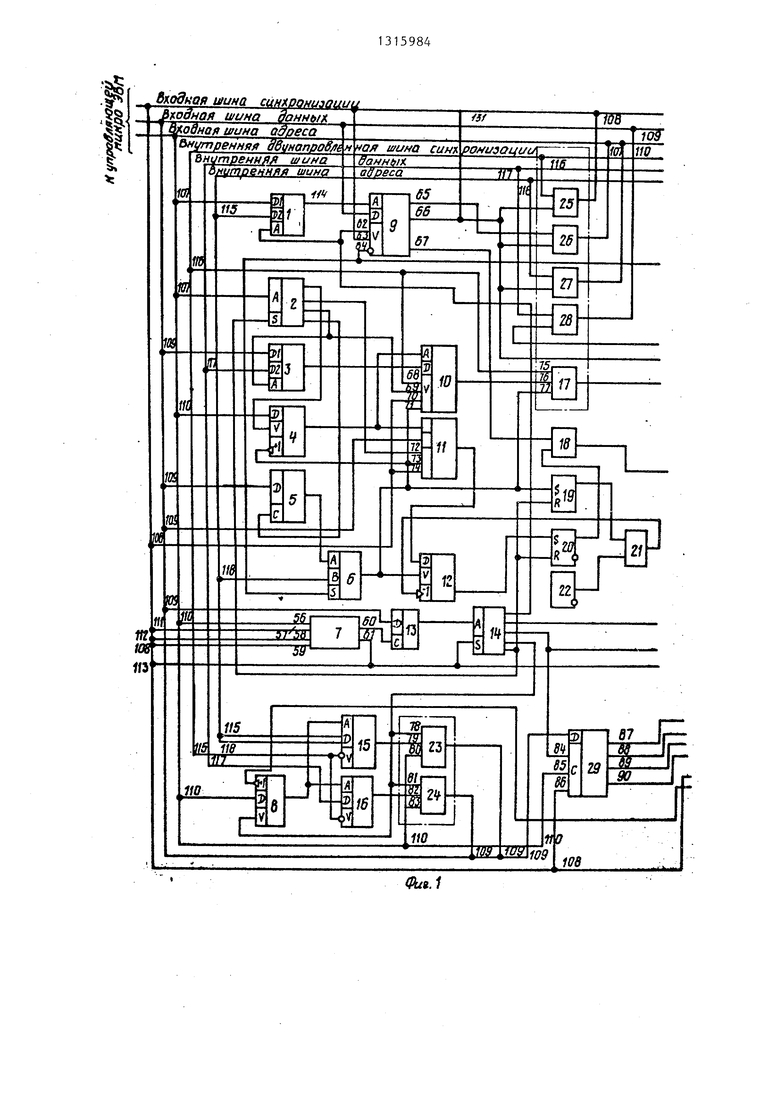

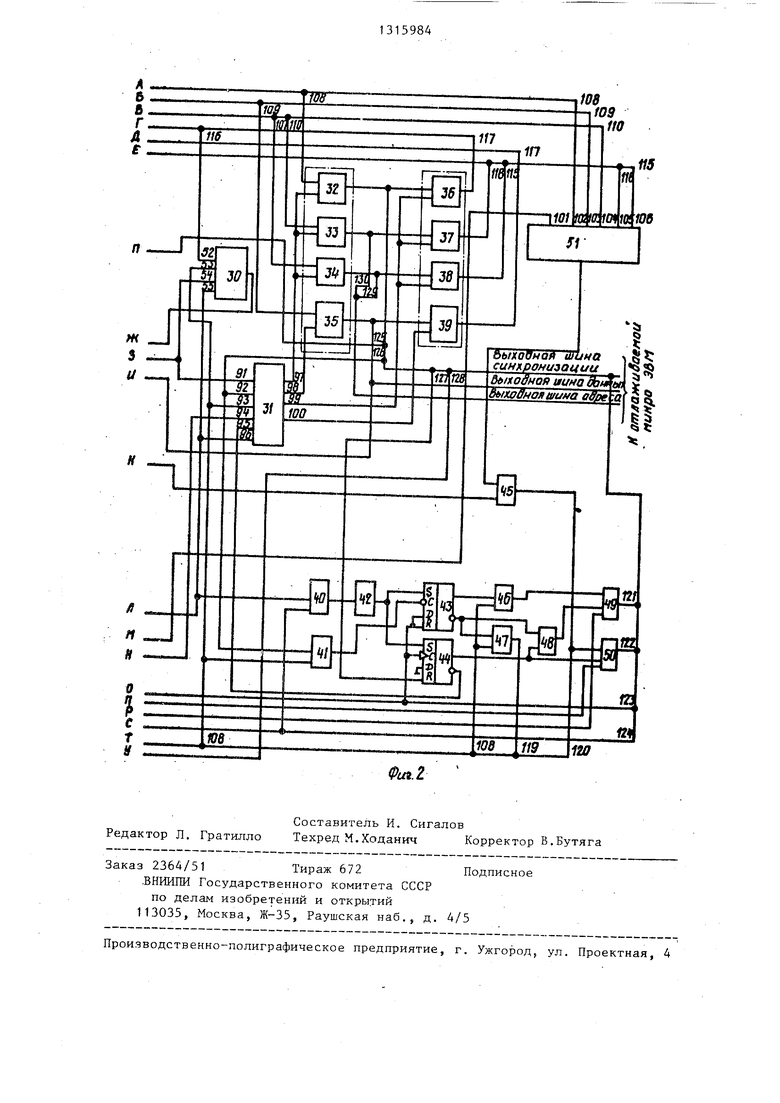

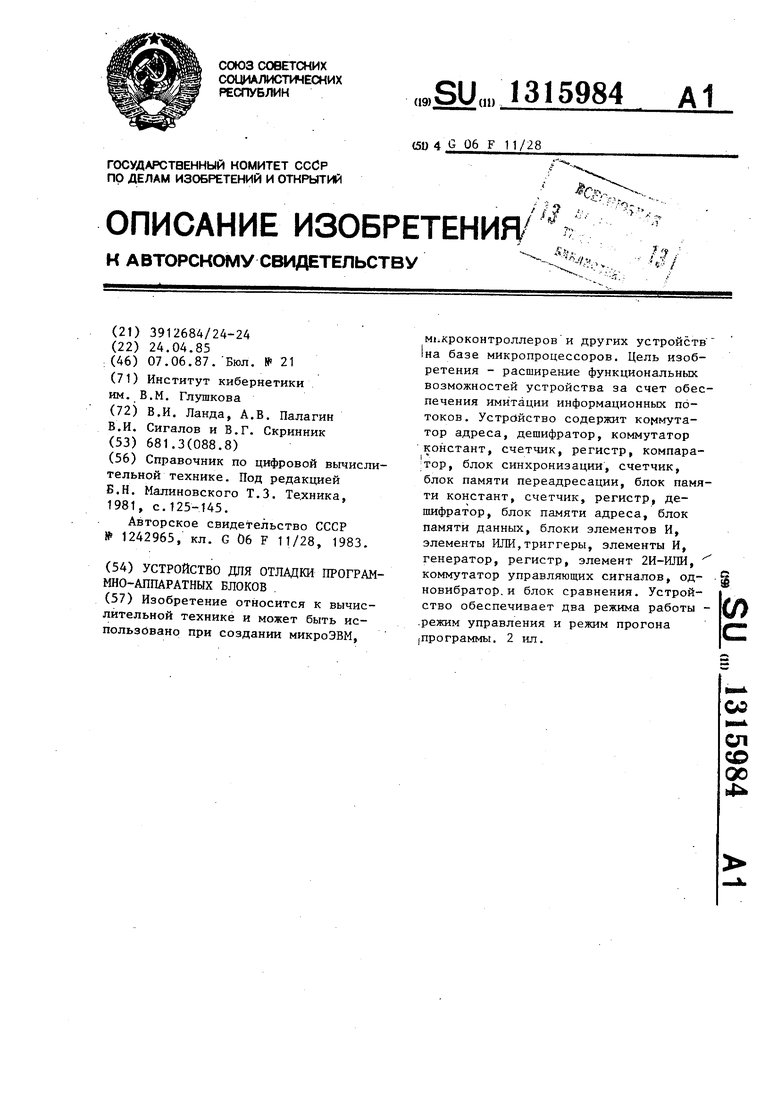

На фиг.1 и 2 представлена схема предлагаемого устройства для отладки программно-аппа:ратных блоков.

Устройство .содержит коммутатор 1 адреса, второй дешифратор 2, коммутатор 3 констант, второй счетчик 4, третий регистр 5, компаратор 6, блок 7 синхронизации, первый счетчик 8, блок 9 памяти переадресации, блоки 10 и 11 памяти констант и временных интервалов соответственно,, третий счетчик 12, второй регистр 13, первы дешифратор 14, блоки памяти адреса и данных 16, пятнадцатый блок элементов И 17, шестой элемент ИЛИ 1.8} третий 19 и четвертый 20 триггеры, четвертый И 21, генератор 22, седьмой 23, восьмой 24, третий 25, первый 26 второй 27 и шестой 28 блоки элементов И, первый регистр 29, элемент 2И-ИЛИ 30, коммутатор 31 управляющих сигналов, четвертый 32, девятый 33, десятый 34, пятый 35, одиннадцатый 36, тринадцатый 37, четырнадцатый 38, пятнадцатый 39 блоки элементов И второй.элемент И 40, первый элемент ИЛИ 41J одновибратор 42, второй 43 и первый 44 триггеры, четвертый элемент ИЛИ 45, первый элемент И 46, третий элемент ИЛИ 47, третий элемен И 48, пятый 49 и второй 50 элементы ИЛИ, блок 51 сравнения, третий 52, второй 53, первый 54 и четвертый 55 входы элемента 2И-ИЛИ, вход 56 запуска, первый 57, второй 58 и третий 59 тактовые входы блока синхронизации, второй 60 и первьй 61 выходы блока синхронизации, третий 62, первый 63, второй 64 входы записи, первый информационньй 65 прямого доступа 66 и второй информационньй 67 выходы блока памяти переадресации, первый 68, второй 69 входы обращения, вход 70 записи и третий вход 71 обращения блока памяти констант, первый 72, второй 73 входы обращения и вход 74 записи блока памяти временных интервалов, первые 75, вторые 76, третьи 77 входы пятнадцатого блока эле42

ментов И, вторые 78, первые 79, третьи 80 входы седьмого блока элементов И, вторые 81, первые 82, третьи 83 входы восьмого блока элементов И, третий 84, второй 85, первый 86 входы записи, первый 87, четвертый 88, третий 89, второй 90 разрядные выходы первого регистра, первьй информационный 91, третий 92, второй 93 и

первый 94 управляющие, второй 95 и третий 96 информационные входы, первьй 97, второй 98, четвертый 99, третий 100 выходы коммутатора управляющих сигналов, второй 101 и первьй 102

входы разрешения, первый 103, второй 104, третий 105, четвертый 106 информационные входы блока сравнения, старшие четыре разряда входной шины 107 адреса, входы 108 приема и выдачи

информации, передаваемой или поступающей по входной шине 109 данных, младшие разряды входной шины 110 адреса, входы признака обращения к портам ввода-вывода 111 и начала

цикла 112, вход блокировки входной шины 113 синхронизации, выходы коммутатора 114 адреса, старшие четыре разряда внутренней шины 115 адреса, выходы приема и выдачи информации

внутренней двунаправленной шины

116синхронизации, внутренняя шина

117данных, младшие разряды-внутренней шины 118 адреса, входы 119 и 120 готовности и запроса прерывания входной шины синхронизации соответственно, выходы готовности 121 запроса., прямого доступа 122, инициализации 123, блокировки 124 входы признака обращения к портам ввода-вывода 125,

приема и выдачи информации 126, подтверждения прямого доступа 127, начала машинного цикла 128 выходной шины синхронизации, старшие четыре 129 и оставшиеся 130 разряды выходной

шины адреса, вход запроса прямого доступа входной шины 131 синхронизации.

Устройство работает под управлеием управляющей микроЭВМ, в качестве

оторой может быть использована, наример, микроэвм УВС-01 и обеспечива-. т отладку устройств на основе микопроцессоров, например, К580ИК80 или 8080 (ф.INTEL). Системная шина

управляющей микроЭВМ подключается к входным шинам устройства для отладки программно-аппаратных блоков. Выходные шины устройства подключаются к инам отлаживаемой микроЭВМ. Устройство может работать в одном из двух режимов: режиме управления и режиме пригона программы.

В режиме управления управляющая микроэвм осуществляет обмен информацией с внутренними блоками устройства отладки, памятью и портами ввода- вывода отлаживаемой микроЭВМ, а такЭВМ. В последнем случае укаэьгаается сегмент памяти управляющей микроЭВМ, соответствующий данному сегменту памяти отлаживаемой микроЭВМ, Эта информация записывается в блок 9 памяти переадресации по информационным шинам управляющей микроЭВМ, подключенным к информационным входам блока 9 памяти переадресации через входную

же внутренними узлами микропроцессора

последней. Рассмотрим работу устрой- щ шину 109 данных. Адрес, по которому

ства в режиме управления. Работой записывается эта информация, опредеустройства в этом режиме управляет

блок, включающий блок 7 синхронизации,

регистр 13 и дешифратор 14. Для обраляется адресом на четырех старших адресных шинах управляющей микроЭВМ, подключенных к первым информационным

щения к тому или иному блоку устрой- J5 входам коммутатор 1 через входную

ства отладки управляющая микроЭВМ устанавливает через шину 110 адреса на входах 56 блока 7 синхронизации адрес, логически являющийся одним из портов ввода-вывода управляющей микроэвм, на информационных входах регистра 13 через шину 109 данньпс 30

шину 107 адреса. При появлении на выходе дешифратора 14 сигнала обращения к блоку 9 памяти переадресации, по входу 62 включается блок 9 памяти 2Q переадресации, а старшие четыре разряда адреса управляющей микроЭВМ через коммутатор 1 поступают на адрес- код блока устройства отладки, к которо- ные входы блока 9 памяти переадреса- му производится обращение,, а на вхо- ции. Запись в блок 9 памяти переадре- де 57 блока синхронизации через вы- 25 сации производится при подаче на ход 111 - сигнал признака обращения его вход 63 сигнала выдачи информации к порту ввода-вывода. При поступлении на вход 59 синхронизатора через выход 108 сигнала выдачи информации управляющей микроЭВМ на выходе 60 появляется сигнал записи в регистр 13. После записи кода блок синхронизации начинает подсчет сигналов начала машинного цикла управляющей микро- ЭВМ, поступающих через выход 112 на вход 58 синхронизатора. На седьмом цикле на выходе 61 синхронизатора появляется сигнал, включающий дешифратор 14 и блокирующий обращение к памяти и портам ввода-вывода управляющей икpoЭBM (выход 113). При включении дешифратора 14 на одном из его выходов (в зависимости от кода, ранее записанного в регистр 13) появляется сигнал обращения к соответ- му устройству ввода. В блок памяти ствующему блоку устройства отладки. временных интервалов загружаются коды Первый выход дешифратора 14 управля- временных интервалов между обращения- ет загрузкой информации в блок 9 па- ми к имитируемому устройству ввода- мяти переадресации. В этот блок загру- вывода. Запись производиться при по- жается информация о состоянии каждо- 0 Даче на вход 108 сигнала вьщачи ин- го сегмента памяти, адресуемой отлажи- формации управляющей микроЭВМ. Адрес ваемой микроэвм. При этом весь объем

управляющей микроЭВМ через выход 108. Пятый выход дешифратора 14 устанавливает в исходное (нулевое) состояние триггеры 19 и 20 и, кроме того, включает дешифратор 2, который управляет загрузкой информации в счетчик 4, блок 10 памяти констант, блок 11 памяти временных интервалов 35 и регистр 5. Каждое из этих устройств выбирается в зависимости от кода на двух старших адресных шинах управляющей микроэвм, подключенных к адресным входам дешифратора 2 через входную шину 107 адреса. В блок 10 памяти кон- констант через входную шину 109 данных и коммутатор 3 загружаются константы, которые должны считываться при последовательных обращениях к имитируемо40

ячейки блока 10 памяти констант и блока 11 памяти временных интервалов, в которые производится запись, пред- 55 варительно записывается в счетчик 4 через входную шину 110 адреса. Адрес имитируемого устройства ввода-вывода записывается в регистр 5 через входную шину 109 данных. . х

адресуемой памяти разбивается на 16 сегментов, определяемых четырьмя старшими разрядами адреса.

Для каждого сегмента указывается: защищен ли он (разрешено ли к нему обращение), находится ли в отлаживаемой микроэвм или в управляющей микроЭВМ. В последнем случае укаэьгаается сегмент памяти управляющей микроЭВМ, соответствующий данному сегменту памяти отлаживаемой микроЭВМ, Эта информация записывается в блок 9 памяти переадресации по информационным шинам управляющей микроЭВМ, подключенным к информационным входам блока 9 памяти переадресации через входную

ляется адресом на четырех старших адресных шинах управляющей микроЭВМ, подключенных к первым информационным

шину 107 адреса. При появлении на выходе дешифратора 14 сигнала обращения к блоку 9 памяти переадресации, по входу 62 включается блок 9 памяти переадресации, а старшие четыре разряда адреса управляющей микроЭВМ через коммутатор 1 поступают на адрес- ные входы блока 9 памяти переадреса- ции. Запись в блок 9 памяти переадре- сации производится при подаче на его вход 63 сигнала выдачи информации му устройству ввода. В блок памяти временных интервалов загружаются коды временных интервалов между обращения- ми к имитируемому устройству ввода- вывода. Запись производиться при по- Даче на вход 108 сигнала вьщачи ин- формации управляющей микроЭВМ. Адрес

управляющей микроЭВМ через выход 108. Пятый выход дешифратора 14 устанавливает в исходное (нулевое) состояние триггеры 19 и 20 и, кроме того, включает дешифратор 2, который управляет загрузкой информации в счетчик 4, блок 10 памяти констант, блок 11 памяти временных интервалов и регистр 5. Каждое из этих устройств выбирается в зависимости от кода на двух старших адресных шинах управляющей микроэвм, подключенных к адресным входам дешифратора 2 через входную шину 107 адреса. В блок 10 памяти кон- констант через входную шину 109 данных и коммутатор 3 загружаются константы, которые должны считываться при последовательных обращениях к имитируемо

шину 107 адреса. При появлении на выходе дешифратора 14 сигнала обращения к блоку 9 памяти переадресации, по входу 62 включается блок 9 памяти переадресации, а старшие четыре разряда адреса управляющей микроЭВМ через коммутатор 1 поступают на адрес- ные входы блока 9 памяти переадреса- ции. Запись в блок 9 памяти переадре- сации производится при подаче на его вход 63 сигнала выдачи информации му устройству ввода. В блок памяти временных интервалов загружаются коды временных интервалов между обращения- ми к имитируемому устройству ввода- вывода. Запись производиться при по- Даче на вход 108 сигнала вьщачи ин- формации управляющей микроЭВМ. Адрес

ячейки блока 10 памяти констант и блока 11 памяти временных интервалов, в которые производится запись, пред- варительно записывается в счетчик 4 через входную шину 110 адреса. Адрес имитируемого устройства ввода-вывода записывается в регистр 5 через входную шину 109 данных. . х

513

Третий выход дешифратора 14 управляет обращениями -к блоку 51 сравнения и к регистру 29. Выбор каждого из.этих блоков производится в зависимости от кода на трех младших адресных шинах управляющей микроЭВМ, подключенных к входам 104 блока 85 сравнения и регистра 29. В блок сравнения записываются адреса точек останова программы. Эти адреса записываются в блок сравнения по информационным шинам управляющей микроЭВМ, подключенным к входам 103 блока сравнения. Запись производится при поступлении на вход 102 сигнала выдачи информации управляющей микроЭВМ, сигнала обращения на вход 101 и при коде адреса О (вход 10.4).

В регистре 29 устанавливаются следующие сигналы, управляющие отлаживаемой микроэвм: Сброс (выход 87), Готов (выход 89), Запрос прямого Доступа (выход 88), Блокировка (выход 90). Назначение этих сигналов следующее: Сигнал Сброс - сигнал инициализации, после поступления которого микропроцессор отлаживаемой микроэвм начинает обращение к нулевой ячейке памяти. Сигнал Готов высоким уровнем разрешает работу микропроцессора отлаживаемой микроЭВМ, а низким уровнем останавливает его. . При низком уровне сигнала Готов мик ропроцессор останавливается на обращении к очередной ячейке памяти или порту ввода-вывода и не заканчивает это обращение до тех пор, пока уровень сигнала Готов не станет высоким. Сигнал Запрос прямого доступа отключает микропроцессор отлаживаемой микроэвм от шин последней, позволяя тем самым осуществить прямой доступ к ее памяти. Сигнал Блокировка запрещает обращение к памяти и портам ввода-вывода отлаживаемой микроЭВМ. Установка этих сигналов производится по информационным шинам управляющей микроэвм, подключенным к информационным входам регистра управления. Установка производится при подаче на вход 86 сигнала выдачи информации управляющей микроэвм и коде адреса 1 (вход 85).

Четвертый выход дешифратора 14 управляет обращениями к блокам памяти адреса 15 и данных 16. В режиме управления из этих блоков считьшается информация о коде выполнения программы отлаживаемой микроЭВМ, записанная

46

в блоки памяти адреса и данных в режиме прогона программы. Эта информация включает состояние адресных и информационных шин отлаживаемой микроЭВМ в каждом машинном цикле. Адрес ячейки блока памяти адреса и блока памяти данных, поступающий на информационные входы счетчика 8, записывается в счетчик при поступлении на

его вход параллельного занесения сигнала обращения к блокам памяти адреса и данньтх. Этот же сигнал строби- рует блок элементов И 23 или блок элементов И 24, через которые информация из блоков памяти адреса и данных поступает на информационные шины управляющей микроЭВМ. Блок элементов И 23 стробируется уровнем логического О на младшем разряде входной шины

адреса (вход 80), а блок элементов И 24 стробируется уровнем логической 1 на младшем разряде входной шины адреса (вход 83).

Второй выход дешифратора 14 управляет обращениями к памяти и портам ввода-вывода отлаживаемой микроЭВМ, а также обращениями к внутренним узлам микропроцессора последней. Для

обращения к памяти отлаживаемой микроЭВМ в регистре 29 предварительно устанавливается сигнал Запрос прямого доступа, передающийся через элемент ИЛИ 50 и вход 122 выходной

шины синхронизации на шину сигнала Запрос прямого доступа отлаживаемой микроэвм. При поступлении этого сигнала микропроцессор отлаживаемой микроэвм отключается от шин и позволяет осуществить прямой доступ к памяти. Дешифратор 14 вырабатывает сигнал обращения к отлаживаемой микроЭВМ, который поступает на вход 55 элемента 2И-ИЛИ 30 и вход 96 коммутатора 31 управляющих сигналов. Эти узлы представляют собой комбинационные схемы, управляющие передачей управляющих адресных и информационных сигналов управляющей микроэвм на

шины отлаживаемой микроЭВМ через блоки элементов И 32-35 при обращении к памяти, портам ввода-вывода или внутренним узлам микропроцессора отлаживаемой микроэвм, передачей управляющих адресных и информационных сигналов отлаживаемой микроЭВМ на внутренние шины устройства отладки через блоки элементов И 36-39 в режиме прогона программы отлаживаемой

микроэвм и передачей информационных сигналов с внутренних шин устройства отладки на шины управляющей микро- ЭВМ через блок элементов И 28 при прямом доступе отлаживаемой мйкроЭВМ к памяти управляющей микроэвм и при .чтении информации из отлаживаемой микроэвм. Узлы реализуют следующие логические выражения: элемент 2И-ИЛИ 30

y(x jAXjj) V (х

54 51

).

где у - сигнал на выходе элемента 2И-ИЛИ 30, Xyj- сигнал на входе 53 (сигнал приема информации управляющей микроэвм); сигнал на входе 55 (сигнал обращения к отлаживаемой

микроэвм);

Xj.- сигнал на входе 54 (признак прямого доступ отлаживаемой мнкро- ЭВМ к памяти управляющей микроЭВМ); Xj,- сигнал на входе 52 (сигнал выдачи информации отлаживаемой микро- ЭВМ, переданный на внутреннюю шину устройства отладки);

коммутатор управляющих сигналов 31

97 gi 2) где Xjj- сигнал обращения к отлажи10 соответствии с выражением (1), поступают на информационные шины управляющей микроэвм через входную шину данных. Таким образом, информация из отлаживаемой микроЭВМ считывается

15 на информационные шины управляющей микроэвм.

Для обмена информацией с внутренними узлами микропроцессора отлаживаемой микроэвм в регистре 29 пред20 варительно устанавливается сигнал Блокировка (выход 90) и снимается сигнал Готов (т.е. на выходе 89 регистра управления устанавливается уровень логического О). Сигнал

25 Готов с выхода 89 регистра 29 управления через элемент ИЛИ 49 и вход 121 поступает на шину сигнала Готов отлаживаемой микроЭВМ. Сигнал Блокировка с выхода 90 регистра 29 упваемой микроэвм; хjj- Сигнал снулево-ЗОравления через управляющий выход 124

го выхода триггера 44 (при отсутст-поступает на шину сигнала Блокироввии обращения к внутренним узлам мик-ка отлаживаемой микроЭВМ. Затем деропроцессора отлаживаемой микроЭВМшифратор 14 вырабатывает сигнал обраимеет уровень логической 1)iщения к отлаживаемой микроЭВМ, При

(х

д(,Л Хдз

) V (хj л Хд2)(3) j совпадении этого сигнала с сигналом

Блокировка сигнал уровня логической 1 с выхода элемента И 40 через одновибратор 42 устанавливает по S- входу триггеры 43 и 44. Сигнал уровгде Xjj- сигнал выдачи информации управляющей микроЭВМ; х,- признак прямого доступаJ сигнал приема информации отлаживаемой микроЭВМ,

Уз9 (,) л

$5 1

.(4)

где Xj - сигнал включения дешифратора 14, т.е. признак обращения управляющей микроэвм к блокам устройства отладки.

too

94

V У,

98

-(5)

Таким образом, если производится запись в память отлаживаемой микро- ЭВМ, в соответствии с выражениями

45 цикла управляющей микроЭВМ сигналы вьдачи информации и приема информации (входы 108) отсутствуют (логический О), на выходах элементов И 46 и ИЛИ 49 сохраняются уровни логичес(2) и (3) стробируются блоки элемен- 50 кого О, а на выходе элемента ИЛИ 47

тов И 32-35 и управляющие адресные, информационные сигналы управляющей микроэвм передаются на шины отлаживаемой микроэвм. При чтении информации из памяти отлаживаемой микроЭВМ направление передачи адресных и управляющих сигналов остается таким же, как и в режиме записи, а напрабление передачи информационных сигналов ме

8

1

няется на противоположное, так как в соответствии с выражениями (3) и (3) блок элементов И35 блокируется, а блок элементов И 39 стробируется. Сигналы с информационных шин отлаживаемой микроэвм через блок элементов И 39 поступают на внутренние шины 117 данных, а оттуда через блок элементов И28, который стробируется в

10 соответствии с выражением (1), поступают на информационные шины управляющей микроэвм через входную шину данных. Таким образом, информация из отлаживаемой микроЭВМ считывается

15 на информационные шины управляющей микроэвм.

Для обмена информацией с внутренними узлами микропроцессора отлаживаемой микроэвм в регистре 29 пред20 варительно устанавливается сигнал Блокировка (выход 90) и снимается сигнал Готов (т.е. на выходе 89 регистра управления устанавливается уровень логического О). Сигнал

25 Готов с выхода 89 регистра 29 управления через элемент ИЛИ 49 и вход 121 поступает на шину сигнала Готов отлаживаемой микроЭВМ. Сигнал Блокировка с выхода 90 регистра 29 упj совпадении этого сигнала с сигналом

Блокировка сигнал уровня логической 1 с выхода элемента И 40 через одновибратор 42 устанавливает по S- входу триггеры 43 и 44. Сигнал уров40 ня логической 1 поступает на вход элемента И 46, а сигнал уровня логического О с нулевого выхода триггера 43 поступает на вход элемента ИЛИ 47. Так как в начале машинного

45 цикла управляющей микроЭВМ сигналы вьдачи информации и приема информации (входы 108) отсутствуют (логический О), на выходах элементов И 46 и ИЛИ 49 сохраняются уровни логичеспоявляется сигнал уровня логического О. Таким образом, при обращении управляющей микроЭВМ к микропроцессору отлаживаемой микроЭВМ на шине Го- 55 тов управляющей микроЭВМ (выход 119) и шине Готов отлаживаемой микроЭВМ (выход 121) устанавливается логический О). Сигнал с единичного выхода триг- триггера 44 через элемент ИЛИ 50 устанавливает уровень логической 1 сигнала Захват -(шина 122) отлаживаемой микроэвм. Сигнал с нулевого выхода, триггера 44 поступает на вход 95 коммутатора управляющих сигналов 31 и в соответствии с выражениями (2) и (4) блокирует прохождение адресных и управляющих сигналов через блоки элементов И 32, 33, 34, 36, 37 и 38.

н на входе Готов отлаживаемой микроэвм появляется сигнал уровня логической 1. После этого микропроцессор отлаживаемой микроЭВМ заканчивает

верждение прямого доступа, сбрасывающий триггер 44, При этом сигналы Запрос прямого доступа и Готов

Таким образом, в этом режиме произво-ю вает цикл приема информации и задним дится обмен только информационными фронтом сигнала приема информации че- сигналами. Обмен информационными сиг- рез элемент ИЛИ 41 сбрасывает по С- налами осуществляется так же, как и в входу триггер 43. При этом на выходе режиме обращения к памяти отлаживаемой элемента И 48 появляется логическая микроэвм.15 1, которая блокирует элемент ИЛИ 49

Если управляющая микроЭВМ выполняет запись во внутренние узлы микропроцессора отлаживаемой микроЭВМ, то при появлении логической 1 на выходе 108 вьщачи информации из управляю-20 цикл выдачи информации и вьщает на щей микроэвм на выходе элемента И 46 управляющий вход 127 сигнал Подт- появляется сигнал логической 1, который блокирует элемент ИЛИ 49 и устанавливает логическую 1 на входе Готов (121) отлаживаемой микроЭВМ. В 25 снимаются ( логический О) и микрорезультате этого микропроцессор отлажи- процессор отлаживаемой микроЭВМ пере- ваемой микроэвм заканчивает цикл прие- ходит в состояние ожидания, ма информации и задним фронтом сигнала После обмена информацией с внут- приема информации отлаживаемой микро- ренними блоками устройства отладки, ЭВМ через элемент ИЛИ 41 по С-входу ЗО памятью отлаживаемой микроЭВМ и внут- сбрасывает триггер 43. При этом сигнал ренними узлами микропроцессора отла- логической 1 с нулевого выхода триггера 43 блокирует элемент ИЛИ 47 и на на шине Готов управляющей микроЭВМ

устанавливается логическая 1. После в регистре 29 снимаются сигналы этого управляющая микроЭВМ заканчивает Сброс, Запрос прямого доступа, свой цикл выдачи информации. После то- Блокировка и устанавливается уро- го, как микропроцессор отлаживаемой микроэвм закончил свой цикл, он вьщает сигнал Подтверждение прямого дос-40 начинает выполнять программу, тупа уровня логической 1 на управ- Информация с шин отлаживаемой микроЭВМ через блоки элементов И 36-39, которые стробируются в соответствии с выражениями (4) и (5) поступает на 45 внутренние шины устройства отладки. Информация с адресных и информационных шин поступает на информационные входы блоков памяти адреса 15 и данных 16. Запись информации в эти бло- 50 ки производится сигналами приема или вьщачи информации отлаживаемой микро- ЭВМ (выходы 116). Сигналом начала машинного цикла отлаживаемой микро- ЭВМ на управляющем входе 128 содер- приема информации из внутренних узлов 55 жимое счетчика 8 увеличивается на 1. микропроцессора отлаживаемой микро- Таким образом, информация о состоянии ЭВМ, последний соответственно произ- адресных и информационных шин отла- водит цикл выдачи информации. Начало живаемой микроЭВМ в следующем машин- обращения протекает так же, как в ном цикле запишется в следующие ячейживаемой микроЭВМ управляющая микро- ЭВМ переводит устройство отладки в режим прогона программы. Для этого

вень логической 1 сигнала Готов. Микропроцессор отлаживаемой микроЭВМ

уровня логической 1 ляющий вход 127. Этот сигнал по R- входу сбрасывает триггер 44. На единичном выходе этого триггера появляется логический О и на шине 122 Запрос прямого доступа также устанавливается логический О, т.е. сигнал Запрос прямого доступа снимается. После этого сигнал Подтверждение прямого доступа также снимается и микропроцессор отлаживаемой микроЭВМ переходит в состояние ожидания (низкий уровень сигнала Готов). Когда управляющая микроЭВМ выполняет цикл

1315984

10

описанном режиме, После установки триггеров 43 и 44 в состояние 1 при появлении сигнала приема информации уровня логической 1 на одном из управляющих входов 108 блокируется элемент ИЛИ 47 и устанавливается сигнал на входе уровня логической 1 Готов управляющей микроЭВМ. После этого управляющая микроЭВМ заканчин на входе Готов отлаживаемой микроэвм появляется сигнал уровня логической 1. После этого микропроцессор отлаживаемой микроЭВМ заканчивает

вает цикл приема информации и задним фронтом сигнала приема информации че- рез элемент ИЛИ 41 сбрасывает по С- входу триггер 43. При этом на выходе элемента И 48 появляется логическая 1, которая блокирует элемент ИЛИ 49

цикл выдачи информации и вьщает на управляющий вход 127 сигнал Подт- снимаются ( логический О) и микропроцессор отлаживаемой микроЭВМ пере- ходит в состояние ожидания, После обмена информацией с внут- ренними блоками устройства отладки, памятью отлаживаемой микроЭВМ и внут- ренними узлами микропроцессора отла-

верждение прямого доступа, сбрасывающий триггер 44, При этом сигналы Запрос прямого доступа и Готов

цикл выдачи информации и вьщает на управляющий вход 127 сигнал Подт- снимаются ( логический О) и микропроцессор отлаживаемой микроЭВМ пере- ходит в состояние ожидания, После обмена информацией с внут- ренними блоками устройства отладки, памятью отлаживаемой микроЭВМ и внут- ренними узлами микропроцессора отла-

цикл выдачи информации и вьщает на управляющий вход 127 сигнал Подт- снимаются ( логический О) и микропроцессор отлаживаемой микроЭВМ пере- ходит в состояние ожидания, После обмена информацией с внут- ренними блоками устройства отладки, памятью отлаживаемой микроЭВМ и внут- ренними узлами микропроцессора отла-

живаемой микроЭВМ управляющая микро- ЭВМ переводит устройство отладки в режим прогона программы. Для этого

в регистре 29 снимаются сигналы Сброс, Запрос прямого доступа, Блокировка и устанавливается уро- начинает выполнять программу, Информация с шин отлаживаемой микроЭВМ через блоки элементов И 36-39, которые стробируются в соответствии с выражениями (4) и (5) поступает на внутренние шины устройства отладки. Информация с адресных и информационных шин поступает на информационные входы блоков памяти адреса 15 и данных 16. Запись информации в эти бло- ки производится сигналами приема или вьщачи информации отлаживаемой микро- ЭВМ (выходы 116). Сигналом начала машинного цикла отлаживаемой микро- ЭВМ на управляющем входе 128 содер- жимое счетчика 8 увеличивается на 1. Таким образом, информация о состоянии адресных и информационных шин отла- живаемой микроЭВМ в следующем машин- ном цикле запишется в следующие ячейвень логической 1 сигнала Готов. Микропроцессор отлаживаемой микроЭВМ

1113

ки блоков памяти адреса 15 и данных 16.

На вторые информационные входы коммутатора 1 поступают сигналы с четырех старших адресных шин отлаживаемой микроэвм (группа шин 115), определяющие, номер сегмента памяти отлаживаемой микроэвм, а на вторые информационные входы компаратора 6 поступают сигналы с восьми младших адресных шин отлаживаемой микроЭВМ (группа шин 118)j .определяющие номер адресуемого порта ввода-вывода. В режиме прогона программы сигналы t четырех старших адресных шин отлаживаемой микроэвм через коммутатор 1 поступают на адресные входы блока 9 памяти переадресации. Выбор блока 9 памяти переадресации или компаратора 6 определяется сигналом признака обращения к порту ввода-вывода отлаживаемой микроэвм, поступающим на управляющий вход 125. Если этот сигнал имеет уровень логического О (обращение к памяти) , то по входу 64 включается блок 9 памяти переадресации. Если этот сигнал имеет уровень логической 1 (обращение к порту ввода-вывода), то включается компаратор 6. При обращении к памяти из блока 9 памяти переадресации считывается записанная в режиме управления информация о текущем сегменте памяти отлаживаемой мик- роЭВМ. Если сегмент памяти, номер которого установлен, защищен, на выходе 67 блока 9 памяти переадресации считывается логическая 1, которая через элементы ИЛИ 18 и 45 и управляющий вход 120 устанавливает сигнал Запрос Прерывания для управляющей микроэвм, а через элемент ИЛИ 60 - сигнал Запрос прямого доступа для отлаживаемой микроЭВМ. Выполнение про граммы микропроцессором отлаживаемой микроэвм прекращается, ;а сигнал Запрос Прерывания сигнализирует управляющей микроэвм о необходимости перевода устройства отладки в режим управления. Если сегмент памяти находит ся в управляющей микроЭВМ, то на выходе 66 блока 9 памяти переадресации считывается логическая 1, которая через управляющий вход 131 вырабатывает сигнал Запрос прямого доступа для управляющей микроЭВМ, инициирующий прямой доступ к памяти управляю-, щей микроэвм и стробирующий блоки элементов И 25-27. Код номера сегмента памяти, к которому должно про98412

изводиться обращение (старшие четыре разряда адреса), считывается с выходов 65 блока памяти переадресации 9 и поступает на первые входы группы элементов И 26, Этот код номера сегмента, а также одиннадцать младших разрядов адреса (не модифицируемые) и сигналы приема и выдачи информации через блоки элементов И 25 и 27 посO тупают на соответствующие шины управляющей микроэвм. В случае чтения информации из памяти управляющей микро- ЭВМ в соответствии с вьфажением (3) стробируется блок элементов И 35,

5 и информация из памяти управляющей микроэвм считывается на информационные шины отлаживаемой микроЭВМ. В случае записи информации в память управляющей микроЭВМ в соответствии

Q с выражением (1) стробируется блок элементов И28 и информация с информационных шин отлаживаемой микроЭВМ поступает на информационные шины управляющей микроэвм.

5

При обращении к порту ввода-вывода включается компаратор 6. При сов- |падении адреса порта ввода-вывода, к которому производится обращение,

0 с адресом имитируемого порта, храня- пщмся в регистре 5, на выходе компаратора 6 появляется .сигнал уровня логической 1. Этот сигнал включает блоки памяти констант 10 и временных

,, интервалов 11. Код временного интервала из последнего тем же сигналом заносится в счетчик 12. Кроме того, сигнал с выхода компаратора 6 устанавливает по S-входу триггер 19 и

0 импульсы с выхода генератора 22 через элемент И 21 начинают поступать на счетный вход счетчика 12. Если производится, обращение к устройству ввода, то информация из блока 10 памяти

констант через блок элементов И 17, который стробируется сигналом приема информации отлаживаемой микроЭВМ по входу 75 и сигналом с выхода компа- ратора 6 к входу 77 считывается на

Q информационные шины отлаживаемой микроэвм. Если производится обращение к устройству вывода, то информация с информационных шин отлаживаемой микроэвм, поступающая на внутренние

информационные шины устройства отладки, через коммутатор 3 записывается в блок 10 памяти констант.

Счетчик 12 производит подсчет времени между обращениями к имитируемому

устройству ввода-вывода. После того, как в счетчик занесен код временного интервала из блока памяти временных интервалов начинается реверсивный счет импульсов, поступающих от гене- ратора 22. .

Превышение промежутком времени между обращениями отлаживаемой микро- ЭВМ к имитируемому порту того отрезка времени, который задан кодом вре- менного интервала, квалифицируется как ошибка. В этом случае счетчик 12 считает до нуля и сигнал с его выхода заема устанавливает триггер 20. Сигнал с единичного выхода этого тригге- pa через элементы ИЛИ 18 и 45 устанавливает сигнал Запрос прерывания для управляющей микроЭВМ, а через элемент ИЛИ 50 - сигнал Запрос прямого доступа для отлаживаемой микроЭВМ. Вы- полнение программы микропроцессором отлаживаемой микроЭВМ прекращается.

После окончания обращения к имитируемому порту ввода-вывода задним фронтом сигнала с выхода компаратора 6 содержимое счетчика 4 увеличивается на единицу и при следующем обращении к имитируемому устройству ввода-вывод производится обращение к следующей -Ячейке блоков памяти констант и вре- манных интервалов.

На входы 105 и 106 блока 51 сравнения поступают адресные сигналы отла- Асиваемой микроЭВМ, где они сравниваются с адресами точек останова пр.огона программы, записанными в режиме управления. При совпадении текущего адреса, .установленного на шинах отлаживаемой микроэвм, с адресом одной из точек останова, на выходе блока сравнения вырабатывается сигнал уровня логической 1, устанавливающей через элемент ИЛИ 45 и управляющий вход 120 сигнал Запрос прерывания для управляющей микроэвм, а через элемент ИЛИ 50 и управляюш;ий вход 122 - сигнал Запрос прямого доступа для отлаживаемой микроэвм. После получения сигнала Запрос прерывания управляющая микроэвм переводит устройство от- ладки в режим управления и производит анализ кода выполнения программы, информация о котором записана в блоках памяти адреса 15 и данных 16.

Формула изобретения

Устройство для отладки программно- аппаратных блоков, содержащее коммутатор адреса, блок памяти переадресации, четырнадцать блоков элементов И, элемент 2И-ИЛИ, коммутатор управляющих сигналов, блок синхронизации, первый и второй регистры, первьш дешифратор, первый счетчик, блок памяти данных, блок памяти адресов, блок сравнения, три элемента И, пять элементов ИЛИ, одновибратор и два триггера, причем первьй выход блока синхронизации через входную шину синхронизации устройства соединен с тактовь входом дешифратора, с первым управляющим входом коммутатора управляющих сигналов, входом признака прямого дос тупа,, блока памяти переадресации, с первым входом первого, второго и третьего блоков элементов И, с первым . информационным входом коммутатора управляющих сигналов, с первым входом элемента 2И-ИЛИ, с выходом третьего блока элементов И, с первым входом записи блока памяти переадресации, с вторым входом элемента 2И-ИЛИ, с первым входом записи первого регистра, с вторым информационным входом коммутатора управляющих сигналов, с входом разрешения блока сравнения, с первым входом четвертого блока элементов И и с первыми входами первого, второго и третьего элементов ИЛИ, с входами третьего и четвертого элементов ИЛИ и с первым входом первого элемента И, первьш, второй и третий тактовые входы блока синхронизации через входную шину синхронизации соер,и пены с тактовыми входами устройства,информационные входы блока памяти переад ресации через входную шину данных устройства соединены с первым входом пятого блока элементов И, первым информационным входом блока сравнения, информационными входами первого и второго регистров и выходами шестого, седьмого и восьмого блоков элементов И, выходы первого и второго блоков элементов И через входную шину адреса устройства соединены с первыми входами девятого и десятого блоков элементов И, с вторым информационным входом блока сравнения, с входом за- пуска блока синхронизации, информационным входом первого счетчика, первыми входами седьмого и восьмого блоков элементов И, первым информационным входом коммутатора адреса и вто- рым входом записи первого регистра, счетный вход первого счетчика через выходную шину синхронизации устройст,15

131598

ва соединен с входом установки в О первого триггера, с третьим управляющим входом коммутатора управляюпщх сигналов, с вторым входом первого элемента ИЛИ, вторым входом записи блока памяти,переддресации, выходом четвертого блока элементов И с первым входом одиннадцатого блока элементов И, с выходами второго и пятого элементов ИЛИ, с первым входом второ- щ го элемента И, тактовым входом первого триггера, входом установки в О второго триггера и с первым и вторым разрядными выходами первого регистра, выход одиннадцатого блока j элементов И через внутреннюю двунаправленную шину синхронизации соединен с третьим входом элемента 2И- ИЛИ, вторым входом третьего блока элементов И, и входами записи блоков 2Q памяти адреса и данных, выход двенадцатого блока элементов И -через внутреннюю шину данных соединен с первым .входом шестого блока элементов И и

информационными входами блока памяти, 25 блока элементов И, выходы девя- выходы тринадцатого и четырнадцатого того и десятого блоков элементов И

через выходную шину адреса соединены с вторыми входами тринадцатого и чеблоков элементов И через внутреннюю ршну адреса соединены с вторым входом второго блока элементов И, вторым информационным входом коммутатора JQ ответственно, информационный выход адреса, информационным входом блока блока памяти переадресации соединен

тырнадцатого блоков элементов И со-

памяти адреса и с третьим информационым входом блока сравнения, выход равенства которого соединен с первым входом.четвертого элемента ИЛИ первый выход первого дешифратора соединен с третьим входом записи блока переадресации и управляющим входом коммутатора адреса, выходы которого соединены с адресными входами блока памяти переадресации, второй выход первого дешифратора соединен с вторы входом второго элемента И, четвертым входом элемента И-ИЛИ, с вторым информационным входом коммутатора управляющих сигналов, первый выход которого соединен с вторыми входами четвертого, девятого и десятого блоков элементов И, второй и третий выходы коммутатора управляющих сигналов п Ционные входы первого и второго |соединены соответственно с вторым триггеров соединены с шиной нулевого, входом пятого блока элементов И и потенциала устройства, выходы первого первым входом двенадцатого блока и третьего.элементов И соединены с элементов И, четвертый выход коммута- вторым и третьим входами пятого эле- . тора управляюпщх сигналов соединен „манта ИЛИ, отличающееся с вторым входом, одиннадцатого блоков тем, что, с целью расширения функ- элементов И и первыми входами тринад- циональных возможностей устройства цатого и четырнадцатого блоков эле- за счет имитации временных характе- ментов И, третий выход первого де- ристик блоков ввода-вывода отлаживае1315984

16

шифратора соединен с вторым входом разрешения блока .сравнения и третьим входом записи первого регистра, третий и четвертый выходы которого соединены соответственно с первым входом пятого элемента ИЛИ и вторым входом второго элемента ИЛИ, четвертый выход первого дешифратора соединен с вторыми входами седьмого и восьмого блока элементов И и входом записи первого счетчика, выходы которого соединены с адресными входами блоков памяти адреса и данных, выходы которых соединены с третьими входами соответственно седьмого и восьмого элементов И, второй выход блока синхронизации соединен с входом записи второго регистра, выход которого соеди- нен с адресным входом первого дешифратора, выход элемента 2И-ИЛИ соединен с вторым входом шестого блока элементов И, выход пятого блока элементов И чере з выходную шину данных соединен с вторыми входами двенадцаответственно, информационный выход блока памяти переадресации соединен

тырнадцатого блоков элементов И со-

35

с вторым входом первого блока элементов И, выход второго элемента И через одновибратор соединен с единичными входами первого и второго триггеров, прямой выход второго и инверсный выход первого триггеров соединены соответственно с вторым входом первого элемента И и третьим инфор Q мационным входом коммутатора управ- ляюЕцнх сигналов, выход первого эле-i мента ИЛИ соединен с тактовым входом второго триггера, инверсный выход которого соединен с вторым входом

третьего элемента ИЖ и первым входом третьего элемента И, прямой выход первого триггера соединен с вторым входом третьего элемента И и третьим , входом второго элемента ИЛИ, информаМОго устройства, в устройство введены второй и третий счетчики, второй дешифратор, третий регистр, компаратор, ко1 мутатор констант и блоки памяти констант и временных интервалов, тре- тий и четвертый триггеры, генератор импульсов, шестой элемент ШТИ, четвертый элемент И и пятнадцатый блок элементов И, причем выход пятнадцатого блока элементов И соединен с вто- рым входом двенадцатого блока элементов И, второй информационный выход блока памяти переадресации соединен с

тов И через входную шину синхронизации соединен с входами записи блоков .памяти констант и временных интервалов, выход двенадцатого блока соединен с вторым информационным входом коммутатора констант, выход которого соединен с информационным входом блока памяти констант, выход тринадцатого блока элементов И через внутреннюю шину адреса соединен с первьми информационными входами компаратора, выход которого соединен с вторым входом обращения блока памяти временных интервалов, третьим входом обращения блопервым входом -шестого элемента ИЛИ, выход которого соединен с вторым вхо- 15 ка памяти констант, счетным входом дом четвертого элемента ИЛИ, выход второго счетчика, третьим входом пятнадцатого блока элементов И, единичным входом третьего триггера и входом записи третьего счетчика, выход переполнения которого соединен с единичным входом четвертого триггера, пятый выход первого дешифратора соединен с

одиннадцатого блока элементов И через внутреннюю двунаправленную шину синхронизации соединен с первым входом пятнадцатого блока элементов И, первым входом обращения блока памяти констант, выход которого соединен с вторым входом пятнадцатого блока эле20

тактовьгм входом второго дешифратора и нулевыми входами третьего и четвертотактовьгм входом второго дешифратора нулевыми входами третьего и четверто

ментов И, выход первого блока элементов И через входную шину адреса сое- 25 го триггеров, прямые выходы которых динен с информационными входами второ- соединены соответственно с первым го счетчика и второго дешифратора, первый, второй, третий и четвертый выходы которого соединены соответствходом четвертого элемента И и вторы входом шестого элемента ИЛИ, выход генератора импульсов соединен с втовременных интервалов, вторым входом обращения блока памяти констант, и входом записи третьего регистра, выход

венно с входом записи второго счетчи- 30 Рьм входом четвертого элемента И, вы- ка, входом обращения блока памяти ход которого соединен со счетньм входом третьего счетчика, третий выход второго дешифратора соединен с управляющим входом коммутатора констант, шестого блока элементов И череа вход- 35 второго счетчика соединен с ад- ную шину данных соединен с первым ин- ресными входами блоков памяти кон- формационным входом коммутатора констант, информационными входами третьего регистра и блока памяти временных интервалов, выход которого соединен с информационным входом третьего счетчика, выход третьего блока элеменстант и временных интервалов, выход третьего регистра соединен с вторым информационным входом компаратора, вы- 40 ход четвертого блока элементов И

через выходную шину синхронизации соединен с входом разрешениякомпаратора.

тов И через входную шину синхронизации соединен с входами записи блоков .памяти констант и временных интервалов, выход двенадцатого блока соединен с вторым информационным входом коммутатора констант, выход которого соединен с информационным входом блока памяти констант, выход тринадцатого блока элементов И через внутреннюю шину адреса соединен с первьми информационными входами компаратора, выход которого соединен с вторым входом обращения блока памяти временных интервалов, третьим входом обращения блока памяти констант, счетным входом второго счетчика, третьим входом пятнадцатого блока элементов И, единичны входом третьего триггера и входом записи третьего счетчика, выход переполнения которого соединен с единичным входом четвертого триггера, пятый выход первого дешифратора соединен с

тактовьгм входом второго дешифратора и нулевыми входами третьего и четвертого триггеров, прямые выходы которых соединены соответственно с первым

го триггеров, прямые выходы которых соединены соответственно с первым

входом четвертого элемента И и вторым входом шестого элемента ИЛИ, выход генератора импульсов соединен с вто30 Рьм входом четвертого элемента И, вы- ход которого соединен со счетньм входом третьего счетчика, третий выход второго дешифратора соединен с управляющим входом коммутатора констант, 35 второго счетчика соединен с ад- ресными входами блоков памяти кон-

стант и временных интервалов, выход третьего регистра соединен с вторым информационным входом компаратора, вы 40 ход четвертого блока элементов И

через выходную шину синхронизации соединен с входом разрешениякомпаратора.

:f la.

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании микроЭВМ, М1 кроконтроллеров и других устройств 1на базе микропроцессоров. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения имитации информационных потоков. Устройство содержит ко мута- тор адреса, дешифратор, коммутатор констант, счетчик, регистр, компаратор, блок синхронизации, счетчик, блок памяти переадресации, блок памяти констант, счетчик, регистр, дешифратор, блок памяти адреса, блок памяти данных, блоки элементов И, элементы ИЛИ,триггеры, элементы И, генератор, регистр, элемент 2И-ИЛИ, коммутатор управляющих сигналов, од- новибратор.и блок сравнения. Устройство обеспечивает два режима работы - .режим управления и режим прогона (Программы. 2 ил. (Л со ел о 00 4;

| Справочник по цифровой вычислительной технике | |||

| Под редакцией Б.Н | |||

| Малиновского Т.З | |||

| Техника, 1981, с.125-145 | |||

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-04-24—Подача