pa пуска, выход первого триггера пуска соединен с первыми входами седьмого элемента ИЛИ и шестого элемента И, выход которого соединен с вторым входом шестого элемента ИЛИ, единичный вькод первого триггера ответа соединен с первым входом седьмого элемента И и Л-входом второго триггера ответа, выход которого соединен с вторым входом седьмого элемента И, выходы шестого и седьмого элементов ИЛИ соединены соответственно с первым входом восьмого элемента И и J-входом второго триггера пуска, нулевой выход которого соединен с первыми Rвходами первого и второго триггеров управления и первым входом первого элемента ИЛИ каждого из блоков задания интервалов, прямьм входом девятого элемента И, вторым входом восьмого элемента И, Входом сброса таймера, R -входом триггера конца цикла и вторым входом .пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен с первым входом первого и четвертого элементов ИЛИ, выход восьмого элемента И соединен с С-входом второго триггера пуска, единичный выход которого соединен с первы14И входами десятого и одиннадцатого элементов И, группа информационных выходов блока задания режимов соединена с первыми входаьш элементов И третьей группы, выходы которых соединены с инверсными входами элементов второй группы и группой информационных входов счетчика циклов, выходы элементов И второй группы соединены с группой входов сброса счетчика циклов, выходы переполнения которого соединены с вторым входом третьего элемента И и инверсным входом третьего элемента И

выход которого соединен с первым входом блока индикации, третья группа выходов блока памяти соединена с первыми входами элементов И четвертой группы, выходы которых соединены с группой информа1шонных входов интервалов каждого иэ блоков задания интервалов, выход третьего элемента И соединен с первым входом двенадцатого элемента И и с входом триггера конца программы, выход которого соединен с вторьм входом двенадцатого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ,выход переполнения счетчика циклов соединен с вторым входом блока индикации, вькод сбро.са блока задания режимов соединен с вторьм входом восьмого элемента ИЛИ и первым входом второго элемента ЕГШ, выход останова блока задания режимов соединен с третьим входом восьмого элемента ИЛИ, выход которого соединен с R-входами первого и второго триггеров пуска, выход приведения в исходное состояние блока задания режимов соединен с четвертым входом восьмого элемента ИЛИ и вторым входом второго элемента ИЛИ, выход которого соединен с вторыми входами элементов И третьей группы и с R входом триггера контроля, выход пуска блока задания режимов соединен с вторым входом седьмого элемента ИЛИ, первыми входами четвертого и пятого элементов И, выход установки режима блока задания режимов соединен с третьим, входом двенадцатогоэлемента И и вторым входом третьего элемента ИЛИ, выход которого соединен с Р -входом триггера конца программы, первый выход блокировки блока задания режимов соединен с вторым входом первого элемента ИЛИ, вторьми R-входами первого и второго триггеров управления и вторым входом первого элемента ИЛИ первого блока задания интервалов, выход первого элемента И которого соединен с первым входом тринадцатого элемента И и с первым входом первой группы входов блока сравнения, выход тринадцатого элемента И соединен с вторыми входами элементов И четвертой группы, второй выход блокировки блока задания режимов соединен с вторым входом четвертого элемента ИЛИ и R-входами первого и второго триггеров управления второго блока задания интервалов, выход первого элемента И которого соединен с вторым входом тринадцатого, элемента И и первым входом второй группы входов блока сравнения, выход синхронного режима пуска блока задания режимов соединен с вторыми входами четвертого и пятого элементов И, выход тринадцатого, четырнадцатого и пятнадцатого эле ментов И и девятого элемента ИЛИ соединены соответственно с входаьв стробирования, пуска, тактовь(м и сброса таймера, второй выход блока синхронизации соединен с первыми входа ш первого и второго элементов И и с входами второго триггера управления первого блока задания интервалов, выход первого ШШ которого соединен с входом сброса счетчика первого блока задания интервалов , первым входом девятого элемента ИЛИ и вторым входом первой группы входов блока сравнения, третий выход блока синхронизации -соединей с С-входом первого триггера пуска, третьим входом четвертого элемента .И и вторым входом одинад(атого элемента И, выход которого соединен с первым входом пятнадцатого элемента И и с первыми входами третьего и четвертого элементов И первого блока задания интервалов, четвертый выкод блока синхронизации соединен с первыми входами первого и второго элементов И и с входами второго триггера управления второго блока задания интервалов, выход первого элемента {ЦЩ которого соединен с входом сброса счетчика интервалов второго блока задания интервалов, вторым входом девятого элемента ШШ и вторьм входом второй группы входов блока сравнения пятый выход блока синхронизации соединен с пятым входом четвертого элемента И и вторым входом десятого элемента И, выход которого соединен с вторым входом пятнадцатого элемента и первыми входами третьего и четвертого элементов И второго блока задания интервалов, шестой выход блока синхронизации соединен с вторым входом шестого элемента К« седьмой выход блока синхронизации соединен с -входом триггера конца программы и J -входом первого триггера управлени первого и второго блоков задания интервалов, выходы вторых элементов ИЛ которых соедииешл соответственно с первыми и втор1«ш входаьв четырнадцатого элемента И, выход второго элемента ШШ первого блока задания интервалов соединен с J- и инверсными К-входаш; второго триггера управлени этого блока, группой синхровходов первого регистра и третьим входом первой группы входов блока сравнения выход несравнения которого соединен с J-входом триггера контроля,восьмой выход блока синхронизации соединен с С-входами первого и второго триггеров ответа, выход второго элемента ИЛИ второго блока задания интервалов соединен с J- и инверсными К-входами второго триггера управления второго блока задания интервалов, синхровходом второго регистра и третьим входом второй группы входов блока сравнения, информационные выходы первого и второго регистров соединены с информационными вяодами соответственно первой и второй групп блока сравнения, вход реакции объекта управления устройства соединен с информационным входом блока сравнения, информационный выход которого соединен с третьим входом седьмого элемента И, R-входом второго триггера ответа, J - и R входами первого триггера ответа, нулевой выход которого соединен с Rвходом второго триггера ответа, выход седьмого элемента И соединен с первым выходом второго элемента ИЛИ каяЕДОго из блоков задания интервалов, К-входы первого и второго триггеров пуска, триггера конца програм в I, первого триггера ответа, триггера контроля и первого триггера управления каждого из блоков задания интервалов соединены с шиной нулевого потенциала, выход триггера контроля соединен с третьим входом блока индикации и пятым входом восьмого

элемента ИЛИ, выход второго триггера управления каждого из блоков задания интервалов соединен с вторыми входами первого и второго элементов И соответствугацего блока задания интервалов, выход второго элемента И каждого из блоков задания интервалов соединен с третьим входом первого элемента ИЛИ соответствующего блока задания интервалов, выход третьего элемента И каждого из блоков задания интервалов соединены с С-входом первого триггера управления и вторым входом второго элемента ИЛИ соответствующего блока задания интервалов, единичный и нулевой выходы первого триггера управления каждого из блоков задания интервалов соединены с вторыми входами соответственно четвертого и третьего элементов И соответствующих блоков задания интервалов, выход четвертого элемента каждого из блоков задания интервалов соединен с синхровходом счетчика интервалов и первым входом пятого элемента И соответствующего блока задания интервалов выход счетчика интервалов каждого из блоков задания интервалов соединен с. nropifM входом пятого элемента И соответстующего блока задания иптерпалов, вы.ход пятого элемента И каждого из блоков задания интервалов соединен с

третьим входом второго элемента ИЛИ соответствующего блока задания интервалов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля схем сравнения | 1984 |

|

SU1228107A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для формирования тестов | 1985 |

|

SU1297059A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ С КОНТРОЛЕМ, содержащее блок синхронизации, блок задания режимов, таймер, блок памяти, первый регистр, счетчик циклов, коммутатор, блок сравнения, первую и вторую группы элементов И, первый, второй, третий и четвертый элементы ИЛИ, причем выход первого элемента ИЛИ соединен с входом сброса первого регистра, выходы которого соединены с первыми входами элементов И первой группы, первая группа выходов блока памяти соединена с группой информационных входов таймера, выход которого соединен с управляющим входом коммутатора, выходы коммутатора являются выходами устройства, выход второго элемента ИЛИ соединен с первым вхо- дом третьего элемента ИЛИ и прямыми входами элементов И второй группы, вбкод сброса блока задания режимов соединен с входом запуска блока синхронизации, от.личающееся тем, что, с целью увеличения глубины контроля, в устройство введены второй регистр, первый и второй триггеры пуска, первый и второй триггеры ответа, триггер контроля, триггер конца программы, триггер конца цикла, третья и четвертая группы элементов И, пятнадцать элементов И, пять элементов ИЛИ, первый и второй блоки задания интервалов, каждый из которых содержит счетчик интервалов, первый и второй триггеры управления, пять элементов И, первьй и второй элементы ИЛИ, причем выход четвертого элемента ИЛИ соединен с входом сброса второго регистра, выходы ко(Л торого соединены с вторыми входами элементов И группы, выходы элементов И первой группы соединены с соответствующими адресными входами блока памяти, вторая группа выходов которого соединена с группой информационных входов коммутатора, выход блока памяти соединен с первым входом перел вого элемента И, выход которого соеОд динен J- и К-входами триггера коно ца цикла, первый выход блока сннхро.шзации соединен с первыми входами 4 второго и третьего элементов И, с входами триггера контроля и триггера конца цикла, выход которого соединен с вторым входом второго элемента И, выход таймера соединен с вторым входом первого элемента И и третьим входом второго элемента И, выход которого соединен со счетным входом счетчика циклов и аервым входом пятого элемента ИШi, выходы четвертого и пятого элементов И соединены соответственно с первым входом шестого элемента ИЛИ и J-входом псроого тригге

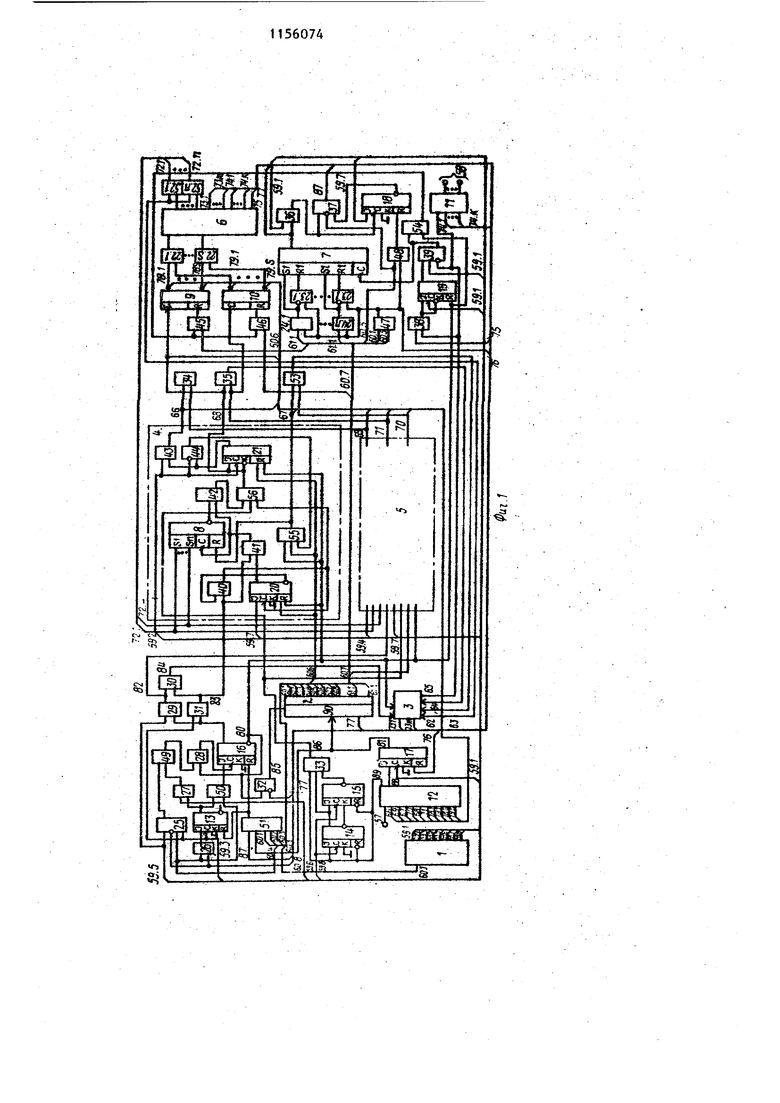

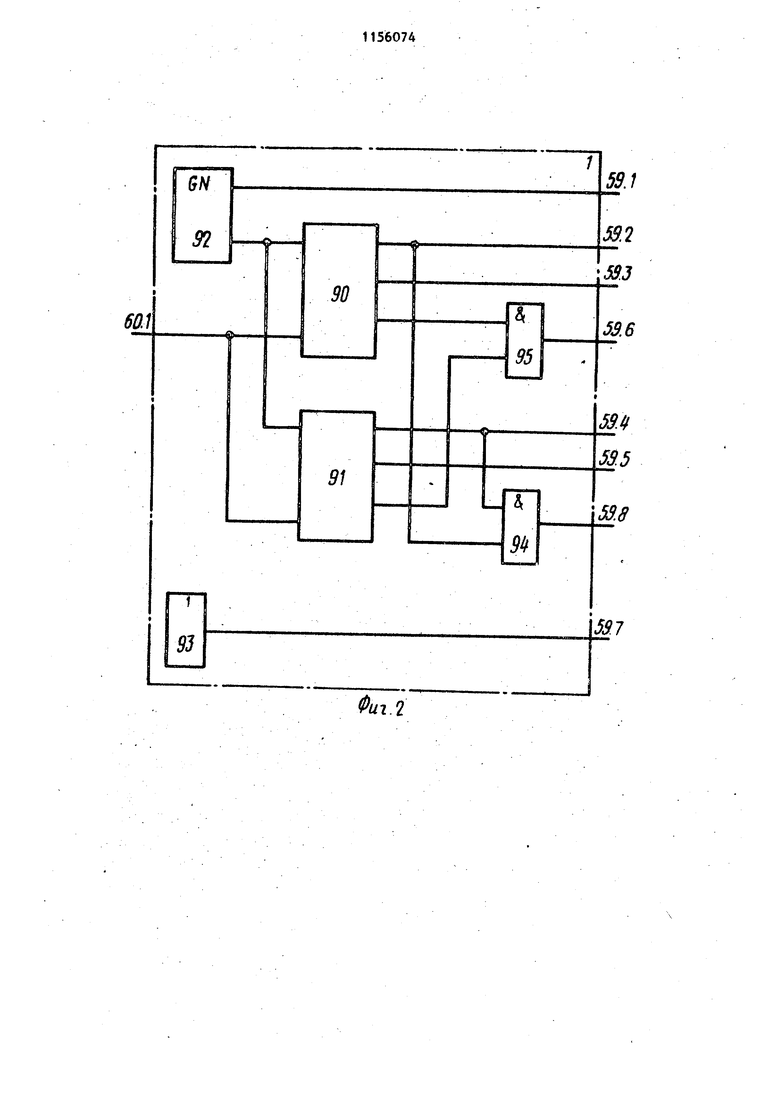

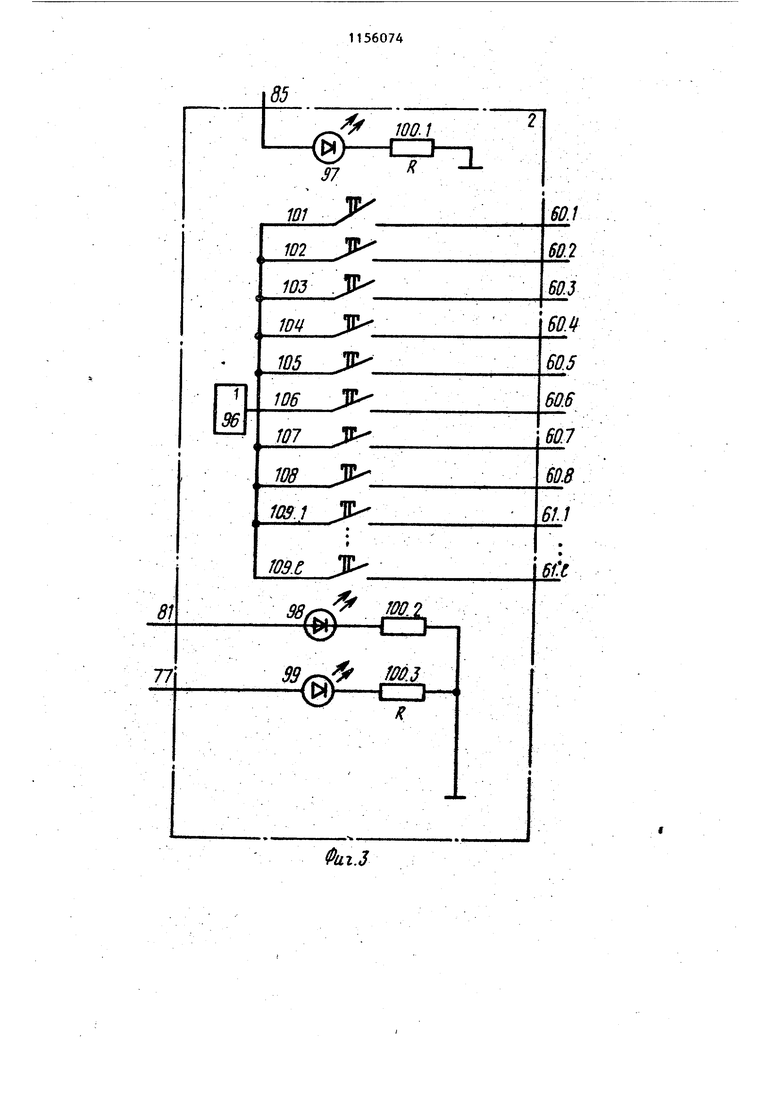

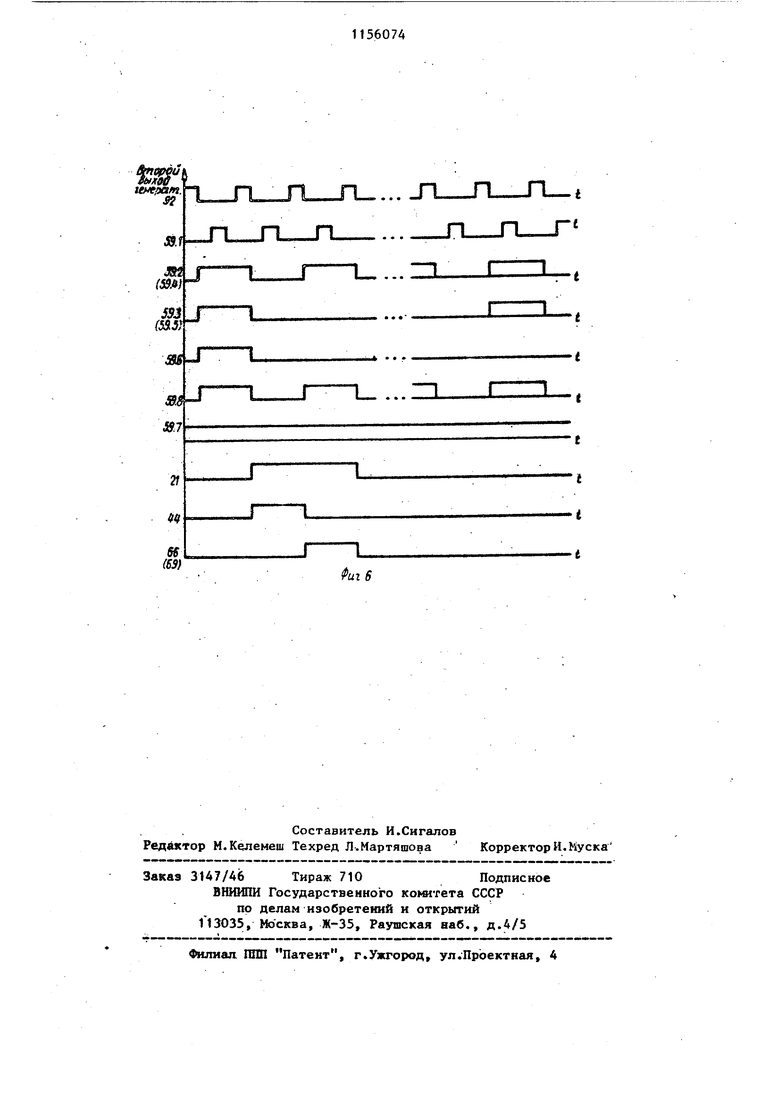

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении программируемых формирователей управляющих и тестовых воздействий для автоматизированныхь систем контроля и управления технологическими процессами. Цель изобретения - увеличение глубинь контроля на вход устройства для обеспечения асинхронгой выдачи тестовых и управляющих воздействий. Введение триггеров конца цикла и конца программы соответствующих им элементов И, ИЛИ и обусловленных ими связей дает возможность управлят формированием сигналов окончания цик ла и программы вьэдачи тестовых и управляющих воздействий. Введение третьего блока элёментрв И и обусловленных им связей обес печивает управление записью информации в счетчик циклов. Введение четвертого блока элементов И и обусловленных ими связей позволяет передачу кода длительности интервалов из блока памяти в блоки задания интервалов. На фиг.1 представлена функциональная схема устройства для управле ния с контролем; на фиг.2 - то же, блока синхронизации; на фиг.З - то же, пулЬта управления и индикации-, на фиг.А - функциональная схема тайтмера;- на фиг.5 - то же, блока сравн ния; на фиг.6 - временная диаграмма работы блока синхронизации и блока задания интервалов. Устройство для управления с конт ролем содержит блок 1 синхронизации блок 2 задания режимов, таймер 3, первый, 4 и второй 5 блоки задания интервалов, блок 6 пнмяти, счет чик 7 циклов, счетчик 8 интерв лов блока 4, первый 9 и второй 10 регистры, коммутатор 11, блок 12 сравнения, первьм 13 триггер пуска, первый -14 и второй 15 триггеры отве та, второй 16 триггер пуска, тригге 17 контроля, триггер 18 конца программы, триггер 19 конца цикла, первьй 20 и второй 21 триггеры управления блока 4, первьй 22, второй 23 и третий 24 блоки элементов И, четвертый 25, пятьш 26, шестой 27, восьмой 28, десятый 29, пятнадцатый 30, одиннадцатый 31, десятый 32, седьмой 33, тринадцатый 34, четырнадцатый 35,третий 36, двенадцатый 37, первый 38, второй 39 элементы И устройства, третий 40, четвертый 41, первый 42, второй 43 и пятьй 44 элементы И блока 4, первьй 45, четвертый 46, второй 47, третий 48, шестой 49, седьмой 50, восьмой 51 элементы ИЛИ устройства, четвертый блок элементов И 52, девятьй 53, пятьй 54 элементы ИЛИ, первьй 55 и второй 56 элементы ИЛИ блока 4. На фиг.1-2 использованы также следугадие обозначения: вход 57 устройства, группа выходов 58 устройства, первьй - седьмой выходы 59.159.8 соответственно блока1 синхронизации, первый - восьмой выходы 60.1-60.8 блока 2, группы выходов 61.1-61.г кода числа циклов блока 2, второй 62, пятый 63 и третий 64 входы таймера 3, выход 65 таймера 3, выходы 66 элемента И 43, выходы 67 и 68 элементов ИЛИ 55 и 56 первого 4 блока задания интервалов соответственно, выходы 69-71 второго 5 блока задания интервалов, выходы 72.1-72.п четвертого блока элементов И 52, первая группа выходов 73.1 73.m блока 6 памяти, вторая группа выходов 74.1-74.п кода блока 6 памяти, вькод 75 конца цикла блока 6 памяти, выход 76 элемента ИЛИ 47, выход 77 счетчика 7 циклов, выхода 78.1-78.9 первого 9 регистра, выходы. 79.1-79.5 второго 10 регистра, инверсный выход 80 второго 16 триггера пуска, выход 81 триггера 17 контроля, выходы 82-87 десятого 29j один надцнтого 31 и пятнадцатого 30 девятого 32, седьмого 33 и двенадцатого 37 элементов И соответственно, первый 88 и второй 89 выходы блока 12 .сравнения. Блок 1 синхронизации (фиг.2) со держит первый 90 и второй 91 распределители импульсов, генератор 92 импульсов, генератор 93 единицы, пер вый элемент И 94 и второй элемент И 95.. Блок задания режимов (фиг.З) содержит генератор 96единш9 1, первый 97 и второй 98 и третий 99 элементы индикации, первый 100.1 - третий 100.3 резисторы огра1шчения тока, первьМ 101 - восьмой 108 выклхучатели для 9адаю1я управляющих воэдействий, группа выключателей 109.1 109.f для эадан1М кода числа циклов. Тлймер 3 (4в1Г.4) содержит триггер 110, боок элементов И 111, первый 112 и второй 113 элементы И, элемент ИЛИ 114, и счетчик 115. Щюк 12 сравнения (г.5) содер жит перв 116 и второй 117 коммутаторы, схему 118 сравнения, блок элементов И 119 и элемент ИШ 120. Обозначения на временной диаграмме (.6) соответствуют номерам выходов или номерам элементов, которые введены на функциональной схеме УСТрОЙСТВ41 фИГ.1. I. Назначение основных элементов уст ройства для управления и контроля. Блок 1 синхронизации предназначен для формирования последовательностей тактовых импульсов, которые обеспечи вают синхронизацию работы всех элементов устройства. Генератор 92 тактовых импульсов формирует исходные последовательности импульсов (фиг.2) Он включается в работу непосредствен но после подачи питания. Импульсы с второго выхода генератора 92 поступают на два паралле,льно работающих распределителя импульсов 90 и 91. Каятый из распределителей 90 и 91 формирует три последовательности так товых импульсов в соответствии с вре гвенной диаграммой фиг.6. Тактовые . импульсы, формируемые на первом выходе генератора 92 импульсов, поступают на выход 59.1 блока 1 синхрониз ции. Тактовые импульсы, формируемые на первых и вторых одноименных выходах д елителей 90 и 91, поступают раз дельно на выходы 59,2, 59,4, 59,3 н 59,5 ($лока 1 синхронизации. а выходы 59,6 и 59,8 блока 1 синхронизации поступают тактовые импульсы с выходов элементов И 95 и 9. Это обеспечивает формирование тактовых импульсов только при наличии одноименных тестовых импульсов одновременно соответственно на первых и четвертых выходах распределителей 90 и 91. Генератор 93 единицы формирует постоянный единичный сигнал, который поступает на выход 59,7 блока синхронизации.. Блок 2 задания режимов (г.З) предназначен для формирования управляющих воздействий на схему устройства, для задания ода числа циклов формирования управлякпщх воздействий и индикации состояния устройства. Элементы ицдикации 97-100 индицируют в исходное состояние устройство, сбой в работе устройства, конец выполнения программа формирования управляющих и тестовых воздействий соответственно. Кнопочные выключатели 101-104 формируют сигналы сброса, останова, приведения в ис ходное состояние и пуска схемы устройства соответственно. Включение кнопочного выключателя 105 формирует сигнал, переводящий устройство из автоматического режима в ру:чной. Кнопочные выключатели 106 и 107 формируют сигналы блокировки работы первого 4 и второго 5 блоков заданияинтервалов и первого 9 и второго 10 регистров при контроле функционирования устройства. Кнопочный выключатель 108 предназначен для формирования сигнала, задающего синхронный режим пуска устройства по тактовому импульсу с выхода 59.6 блока синхрони- . зацин. Кнопочные выключатели 109.1109.Е позволяют задавать двоичный код числа циклов формирования: управляющих и тестовых воздействий. Таймер 3 (фиг.4) обеспечивает формирование управляющего сигнала на коммутатор 11, разрешающего выдачу заданного управляющего или тестового воздействия строго определенной длительности на одном или нескольких выходах группы выходов 58 устройства. Принцип действия и назначение элемеитов таймера 3 состоит в следующем. В счетчик 115 через блок элементов И 111 записывается код длительности управляющих сигналов, который 51 поступает на входы блока 3с выходов 73.1-73.171 блока 6 памяти. Разрешение на запись дает сигнал с выхода элемента И 34, поступающий на вход 62 блока 3. Пока счетчик 115 находится в нулевом состоянии, на его инверсном выходе присутствует единйчньй сигнал, которьй открывает элемент И 113, и тактовые имлульсы с выхода 84 элемента И 30 проходят через элементы И 113 и ИЛИ 114 на нулевой вход триггера 110 и устанавливают его в исходное состояние. После записи в счетчик 115 кода длительности управляющих сигналов на его выходе пропадаёт единичный сигнал и на йулевой вход триггера 110 перестают поступат импульсы сброса. Блок 3 переходит в режим ожидания запуска. Включение блока 3 осуществляется импульсом, поступающим на вход 64 блока 3с выхода элемента И 35. По заднему фронту этого импульса, который посту пает на объединенные входы J и С триггера 110, последний устанавливается в единичное состояние и на выхо де 65 блока 3 появляется единичный сигнал, разрешающий выдачу через коммутатор 11 управляющих или тестовых сигналов на выход 58 устройства Одновременно триггер 110 нулевым сигналом со своего инверсного выхода открывает элемент И 112, через который на вход С счетчика 115 начинают поступать тактовые импульсы с вькода 84 элемента И 30. Поступающие тактовые импульсы вычитаются из числа, записанного в сче чике 115, и когда последний вернется в исходное состояние, на его выходе вновь появится единичный сигнал, которьй откроет элемент И 113 и очеред ной тактовый импульс с выхода 84 эле мента И 30 установит триггер 110 в исходное состояние. Триггер 110 снимает единичный сигнал с выхода 65 блока 3 и единичным сигналом на своем инверсном выходе закрывает элемент И 112, прекратив тем самым поступление импуль сов на вход С счетчика 115. Таким образом, на выходе 65 блока 3 будет сформирован сигнал, управлявлций вьзд чей информации на выход устройства длительность которого строго опреде ляется кодом длительности поступив шем с выходов 73.1-73.m блока 6 па мяти. Установка счетчика 115 в исход 4 ное состояние осуществляется сигналом сброса, поступающим на вход 63 блока 3 с вьрсода элемента ИЛИ 53. Триггер 110 первоначально устанавливается в исходное состояние сигналом сброса, снимаемым с инверсного выхода 80 второго триггера 16 пуска. Функциональная схема устройства для управления и контроля содержит два идентичных блока 4 и.5 задания интервалов. Рассмотрим назначение элементов каждого блока. Счетчик 8 предназначен для отсчета временного интервала, соответствующего коду длительности интервала,считываемому с третьей группы выходов блока 6 памяти. Он представляет собой вычитающий счетчик, имеющий п входов (5 5) параллельной записи кода, счетный вход Си вход R сброса. На выходе счетчика появляется единичный сигнал только при установке его в исходное состояние. Запись кода в счетчик осуществляется с выходов блока элементов И 52, которые открываются разрешающим сигналом с выхода элемента И 34.Установка счетчика 8 в исходное состояние осуществляется сигналом с выхода элемента ИЛИ 55,который )ормируется в трех случаях при поступлении сигнала сброса с выхода 80 триггера 16 пуска, когда он находится в исходном состоянии, при поступлении сигнала блокировки с выхода 60.6 пульта 2 управления к индикации, которьй используется для проверки устройства, при поступлении сигнала с выхода элемента И 44, которьй формируется при окончании формируемого интервала. Первьй триггер 20 управления разрешает поступление тактовых импульсов с выхода 83 элемента И 31 .на счетный выход счетчика 8, На его вход Э подается сигнал логической единицы с .выхода 59,7 блока 1 синхронизации, а вход К подключен к нулевому полюсу источника питания. Когда триггер 20 находится в исходном состоянии, элемент И 40 открыт единичным сигналом с инверсного выхода триггера 20. Че- рез элемент И 40 проходит первый тактовьй импульс с выхода 83 элемента И 41 и по его заднему фронту триггер 20 переключателя в единичное состояние. . Нулевым сигналом с инверсного выхода он запрещает прохождение последуищих тактовых импульсов через элемент И 40, а единичным сигналом прямого выхода открывает элемент И 4 через который второй и последующие тактовые импульсы с выхода элемента И 41 поступают на счетный вход счетчика 8, а также на вход элемента И 42. Триггер 20 устанавливается в исходное состояние либо сигналом сброса с выхода 80 триггера 16 пуска, либо сигналом бпокировки, подаваемым с выхода 60.6 пульта 2 управ ления и индикации. Входы R триггера 20объединены по ИЛИ, т.е. могут Н1Бзависимо переводить триггер в исходное состояние. Второй триггер 21 управления предназначен для формирования импул сов сброса в исходное состояние счетчиков 8 и 115, а также импульсо управляющих записью кодов в счетчики 8 и 115. На J- и К-входы триггера подается,сигнал с выхода элемен- та ИЛИ 56. Вход К является инверсны Если на выходе элемента ИЛИ 56 появляется единичный сигнал, то триггер 21переключается в единицу по заднему фронту очередного тактового импульса с вьиода 39.2 блока 1 синхронизации. Единичным сигналом триггер 1 открывает элементы И 43, 44. В результате этого на выходе элемента И 44 появляется импульс, соответствующий пауэе между тактовыми импульсами с выхода 59.2 блока 1, кото рые поступают на его инверсньй вход Этот импульс проходит черер элемент ИЛИ 55 на сброс.счетчика 8 и далее через элемент ИЛИ 53 на сброс счетчика 115. Очередной тактовый импульс с выхода 59,2 блока 1 прохо, дит на выход элемента И 43, открывает блоки элементов И 52 и 111 и тем самым разрешает запись кодов длитель ности интервала и дл1;тельности управ ляющих сигналов в счетчики 8 и 115 соответственно. Так как на выходе элемента ИЛИ 56 появляется нулевой сигнал, то этот же тактовый импульс своим задним фронтом возвращает триг гер 21 в исходное состояние. В ре зультате элементы И 43, 44 закрыва ются и последующие тактовые импульсы с выхода 59.2 блока 1 на их выходы не проходят Триггер 21 устанавливается в исходное состояние теми же сигналами, что и триггер 20. Элемент И 42 разрешает прохождени на элемент ЮШ 56 (N-t-l)-ro тактового импульса, поступающего с выхода элемента И 41 одновременно на счетный вход счетчика 8 и элемент И 42. Число М определяется кодом длительности интервала, записанным предварительно в счетчик 8. Таким образом,N -и импульс возвращает счетчик 8 в исходное состояние. Последний сигналом с инверсного выхода открьшает элемент И 42 и (М+1)-й тактовый импульс проходит на элемент ИЛИ 56. Элемент ИЛИ 56 формирует импульсы, соответствующие началу и концу интервала, определенного кодом длительности импульса, записанным в счетчик 8. Импульс начала интервала проходит через элемент ИЛИ 56 с выхода элемента И 40, импульс конца интервала - с выхода элемента И 42. Элемент ИЛИ 56 формирует импульс конца интервала также при поступлении на его вход импульса с выхода элемента И 33, что позволяет сократить интервал против заданного при поступ лении соответствующего сигнала с объекта контроля на вход 57 устройства. . Назначение и принцип действия элементов блока 5 задания интервалов аналогичны описанным. Блок 6 памяти предназначен для хранения кодов длительности интервалов, кодов длительности управляющих и тестовых возде1Чствий, а также кодов . управляющих сигналов. Указанные коды хранятся в блоке 6 памяти по различным адресам и вьщаются одновременно параллельными п , m и -разрядными кодами соответственно при поступлении на один из 5 -входов единичного сигнала с выхода одного из элементов И блока элементов И 22. Выходные сигналы блока 6 памяти присутствуют в течение всего интервала времени наличия сигнала на входе блока 6. Один разряд блока 6 памяти выделен для хранения сигналов метки, отмечающей последний код управляющих воздейстйий в формируемой последовательности (цикле).. При считьгоании из блока 6 памяти последнего кода на выходе 75 блока появляется единичный сигкал метки. Счетчик 7 циклов предназначен для определения заданного числа циклов реалнэавд1и управляющих и тестовых воздействий. . Он представляет собой вычитакпр{й счетчик, имекщий t входов параллельной записи кода числа циклов, счетный вход и один инверсньй выход, единичный сигнал на котором появляет ся только при установке счетчика 7 в исходное состояние. Запись кода числа циклов осуществляется в счетчик 7 с выходов 61.1 - 61.t блока 2 парафазных кодов, который формируется блоками элементов И 23 и 24. Разрешение на запись кода в счетчик форми руется элементами ИЛИ 47 при поступлении на входы сигналов установки в исходное состояние с выхода 60.1 и сброса с выхода 60. 3 пульта 2 управ ления и индикации. Отсчет числа циклов производится счетчиком Ъ по импульсам конца цикла, поступающим на его счетный вход с выхода 89 эле мента И 39. При отработке устройством заданного числа циклов счетчик циклов устанавливается в исходное состояние и на его выходе 77 появляются единичный сигнал конца программы . Регистры 9 и 10 предназначены дл задания номера интервала и формиров ния сигнала считывания кодов из бло ка 6 памяти. Оба регистра идентичны а их одноименные выходные сигналы поступают на элементы И блока элементов И 22. Это повышает достоверность функционирования устройства, так как сигнал считывания из блока памяти формируется только при одновременной выдаче единичных сигналов на одноименных выходах регистров 9 10. Переключение регистров осуществляется по задним фронтам импульсов конца интервала, формирующих соответственно с блоках 4 и 5 задания интервалов на выходах 68 элементов ИЛИ 56. Элемент ИЛИ 45 формирует сигнал сброса регистра 9, если на его входы поступают либо сигнал сброса с вькода элемента ИЛИ 54, либо сигнал блокировки с выхода 60.6 блока 2 управления и индикации. Аналогично элемент ИЛИ 46 формирует сигнал сбр са регистра 10, если на его вхЬды поступают либо сигнал сброса с выхода элемента ИЛИ 54, либо сигнал блокировки с выхода 60.7 пульта 2 управления и индикации. Коммутатор 11 предназначен для формирования управляющих и тестовых воздействий на одном или нескольких выходах 58 устройства.

Коммутатор 11 содержит k элементов И, на объединенные первые входы которых поступает сигнйл с выхода 65 блока 3, разрешающий выдачу управляющих и тестовых воздействий на выход 58 устройства. Значения выходных сигналов коммутатора 11 определяется кодом, поступающим с выходов 74.1-74.К блока 6 памяти на вторые входы элементов И, а длительность выходных сигналов определяется длительностью сигнала с выхода 65 блока 3. Блок 12 сравнения (фиг,5) предназначен для сравнения времени реакции объекта управления и контроля с заданными интервалами, коммутации сигнала реакции объекта на входы триггеров 14 и 15 ответа, проверки совпадения одноименных выходных сигналов, вьщаваемых блоками 4 и 5 задания интервалов и регистрами 9 и 10. Блок 12 сравнения формирует на своем выходе.88, сигнал, соответствующий сбою в работе устройства, либо о несоответствии времени реакции объекта заданному временному интервалу. Для этого на входы схемы 118 сравнения блока 12 подаются одноименные сигналы с ЙЫХОДОВ1 66, 67 и 68 блока 4 и 69, 70 и 71 блока 5, а также выходов 78.1 - 78.S регистра 9 и 79.1 - 79.S регистра 10. При несовпадении значений сигналов хотя бы на одной паре одноименных выходов схема 118 сравнения формирует единичный сигнал, которьй через элемент ИЖ 120 подается на выход 88 блока 12 сравнения. Блок элементов И 119 предназначен для формирования сигналов, соответствующих номеру реализуемого интервала, если одноименные сигналы одновременно вьвдаются регистрами 9 и 10. Первый коммутатор 116 предназначен для выделения реакции объекта, поступающей на вход 57 устройства и соответствующей номеру реализуемого интервала. При совпадении единичшлх сигналов, поступающих на вход 57 устройства и с выхода блока элементов И 119, первый коммутатор П6 пропускает данньй сигнал реакции объекта на выход 89 блока 12 сравнения. Второй кo мyтaтop 117 предназначен для контроля времени реакции объекта зaдaннo fy временному интервалу. С этой целью на его первые входы Поступают сигналы реакции объекта контроля,, а на его вторые входы сигналы с выходов блока элементов И 119. Благодаря этому сигнал реакции объекту, поступивший в течение заданного интервала, не пройдет на выход коммутатора 117. При любом выпаденик сигнала реакции из заданного временного интервала соответствующий инверсный вход KOh iyTaTopa 117 будет открытый нулевым сигналом с выхода одного из элементов И блока элементов И 119, и сигнал реакции пройдет через коммутатор 117 и элемент И 120 на выход 83 блока 12 сравнения, свидетельствуя о норме времени реакции объекта заданным временным параметрам. I Триггер 17 контроля фиксирует факт ошибки (сбоя) в работе устройст ва и выдает единичный сигнал, который приводит в исходное состояние триггера 13 и 16 пуска, останавливая устройство, и поступает в пульт 2 для индикации сбоя в работе устройст ва,Триггер 17 устанавливается в еди ничное состояние очередным тактовым импульсом с выхода 59.1 блока 1 синх ронизации после поступления единично го сигнала на вход D . Возврат триггера 17 в исходное состояние осуществляется либо сигналом сброса, либо сигналом установки в исходное состояние с выходов 60.3 и 60.1 пуль та 2 управления и индикации, которые поступают на входы R триггера 17 через элемент ИЛИ А7. Первый триггер 13 пуска предназна чен для синхронного запуска устройст ва. Переключение триггера 13 в единичное состояние осуществляется тактовыми импульсами с выхода 59.3 блока 1 синхронизации, которые посту пают на вход С триггера. Для синхрон ного запуска устройства с выходов 60.4 и 60.8 пульта 2 управления и индикации формируются единичные сигналы пуска устройства и синхронного режима пуска соответственно, которые подаются на входы элемента И 26.. Последний формирует единичный сигнал на вход Э триггера 13. После поступления этого сигнала очередной тактовый импульс с выхода 59.3 блока 1 синхронизации устанавливает триггер 13 в единичное состояние. Тригге 13 единичным сигналом со своего выхода открывает элемент И 27, через которьш проходят тактовые импульсы с выхода 59.6 блока 1 синхронизации. Одновременно сигнал с выхода триггера 13 проходит через элемент ИЛИ 50 на вход J второго триггера 16 пуска, подготавливая его к включению. Триггер 16 пуска осуществляет пуск устройства, а после поступления на вход 3 единичного сигнала триггер 16 переключается в единичное состояние очередным тактовьп- импульсом с выхода 59.6 блока 1 синхронизации, который проходит через открытые элементы И 27, 28 и элемент ИЛИ 49 на вход С триггера. Установившись в единичное состояние, триггер 16 нулевым сигналом с инверсного выхода закрьшает элементы И 28 и 32 и снимает сигнал сброса с блоков 4, 3 и 5 триггера 19 и регистров 9 и 10. Одновременно единичньш сигнал с прямого выхода триггера 16 открьшает элементы И 29 и 31, разрешая прохождение тактовых импульсов с выходов 59,5 и 59,3 блока 1 синхронизации соответственно на блоки 3, 4 и 5 устройства и тем самым осуществляя пуск устройства в работу. Сброс триггеров 13 и 16 пуска осуществляется сигналом с выхода элемента ИЛИ 51, который формирует сигнал, сброса при поступлении на его входы одного изследующих сигналов: сигнала сброса с выхода 60.1блока 2,сигнала останова с выхода 60.2блока 2, сигнала установки в исходное с выхода 60.3 блока 2,сигнала сбоя устройства с выхода 81 триггера 17 контроля или сигнала Конец программы с выхода 87 элемента И 36. Триггеры 14 и 15 ответа предназначены для формирования импульса конца интервала при поступлении сигнала с объекта управления и контроля на вход 57 устройства. Единичный сигнал с выхода объекта поступает на вход 57 устройства и далее через первьй коммутатор 119 блока 12 сравнения на входы Ли R триггера 14. В результате этого снимается сигнал сброса с триггера 14, и он подготавливается к переключению в единичное состояние. Переключение триггера 14 осуществляется очередным тактовым импульсом, поступающим на вход триггера 14 с выхода 59.8 блока 1 синхронизации. Триггер 14, переключивщись по заднему фронту тактового импульса, своими выходными сигналами ;готовит к переключению в единичное 13 состояние триггер О ответа. Однотриггер 15 временно единичный сигнал с прямого выхода триггера 1Д поступает на элемент И 33. В результате этого на выходе 86 элемента И 33 появляется единичный сигнал, который поступает в блоки 4 и 5 задания интервала. Следующий тактовый имггульс с выхо да 59.8 блока 1 синхронизации поступает на вход триггера 15 и по его заднему фронту он переключается в единичное состояние. Нулевым сигналом с инверсного выхода он закрыва ет элемент И 33. Таким образом, на выходе элемента И 33 формируется импульс конца интервала длительностью, равной периоду следования тактовых 1импульсов на выходе 59.8 блока 1 син ронизации. Триггеры 14 и 15 ответа возвращаются в исходное состояние по окончанию действия сигнг,ла на выходе 89 блока 12 сравнения. Триггер 18 конца программы предназначен для выделения импульсного сигнала конца программы формирования управляющих или тестовых, воздействий На вход 3 триггера подается посто янный единичный сигнал с выхода 59.7 блока 1 синхронизации, а вход К подключен к нулевому полюсу источника питания. Сигнал конца программы формируется на выходе 77 счетчика 7. Этот сигнал открывает элемент И 36, на выходе которого появляются сигнал конца программы в виде последователь ности импульсов с частотой тактовых импульсов с выхода 59.1 блока 1 синх ронизации. Этот сигнал поступает одновременно на элемент И 37 и вход С триггера 18. Первый из последователь ности импульсов проходит на выход элемента И 37 и далее на элемент ИЛИ 51 и триггер 13 в качестве импульсного сигнала конца программы Одновременно триггер 18 по заднему фронту сигнала устанавливается в единицу, запрещая прохождение последующих импульсов через элемент И Триггер 18 устанавливается в нулевое

состояние сигналами сброса с вьгхода 60.3 блока 2 и установки в исходное с выхода 60.1 блока 2. Триггер 10 блокируется в исходном состоянии при выдаче на выходе 60.5 блока 2 сигнала перевода устройства в ручной режим. Одновременно этот же сигнал закрывает элемент И 37,запре-11

элементы ИЛИ 54, 45 и 46, импульс конца цикла приведет в исходное состояние регистры 9 и 10.

Элемент И 25 предназначен для формирования сигнала, разрешающего асинхронный запуск устройства. На его выход проходит импульс запуска при отсутствии сигнала синхронного 414 щая формирование импульсного сигнала конца программы. Элементы ИЛИ 47 и 48 объединяют указанные сигналы и формируют сигнал, поступающий на вход R триггера 18. Триггер 19 конца цикла управляет формированием сигнала конца цикла. Входы J и k триггера 19 гцдключены к выходу элемента И 38 (вход К - инверсный). При считьшании из блока 6 памяти кодов для последнего интервала формирования управляющих и тестовых воздействий с выхода 75 одновременно считьшается единичный сигнал, который поступает на первый вход элемента И 38. Когда на второй его вход поступает сигнал с выхода 65 блока. 3, разрешающий выдачу последних в данном цикле управляющих или тестовых воздействий на выход устройства, на выходе элемента И 38 появляется единичный сигнал. Он поступает на выходе Э и К триггера 19, который очередным тактовым импульсомс выхода 59.1 блока 1 синхронизации переключается в единичное состояние. Единичный сигнал с выхода триггера 19 поступает на вход элемента И 39. Когда закончится выдача последних в цикле управляющих воздействий и сигнал на выходе 65 блока 3 станет равным нулю, откроется элемент И 39 и на его выход поступит очередной тактовый импульс с выхода 59.1 блока 1 синхронизации. Одновременно этот же импульс своим задним фронтом переключает в нулевое состояние триггер 19,.так как на его входе Л будет присутствовать нулевой сигнал, а на входе К - единичный. Своим выходным сигналом триггер 19 закроет элемент И 39 и запретит прохождение через него последующих тактовых импульсов с вькода 59.1 блока 1 синхронизации. Импульс конца цикла с выхода элемента И 39 поступит на счетный вход счетчика 7, в результате чего содержимое счетчика 7 уменьшится на единицу. Одновременно, пройдя через

15

запуска и при поступлении сигнала пуска с выхода 60..4 блока 2. Этот, импульс является конъюнкцией тактовых импульсов, поступающих одковременно на его входы с выходов 59.3 и 59.5 блока 1 синхронизации. Этот импульс проходит через элемент ИЛИ 49 и И 28 и переключает в единичное состояние триггер 16 пуска.

Элемент И 30 формирует тактовые импульсы, управлякщие работой блока

3только при наличии тактовых импульсов с выходов 59,3 и 59.5 на обоих его входах, что обеспечивает дополнительную запщту устройства от неправильного функционирования при сбоях.

Элемент И 32 формирует сигнал приведения устройства в исходное состояние. Этот сигнал появляется на выходе 85 элемента И 32, если в счетчик 7 циклов записан код числа циклов, которые необходимо реализовать, а триггер 16 пуска находится в нулевом состоянии. Этот сигнал поступает в блок 2 и используется для индикации исходного состояния устройства.

Элемент И 34 формирует импульсы управления записью кодов в счетчики 8 блоков 4, 5 и счетчик 7 блока 3. Элемент И 35 формирует импульс конца интервала, управляющий переключением триггера 110 блока 3. Элементы И 34 и 35 формируют указанные сигналы олько при одновременном формировании одноименных сигналов блоками 4 и 5 задания интервалов, что повьппает остоверность функционирования устройства .

Блок элементов И 52.1-52. разрешает прохождение кода длительности интервала с выходов блока 6 памяти на входы счетчиков 8 блоков

4и 5 задания интервалов.

Элементы И-52.1-52.п открываются сигналом с выхода элемента И 34.

Элемент ИЛИ 54 формирует сигнал сброса счетчика 115 блока 3, если хотя бы один из блоков 4 и 5 задания интервалов сформировал этот сигнал.

Устройство для управления контролем работает следующим образом.

После включения питания устройство приводится в исходное состояние. Для этого на блоке 2 с помощью кнопочных выключателей 109.1-109. наби-, рается код числа циклов формирования:

5607416

управляющих или тестовых воздействий которьй должны реализовать устройство. После этого с помощью в кнопочного выключателя 101 пульта 2 формируется сигнал сброса, по которому приводятся в исходное состояние все элементы памяти устройства, включая счетчики 90 и 91 блока 1 синхрониза ции, а в счетчик 7 циклов заносится

10 заданный код числа циклов. О приведении устройства в исходное состояние свидетельствует сигнал, на выходе 85 элемента И 32, который поступает на индикатор 97 блока 2.

15 Запуск устройства осуществляется в двух режимах: асинхронном и синхронном.

При асинхронном запуске на блоке 2 с помощью кнопочного выключателя

20 104 формируется команда Пуск, которая поступает на выход 60.4 блока 2 и далее на вход элемента И 25.

Тактовые импульсы с выходов 59.3 и 59,5блока 1 синхронизации поступают на входы элемента И 25. Очередной тактовый импульс пройдет на выход элемента И 25, а затем через элементы ШШ 49, и И 28 на вход С триггера 16 пуска и переключит его в единичное состояние. Последний снимет сигнал сброса с элементов схемы устройства, закроет элемент И 28 и от,кроет элементы И 29 и 31, через которые тактовые импульсы с .выходов

.- 59.3 и 59:5 поступят на блоки 3,4, и 5 устройства.

При синхронном запуске на блоке 2 с помощью кнопочного выключателя 108 задается режим синхронного запуска. Сигнал с выхода 60.8 блока 2 открьшает элемент Н 26 и закрыва ет элемент И 25. При поступлении сигнала Пуск с выхода 60.4 блока 2 на вход J триггера 13 поступает единичHbDi сигнал , и очередной тактовый имлульс с выхода 59.3 блока 1 переводит триггер 13 в единичное состояние. Он открьшает элемент И. 27, через которьй проходит очередной тактовый

импульс с выхода 59.6 блока 1, которым синхронизируется запуск. Пройдя через элементы 1ШН 49 и И 28, этот импульс включает триггер 16, запуская устройство в работу аналогично описанном .

Первьй тактовьш импульс с выхода 83 элемента И 31 проходит через элемент И 60 и своим задним фронтом переключает в единичное состояние триггер 20. Одновременно этот де тактовый импульс проходит через элемент ИЛИ 56 на входы Лик триггера 21 и на выход 68 блока 4. Во врем действия этого импульса очередной тактовый импульс с выхода 59.2 блока 1 своим задним фронтом переключает триггер 21 в единичное состояние. Триггер 21 открывает элементы И 43и 44. На выходе элемента И 44 появляется единичный сигнал, который, пройдя через элемент ИЛИ 55, сбрасывает счетчик 8 и одновременно поступает на вход схемы 118 сравнения. Импульс, поступивший на выход 68 блока 4, проходит па вход 6 регистра 9 и на входы схемы 118 сравнения. Своим задним фронтом он переключает регистр 9 в состояние, при котором на его выходе 78.1 появляется единич ный сигнал. При совпадении его с одноименньм сигналом . с выхода 79.1 регистра 10 на выходе элемента И 22. появляется единичный сигнал, по кото рому из блока 6 памяти считьгоаются коды, соответствукяцие первому интервалу формирования управляющих или тестовых воздействий. При совпадении импульса с выхода 68 блока 4 с одноименным импульсом с выхода 71 блока 5 на выходе элемента И 36 появится импульс, который поступит на объединенные J - и С-вхо ды триггера 110 блока 3 и задним фронтом переключит его в единичное состояние. Следунзщий тактовый импульс с выхо да 59.2 блока 1 проходит через элемент И 43 на выход 66 блока 4. При поступлении одноименного импульса с выхода 69 блока 5 элемент И 34 форми рует импульсi который открьпзает блок элементов И 52.1-52.п, через которые код длительности интервала проходит на входы 5„ счетчиков 8 блоков 4 и 5 и записываетсяв эти счетчики Одновременно импульс с выхода :элемен та И 34 открывает блок элементов И 1 1 блока 3 и код длительности управляющего или тестового воздействия с выходов 73.1-73.m блока 6 записывает ся в счетчик 115 блока 3. Кроме того, импульс с выхода 66 блока 4 поступает на вход схемы 118 сравнения. Тот же тактовый импульс с выхода 59.2.своим задним фронтом возвратит 1 418 триггер 21 в исходное состояние,так как к этому моменту сигнал на выходе элемента ИЛИ Е 56 будет равен нулю. Триггер 20, переключившись в единичное состояние, откроет элемент И 41, в результате чего второй и последующий тактовые импульсные выходы 83 элемента И 31 будут проходить через элемент И 41 на счетный вход счетчика 8 блока 4. Счетчик 8 начнет отсчет времени первого интервала формирования управляющих или тестовых воздействий. Одновременно с этим триггер 110 нулевым сигналом со своего инверсного выхода откроет элемент И 112 и счетчик 115 начнет отсчет длительности формируемого управляющего или тестового воздействия. Единичный сигнал с прямого выходя триггера 110 поступит на выход 65 блока 3 и далее на вход коммутатора 11, в результате на выход 58 устройства поступят управляющие или тестовые воздействия в соответствии с кодом, поступившем на коммутатор 11с выходов 74.1-74.к блока 6 памяти. По окончании заданной длительности управляющего воздействия счетчик 115 блока 3 вернется в исходное состояние, откроет элемент И 113, через который пройдет очередной тактовый импульс с выхода 84 элемента И 30. Этот импульс через элемент ИЛИ 114 пройдет на вход R триггера 110, который снимет единичный сигнал с выхода 65 блока 3. В результате коммутатор 11 прекратит выдачу управляющих или тестовых воздействий на выход 58 устройства. По окончании отсчета заданного времени первого интервала в исходное состояние вернется счетчик 8 блока 4, который откроет элемент И 42, и очередной тактовый импульс с выхода 83 элемента И 31 пройдет через элементы И 41, 42 и элемент ИЖ 56 на входы Г7 и К триггера 21 и выход 68 блока 4. В результате на выходах элементов И 43, 44, 35 и 34 аналогично описанному будут последовательно сформированы импульсы, которые последовательно приведут в исходное счетчики 8 и 115, переведут с в следующее состояние регистры 9 и 10, произведут запись кодов в счетчики 8 и 115 и переведут устройство в ре-, жим отработки следующего интервала формирования управляющих или тестовы воздействий. Блок 5 задания интервалов работае аналогично блоку 4, параллельно с ним формирует управлянлцие сигналь на выходах 69, 70 и 71. Для повьпиения достоверности функционирования устройства и значительного уменьшения вероятности выдачи ложных управляющи и тестовых воздействий сигналы с выходов 66. 69 и 68 71 подаются на элементы И 34 и 35 соответственно, которые В1адают единичные выходные сигналы только при совпадении единич ных сигналов на входах.Одновременно течение всего времени работы устройства одноименные выходные сигналы блоков 4, 5 и регистров 9 и 10 сравниваются схемой 118 блока 12 сравнения. Схема 118 сравнения выдает единич ный выходной сигнал при несовпадении значений хотя бы одной пары одноимен ных сигналов. При поступлении единичного сигнала на вход 3 триггера 17 последний переключается в единицу очередным тактовым импульсом с выхода 59.1 блока 1. Триггер 17 единичным выходным сигналом через элемент ИЛИ 51 сбрасьшает устройство в исходное сос тояние, а на блоке 2 засвечивает индикатор 98 сбоя. Возврат триггера 17 в исходное состояние осуществляется по сигналам Сброс или Исходное, подаваемым с блока 2. Важной особенностью работы устрой ства является возможность сокращения интервала формирова.ния управляющих или тестовых воздействий в соответст вии с реальньв4и характеристиками объекта контроля и управления, что с щественно повышает точность вьщачи по времени последуняцих сигналов на выход 58 устройства. С этой целью требуемый выход.объекта подключается к входу 57 устройства. Когда на входе 57 появляется единичный сигнал, он проходит через коммутатор 116 блока 12 сравнения на выход 89 и по тактовому импульсу с выхода 59.8 блока 1 срабатывает триггер А и на выходе 86 элемента И 33 появляется сигнал. По заднему фронту следующего тактового импульса с выхода 59.3 блока 1 срабатывает триггер 15 и закрывает элемент И 33. Сформированный таким образом импульс 1 74 20 поступает на элементы ИЛИ 56 в блоки 4 и 5, в результате чего они аналогично описанному формируют необходимые управляющие сигналы, которые принудительно переводят устройство в режим формирования следующего управляющего воздействия несмотря на то, что счетчики 8 еще не вернулись в исходное состояние. Триггеры 14 и 15 возврашаются в исходное состояние при снятии сигнала с выхода 89 блока 12 сравнения. Устройство реализует алгоритм контроля времени выполнения объектом заданных операций параллельно с основным алгоритмом выдачи тестовых и управляющих воздействий. С -этой целью реакции объекта, поступающие на вход 57 устройства, подаются на входа коммутатора 117 блока 12 сравнения . Если реакция объекта соответствует заданному интервалу, то соответствующий вход коммутатора 117 закроет единичный сигналом с выхода соответствукщего элемента И блока элементов И 119 и сигнал на выход коммутатора 117 не пройдет. Если же реакция объекта превышает заданный интервал, то по его истечении регистры 9 и 10 переключаться в следукяцее положение и сигнал, поступивший . с объекта, пройдет через коммутатор 117 и элемент ИЛИ 120 на выход 88 |блока 12 сравнения. Б результате по очередному тактовому импульсу с выхода 59.1 блока 1 синхронизации сработает триггер 17 контроля, устройство прекратит дальнейшее функционирование и зафиксирует факт неправильной реакции объекта контроля или управления. Устройство функционирует аналогично описанному в течение реализации всех N-1 () интервалов формирования управляю1дах и тестовых воздействий, где N г число интервалов формирования воздействий. При считывании из блока 6 памяти совокупности кодов, соответствукнцих последнему интервалу, на выходе 75 блока 6 считьшается единичный сигнал, отмечающий последний интервал. Этот сигнал поступает на первьй вход элемента И 38, на второй вход которого поступает сигнал с выхода 65 блока 3, который разрешает вьщачу через коммутатор 11 управляющих или тестовых сигналов, соответствующих послед- нему интервалу. На выходе элемента И 38 появляется единичный сигнал, в результате чего очередной тактовый импульс с выхода 59.1 блока 1 переключает, триггер 19 в единичное состояние. Когда заканчивается сигнал на выходе 65 блока 3, очередной тактовый импульс с выхода 59.1 блока 1 проходит через элемент И 39. Одновременно этот же тактовый импульс с выхода 59.1 блока 1 своим задним фронтом возвращает триггер 19 в исходное состояние, в результате чего последующие тактовые импульсы не могут пройти на вькод элемента И 39. Импульс с выхода элемента И 39 соответствует концу цикла формирования управляющих или тестовых воздействий Он поступает на счетный вход счетчика 7 циклов, уменьш 1Я его содержимое на единицу. Одновременно он проходит через элементы ИЖ 54, 45, 46 и устанавливает их в исходное состояни чем подготавливает реализацию следующего цикла работы. По окончании отсчета времени длительности последнего интервала счетчика 8 блока 4 и 5 возвращаются в исходное состояние, и устройство ав томатически переходит к отработке следукяцего цикла формирования управ лягадих и тестовых воздействий. После обработки последнего цикла по импульсу с выхода 89 элемента И 3 счетчик 7 циклов установится в исходное состояние. На его выходе 77 появится единичный сигнал, а на выходе элемента И 36 - последовательность импульсов. Сигнал с выхода 77 поступит на пульт 2 для индикации конца програм мы работы устройства. На выходе эле мента И 37 будет сформирован импуль ный сигнал, соответствующий концу работы устройства. Этот сигнал чере 422 элемент liJlH 51 установит в исходное состояние триггеры 13 и 16 пуска, прекратив тем самым работу устройства. Для приведения устройства в исходное состояние на блоке 2 с помощью кнопочных выключателей 109.1-109.t задается новое число циклов работы устройства, а с помощью кнопочного выключателя 103 формируется сигнал приведения устройства в исходное состояние. По этому сигналу все элементы памяти устройства приводятся в исходное состояние, а в счетчик 7 циклов записьшается код числа циклов На блоке 2 погасает индикатор 99 конца программы и загорается индикатор 97 исходного состояния программного устройства. Предлагаемое устройство обеспечивает высокую достоверность функционирования, практически исключающую возможность вьщачи ложных управляющих или тестовых сигналов, что обеспечивается наличием двух блоков 4 и 5 задания интервалов и двух регистров 9 и 10. Для проверки правильности функционирования элементов контроля с блока 2 задаются с помощью кнопочных выключателей 106 и 107 специальные сигналы блокировки блока 4 и регистра 9 или блока 5 и регистра 10. При формировании одного из этих сигналов работа соответствующих блока и регистра блокируется и после пуска устройства блок 12 сравнения и триггер 17 контроля должны зафиксировать сбой или отказ в схеме устройства, как это было описано. Наличие этого режима и обеспечивающих. его элементов и связей позволяют еще больше повьюить надежность и достоверность функционирования программного устройства.

GH

S2

90

91

т

95

Ш 53.5

4 9

Фиг.г

Фиг.З

l/yfi

tencDam. SZ

JS Г5Й«1

IIV

Г5ЯЛ ДЙ

«4Фиг 6

e

e t e

ч

i t

| Программное временное устройство | 1974 |

|

SU532860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758154, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для тестового контроля | 1974 |

|

SU516039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения неисправностей цифровых систем | 1973 |

|

SU561965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-11-05—Подача