(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для отображения дугОКРужНОСТЕй и эллипСОВ HA эКРАНЕэлЕКТРОННО-лучЕВОй ТРубКи | 1978 |

|

SU807264A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Знакоформирующее устройство | 1990 |

|

SU1728880A2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Преобразователь сдвига фазы в код | 1984 |

|

SU1193812A1 |

1

Изобретение относится к измерительной и вычислительной, технике и может быть использовано для деления повторяющихся, одинаковых по длительности временных интервалов на целое число равных частей.

Известен умножитель частоты, содержащий генератор опорной частоты, счетчики, регистр, схему задержки выходных импульсов, формирователь схемы контроля нулей и единиц остатка 1,

Его не достатком является низкая точность умножение частоты,

Наиболее ;близким по техническотй сущности к изобретению является устройство, содержащее генератор опорной частоты, блок синхронизации, суммирующий и вычитающий счетчики, регистр, сумматор и первый элемент ИЛИ, причем выход генератора опорной частоты соединен со счетным входом суммирукяцего счетчика, установочный вход которого:соединен с первым выходом блока синхронизации и первым входом первого элемента ИЛИ, выходы . разрядов суммирующего счетчика подключены ко входам регистра, управлякяций вход которого подключен ко второму выходу блока синхронизахдаи

и управляющему входу сумматора, т вход блока синхронизации является входом устройства, вцходы старших разрядов регистра соединены со входами вычитающего счетчика, установочный вход которого подключен к выходу первого элемента ИЛИ, а выходко второму входу первого элемента ИЛИ, и входу синхронизации суммаtO тора, входы которого соединены с выходами младших разрядов регистра 2,

(Недостаток данного устройства низкая точность умножения частоты.

Цель изобретения - повымение точности, . Поставленная цель достигается тем, Что в устройство, содержащее генератор опорной частоты, блок синхро20 низацни, суммирующий и вычитающий счетч1 и, регистр, сумматор и первый элемент ИЛИ, причем выход геиератора опорной у астоты соединен со счётньм входом суммирующего счетчика, установочный вход которого соединен с первым выходом.блока.синхронизации и первым входом первого элемента ИЛИ, выходы разрядов сумм1-фующего счетчика подключены ко входам

30 регистра, управляющий вход которого

подключен ко второму выходу блока сийхрЬнйзации и управляющему входу сумматора, вход блока синхронизации ;Я1вляется входом устройства, выходы старших разрядов регистра соединены ео входами вычитающего счетчика, установочный вход которого подключен к йыходу первого элемента ИЛИ, а выход - ко второму входу первого

лШента ИЛИ и BXO t:H«xp 5MHsSl :

сумма-гора, входы котЬрого сде ййёйы с выходами младших разрядов рбгистрйг дополнительно введены триггер, . ифференцирующий элемент, дешифратор, группа элементов И, ШЛёЙё йгей Задержки и второ:й элемент ИЛИ, причем ВЫХОДЫ csMMaTopa через дешифратор подключены к первым входам элеентов И группы, вторые входы элеентов которой, за исключениемперого, подключены к выходам сЬответтвующлх элементов задержки, соединенных в последовательную цепочку, ход первого элемента задержки которой соединен с выходом генератора опорной частоты и вторым входом первого элемента И группы, выходы элементов И группы подключены ко входам второго элемента ИЛИ, выход которого соединен со счетным входом вычитающего счетчика и первым входом триггера, второй вход которого подключен к выходу вычитающего счетчика, а выход триггера через дифференцирующий элемент соединен с выходом устройства.

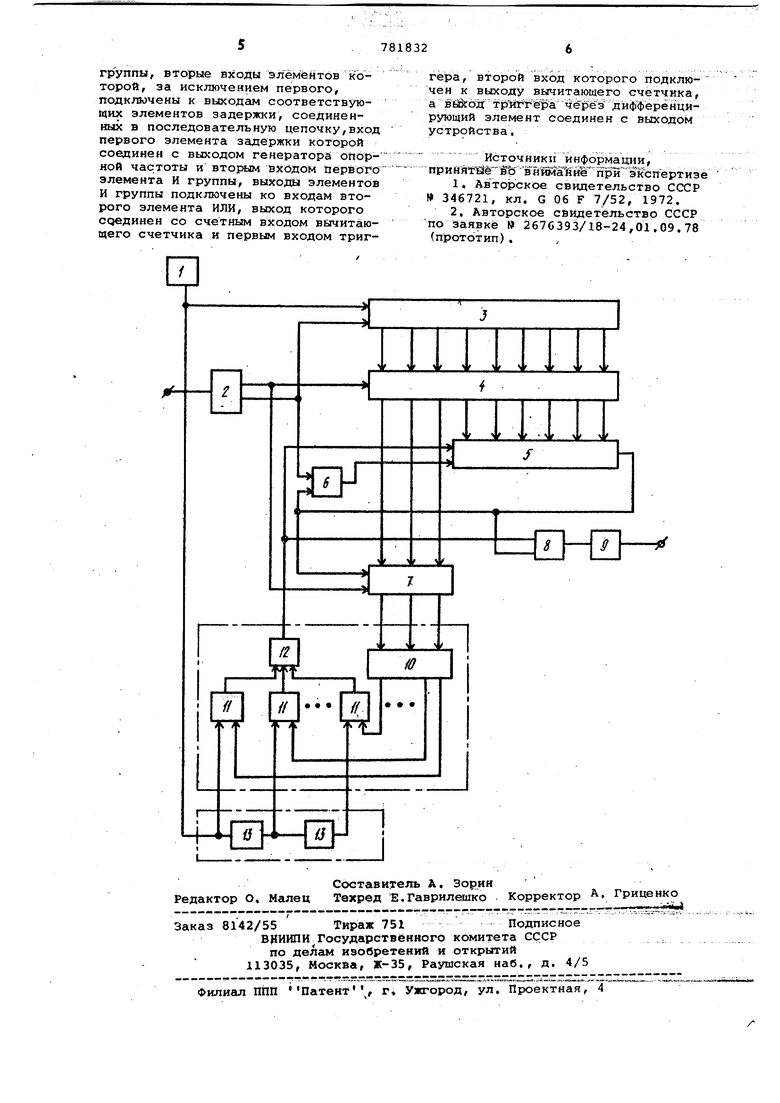

На чертеже представлена блок-схе ма устройства.

Умножитель частоты содержит генег ратор 1 опорной частоты, блок 2 синхронизации, сумми руквдий счетчик 3, регистр 4, вычитак«ций счетчик 5, элемент б ИЛИ, сумматор 7, RS-триггер 8, дифференцирующий элемент 9, дешифратрр 10, группу элементов II И, элемент 12 ИЛИ, элементы 13 задержки.

Устройство работает следующим образом,

На вход блока 2 синхронизации поступает входной сигнал х, имекдащй период Т)(, При переходе через опре деленный уровень на выходах блока 2 формируются короткие импульсы, которые используются для ввода кода из счетчика 3 в регистр 4 и для установки счетчика 3 в нулевое состояние,- , - . , -, .-,.. .. . . ., .,.:, |, ,,,. .. .

За период Т входного сигнала Uj, в счетчик 3 поступает N импульсов с выхода генератора 1, период кото- у рых равен TQ, .

В начале следующего периода Ujj блок 2 вырабатывает импульсы на выходах, первьЛ из которых перезаписывает код из счетчика 3 в регистр 4 и устанавливает в ноль сумматор 7 : сфоГуШ1а лив llel; в-::йб)1Г-;ечет--;;чик 3, через элемент б ИЛИ поступает

на вход счетчика 5 и заносит в него код старших разрядов регистра 4,

После того как на вход счетчика 5 поступает количество импульсов, равное коду стариих разрядов регистра, код в счетчике5 равняется нулю и на его выходе вырабатывается сигнал переполнения, Этот сигнал через элемент б ИЛИ поступает на вход счетчика 5 и опять заносит в него код N старших разрядов из регистра 4, одновременно этот сигнал устанавливает в Ч триггер 8 и поступает на вход сумматора 7, при этом ЬзЖмйруются содержимое сумматора 7 и младших разрядов регистра 4,

После выполнения суммирования код сумматора изменяется, изменяется состояние выходов дешифратора ДО управляющего элементами 11 И, на информационные входы которых посту;пают задержанные на элементах 13 импульсы, одноёременно изменяется и импульсная последовательность на входе счетчика 5, Первый импульс с выхода элемента 12 ИЛИ устанавливает в О триггер 8, и переход напряжения на его выходе выделяется дифференцирующим элементом 9 и поступае на выходную шину

В дальнейшем цикл работы устройства повторяется.

Формула изобретения

с Умножитель частоты, содержащий генератор опорной частоты, блок синхронизации, еу ммирующий и вычитающий счетчики, регистр, сумматор и первый элемент ИЛИ, причем выход генератора опорной чаЕС#о ы соединен со счетным входом суммирующего счетчика, установочный вход которого соединен с первым выходом блока синхронизации и первым входом первого элемента ИЛИ, выходы разрядов суммирующего

5 счетчика подключены ко входам регистра, управляющей вход которого подключен ко второму выходу блОка синхронизации и управляющему входу сумматора, вход блока синхронизации является ВХОДСИИ1 устройства, выходы старших разрядов регистра соединены со входами вычитающего счетчика, установочный вход которого подключен к выходу первого элемента ИЛИ, а выход - ко второму входу первого элемента ИЛИ и входу синхронизации сумматора, входы которого соединены с выходами младших разрядов регистра, отличающийся тем, что, с целью повышения точности, он содержат триггер, дифференцирующий элемент, дешифратор, группу элементов И, элементы задержки и второй элемент ИЛИ, причем выходы сумматора через дешифратор подключены к первьм входам элементов И

Авторы

Даты

1980-11-23—Публикация

1978-12-11—Подача