1

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих запоминающих устройствах.

Известно устройство для адресно-разрядной выборки системы 2,5 Д, содержащее в каждом разряде ключи втекающего и вытекающего записывающего и считывающего токов, согласующий блок, ключи, управляющие записывающим и считывающим токами, диодный дешифратор адресных линий разряда, дешифратор адреса и другие элементы {1|. Включение двух дополнительных диодов значительно уменьшает напряжение на индуктивности нагрузки в момент формирования фронта импульса тока, что снижает быстродействие устройства. Наличие гальванической межкаскадной связи позволяет организовать схему выборки только с диодным дещифратором, в котором на каждую адресно-разрядную шину необходимо устанавливать четыре диода, что громоздко ri неэффективно при большом количестве разрядов запоминающего устройства.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для выборки информации из блоков памяти типа 2,5 Д, содержащее первый дещифратор, входы которого подключены к шине сигналов управления, а одни выходы к соответствующим входам управляемых генераторов тока, выходы которых через элементы связи соединены с шиной питания и входами ключей, выходы которых соединены попарно и через адресно-разрядные шины подключены к выходам второго дешифратора, входы которого соединены с выходами соответствующих ключей групп, входы ключей группы соединены с другими выходами первого дешифратора 2.

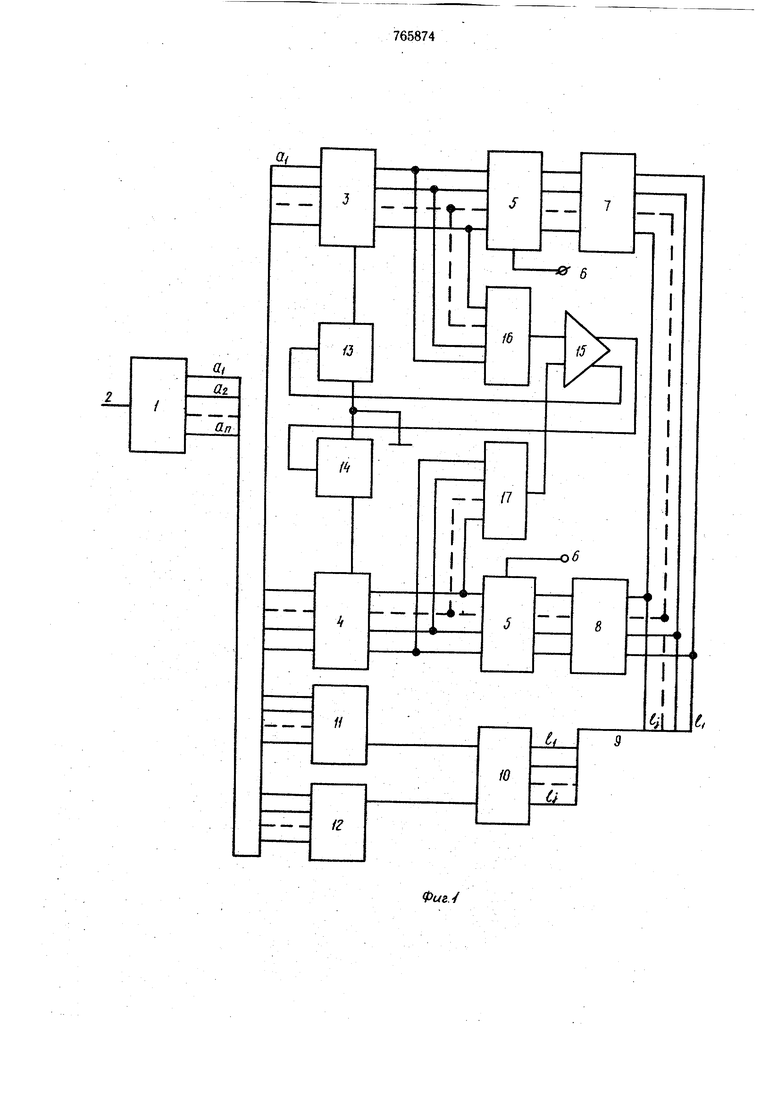

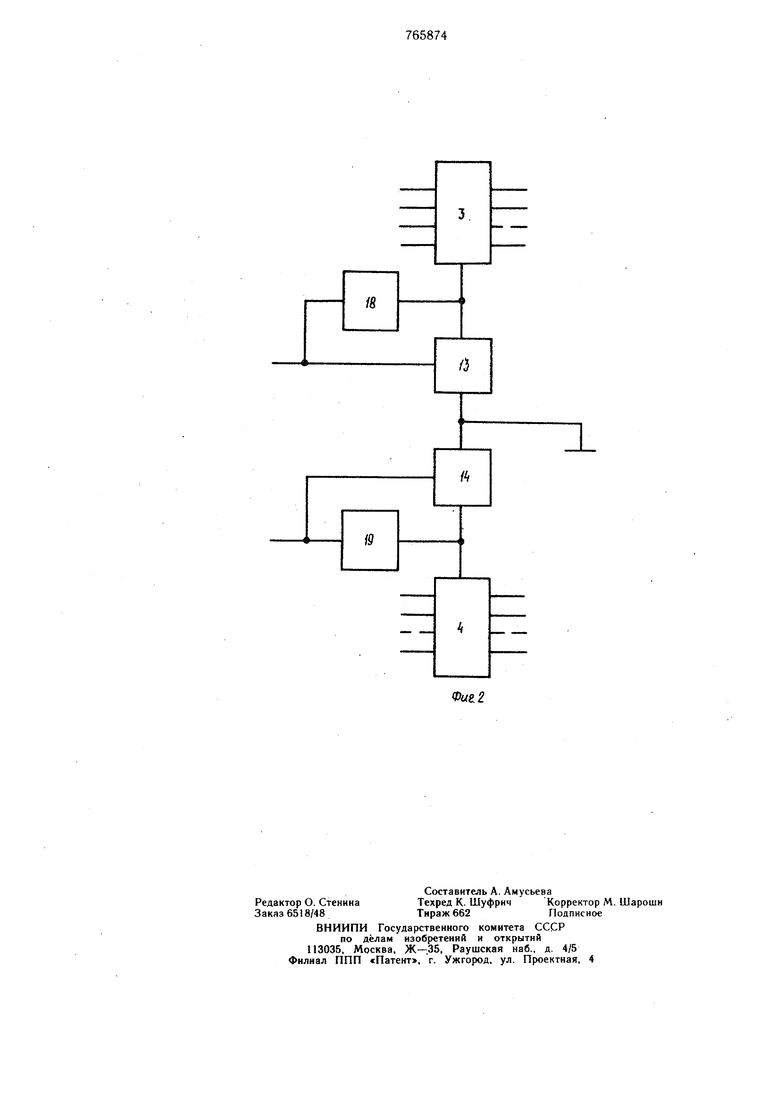

Однако для повышения быстродействия устройства необходимо уменьшить время между запускающими импульсами ключей положительного и отрицательного напряже НИИ. Обычно эти ключи работают в режиме насыщения, поэтому необходимо учи,тывать время рассасывания носителей заряда базы выходных транзисторов ключей. Без учета этого условия, т. е. при подаче запускающего импульса, например, на ключ отрицательного напряжения, когда еще открыт ключ положительного напряжения (в момент, когда его запускающий импульс окончен, и происходит рассасывание заряда базы), через ключи протекает ток большой амплитуды (режим короткого замыкания), что приводит к выходу- из строя ключей. Такое явление наблюдается при изменении температурного режима работы устройства, изменении питающих напряжений, изменении временной диаграммы работы устройства при профилактических и отладочных работах, что требует от разработчика устройства значительного запаса по времени между импульсами запуска ключей положительного и отрицательного напряжений, в результате чего снижается быстродействие устройства, Для повышения надежности в устройстве используется зависимая блокировка вы)одов первого дешифратора, однако такое решение неэффективно, так как не учитывает время восстановлеиия ютючей, т. е. время рассасывания носителей заряда базы выходных транзисторов ключей. Недостаточная надежность схемы выборки информации предъявляет жесткие требования к формирователям сигналов управления, поступающим на вход устройства, так как неисправности в устройстве управления запоминаюихего устройства приводят к массовому выходу ключей напряжения, что часто наблюдается в процессе иастройки. Все эта создает определенные трудности в условиях серийного производства, а также снижает надежность работы запоминающего устройства. Цель изобретения - повышение быстродействия и надежности устройства. Это достигается тем, что в устройство введены два дополнительных ключа, схема сравнения и два элемента ИЛИ, причем выходы управляемых генераторов тока соединены соответственно через дополнительные ключи с шиной нулевого потенциала, входы дополнительных ключей соединены с выходами схемы сравнения, входы которой, через элементы ИЛИ соединены с выходами соответствующих управляемых генераторов тока. При этом напряжение с перехода базаэмиттер выходных транзисторов ключей через элементы связи и элементы ИЛИ поступают на схему сравнения, что позволяет учесть время рассасывания заряда базы выходных транзисторов. С целью исключения влияния емкости управляемых генераторов тока, для ее формированного заряда в устройство введены два эмиттерных повторителя, входы и выходы которых соединены соответственно с входами и выходами дополнительных ключей. На фиг. приведена структурная схема устройства для выборки информации из блоков памяти типа 2,5 Д; на фиг. 2 - подключение двух эмиттерных повторителей. Устройство содержит первый дешифратор 1, входы которого подключены к шине 2 сигналов управления, а одни выходы - к соответствующим входам управляемых генераторов тока 3 и 4, выходы которых через элементы связи 5 соединены с шиной питаикя 6 и входами ключей 7 и 8, выходы которых соединены попарно и через адресноразрядные шины 9 подключены к выходам второго дешифратора 10, входы которого соединены с выходами соответствующих ключей групп 11 и 12, входы которых соединены с другими выходами первого дешифратора 1, два дополнительных ключа 13 и 14, схему сравнения 15, идва элемента ИЛИ 16 и 17. Выходы управляемых генераторов тока 3 и 4 соединены соответственно через дополнительные ключи 13 и 14 с шиной нулевого потенциала, входы дополнительных ключей 13 и 14 соединены с выходами схемы сравнения 15, входы которой через элементы ИЛИ соединены с выходами соответствующих управляемых генераторов тока 3 и 4. Ключевые элементы 13 и 14 и эмиттерные повторители 18 и 19 выполнены каждый на одном транзисторе. Наиболее часто в схемах выборки информации из блоков памяти запоминающих устройств в качестве элементов связи используются импульсные трансформаторы. Рассмотрим работу устройства для выборки информации из блоков памяти типа 2,5 Д с применением ключей напряжений с трансформаторной связью. Устройство работает следующим образом. В исходном состоянии с выходов первого дешифратора 1 на входы управляемых генераторов тока 3 и 4 поступают сигналы нулевого потенциала и напряжение на нагрузке генераторов тока - первичной обмотке трансформатора 5 - равно нулю. Ключи 7 и 8 закрыты. На входы элементов ИЛИ 6 и 17 подается сигнал высокого уровня, равный напряжению источника питания, поэтому на выходе элементов ИЛИ также поддерживается сигнал высокого уровня, вследс«:вие чего дифференциальный каскад схемы сравнения 15 закрыт и дополнительные ключи 13 и 14 открыты, разрешая тем самым работу управляемых генераторов тока 3 и 4. При подаче на вход генератора тока 4 высокого (едини.чного) уровня напряжения он открывается. По первичной обмотке трансформатора 5 протекает ток и, трансформируясь во вторичную обмотку, открывает ключ 8 (ключ отрицательного напряжения). Напряжение на первичной обмотке трансформатора пропорционально напряжению насыщения база-эмиттер выходного транзистора ключа, которое через элемент ИЛИ 17 прикладывается ко входу схемы сравнения 15, транзистор схемы сравнения открывается, и на вход дополнительного ключа 13 подйется сигнал высокого уровня. Дополнительный ключ 13 закрывается, и работа генераторов тока 3, а следовательно, и ключей 7 (ключи положительного напряжения)

запрещена. Напряжение на первичной обмотке трансформатора 5 поддерживается и в течение времени рассасывания заряда базы выходного транзистора ключей 8 (когда закрывается генератор тока 4, напряжение на первичную обмотку трансформируется со вторичной обмотки трансформатора). Таким образом, работа ключей 7 запрещена и на время рассасывания заряда базы выходного транзистора ключей 8. После окончания процесса рассасывания напряжение на первичной обмотке трансформатора 5 становится равным нулю, схема сравнения 15 закрывается и работа ключей 7 разрешается. При ключении ключей 7 работа ключей 8 запрещается аналогичным образом.

При работе устройства выборки в цикле чтения первым включается ключ 8, заряжая паразитную емкость разрядной шины 9, после этого открывается ключ 12 (ключ вытекающего тока), и по выбранной разрядной щине протекает полуток чтения. В конце цикла чтения первым выключается ключ 8, при этом емкость выбранной разрядной шины перезаряжается через открытый ключ 12.

В цикле записи первым включается ключ 7, затем - ключ 11 (ключ втекающего тока). Полуток записи протекает через ключ 7, выбранную разрядную шину и ключ П. В конце цикла записи первымвыключается ключ 1, а затем ключ 7, оставляя ранее выбранную шину под потенциалом, который обеспечивает запирание элементов второго дешифратора 10 ранее выбранной разрядной щины при возможном новом цикле чтения.

Таким образом, в устройстве исключается одновременная работа ключей 7 и 8 (ключей положительного и отрицательного напряжений) при перекрытии запускающих импульсов, поступающих с выходов первого дешифратора 1, что устраняет перегрузку выходных транзисторов ключей по току и повышает надежность работы устройства. Эффективность работы устройства значительно повышается, если используются ключи с трансформаторной межкаскадной связью, так как напряжение на первичной обмотке трансформатора опережает ток в ней и тем самым на дополнительные ключи управляющие сигналы подаются раньше, чем откроются ключи напряжения, работу которых необходимо запретить.

Предлагаемое устройство для выборки информации из блоков памяти типа 2,5 Д имеет повышенную по сравненню с прототипом надежность, увеличено его быстродействие за счет возможности сближения запускающих импульсов, так как происходит автоматическое слежение за -последовательностью работы ключей 7 и 8, что снижает жесткость требований к схемам, формирующим управляющие сигналы и исключает зависимые отказы.

Формула изобретения

1. Устройство для выборки информации из блоков памяти типа 2,5 Д, содержащее первый дешифратор, входы которого подклю чены к шине сигналов управления, а одни выходы - -к соответствующим входам управляемых генераторов тока, выходы которых через элементы связи соединены с шиной питания и входами ключей, выходы которых соединены попарно и через адресноразрядные щины подключены к выходам второго дешифратора, входы которого соединены с выходами соответствующих ключей групп, входы ключей групп соединены с другими выходами первого дешифратора, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит два дополнительных ключа, схему сравнения и два элемента ИЛИ, причем выходы управляемых генераторов тока соединены соответственно через дополнительные ключи с щиной нулевого потенциала, входы дополнительных ключей соединены с выходами схемы сравнения, входы которой через элементы ИЛИ соединены с выходами соответствующих управляемых генераторов тока.

2. Устройство по п. 1, отличающееся тем, что в него введены два эмиттерных повторителя, входы и выходы которых соединены соответственно с входами и выходами дополнительных ключей.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 531277, кл. Н 03 К 17/00,

2.Лехнов В. А. и др. Особенности оперативной памяти ЭВМ М-7000. В сб. Запоминающие устройства. Киев, 1975 с. 4-8, рис. 1, 3 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора информации из блоков памяти | 1982 |

|

SU1019491A1 |

| Блок адресной выборки для запоминающего устройства | 1980 |

|

SU982083A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Запоминающее устройство | 1979 |

|

SU809367A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Коммутатор | 1974 |

|

SU497730A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ СИГНАЛЬНОГО ЗАРЯДА С МАТРИЧНОГО ПЗИ-ФОТОПРИЕМНИКА | 2007 |

|

RU2341850C1 |

| МАГНИТНО-ТРАНЗИСТОРНЫЙ КЛЮЧ | 1991 |

|

RU2013860C1 |

| Устройство для индикации | 1982 |

|

SU1059604A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

Авторы

Даты

1980-09-23—Публикация

1978-01-18—Подача