Изобретение относится к вычислительной технике и может быть использовано при создании интегральных дин мич.еских оперативных запоминающих ус тройств (ОЗУ). Известны устройства для считьшани информации из динамических матричных накопителей, входящих в состав интегральных ОЗУ. Одно из таких устройств содержит в казвдом столбце матричного накопителя дифференциальный усилитель, выполненный на триггере статического типа, и дешифратор строк, дешифратор столбцов, блок ввода-вывода информации, блок управления, выходы которого подключены к управляющим; входам обоих дешифраторов и блоков Недостатком такого устройства является большая потребляемая мощность из-за протекания сквозного ток при считывании и записи через дифференциальные усилители. Наиболее близким техническим реше нием к предлагаемому является устрой ство для считывания информации из динамического матричного накопителя содержащее дифференциальные усилит ли с элементами предзаряда на транзисторах, входы усилителей, подключены к разрядным шинам, соединенные со стоками соответствующих запоминающих транзисторов, затворы которых соединены с соответствующими словарными шинами, а истоки - с одними выводами запоминающих конденсаторов, другие выводы кото1млх соединены с общей шиной хранения, подключенной к выходу генератора смещения напряжения хранения, а выход блока управления ОЗУ соединен с затворами транзисторов элементов предзаряда, истоки которых соединены с гаиной питания, а стоки совмещены со входами дифференциальных усилителей, выполненных динамическими на основе триггера, не потребляющего сквозного тока при счи,тывании и записи в устойчивом состоянии, разрядные шины череэ ключи выборки столбцов подключены к блОку вводавывода информации, ,. В интервале предварительного заряда на затворы транзисторов элементов предзаряда подается .высокий уровень напряжения, превосходящий напряжение источника питания, что обеспечивает высокое быстродействие устройства в интервале предзаряда и заряда разрядных шин до напряжения источника питания. Для получения высокого .

ровня напряжения предэаряда емкость утстрапногр каскада блока управлеия должна быть в несколько раз ольше емкости затворов всех транзиторов узлов преязаряда и занимает во только же раз большую площадь 2.

5

Однако уменьшение емкости бутстрап ого каскада блока управления дает кономию занимаемой площади, но одноременно снижает величину напряжения редэаряда, что приводит к ухудшению

ыстродействия устройства в интервале предварительного заряда. Невозможно одновременное уменьшение площади, занимаемой блоком предзаряда, и повышение быстродействия устройства.

Цель изобретения - увеличение 5 быстродействия устройства при одновременном уменьшении занимаемой площади на кристалле.

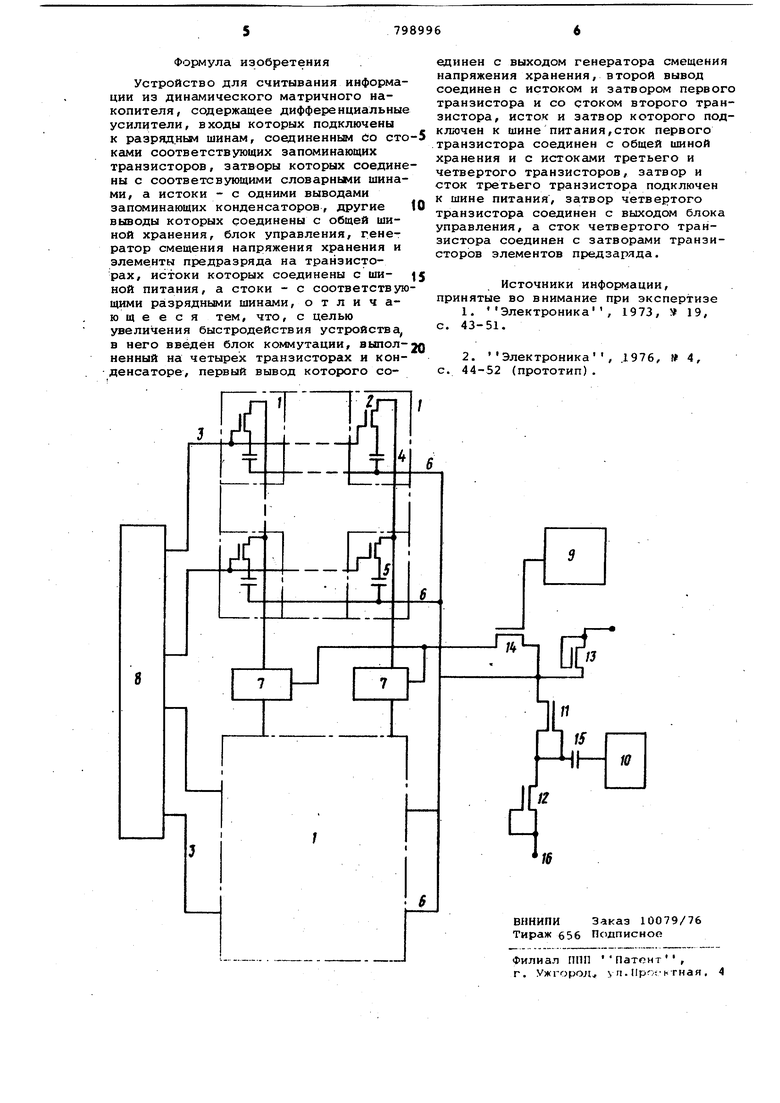

Поставленная цель достигается тем, что В устройство для считывания ин- 20 формации из динамического матричного накопителя введен блок коммутации, выполненный на четырех транзисторах и конденсаторе, первый вывод которого соединен с выходом генератора смеще- 25 ния напряжения хранения, второй вывод соединен с истоком и затвором первого транзистора и со стоком второго транзистора, исток и затвор которого подключены к шине питания,сток первого JQ транзистора соединен с общей шиной хранения и с истоками третьего и четвертого транзисторов, затвор и сток третьего транзистора подключен к шине питания, затвор четвертого ,г транзистора соединен с выходом блока управления, а сток четвертого транзистора соединен с затворами всех транзисторов элементов предзаряда.

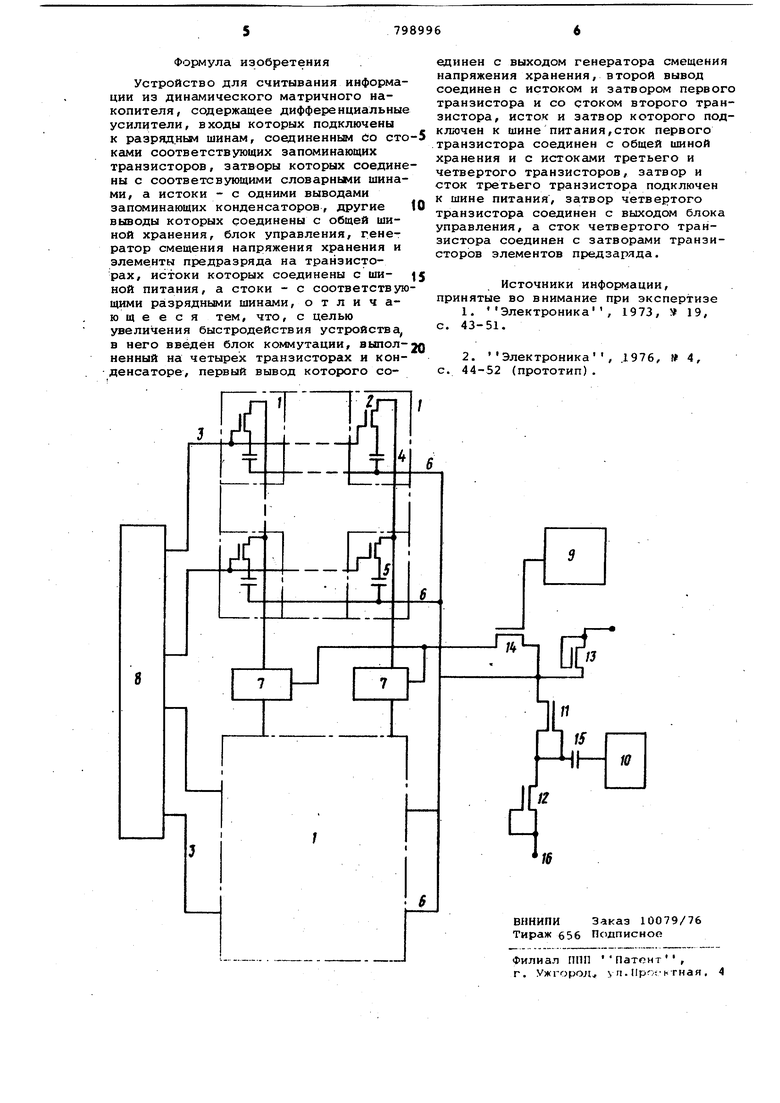

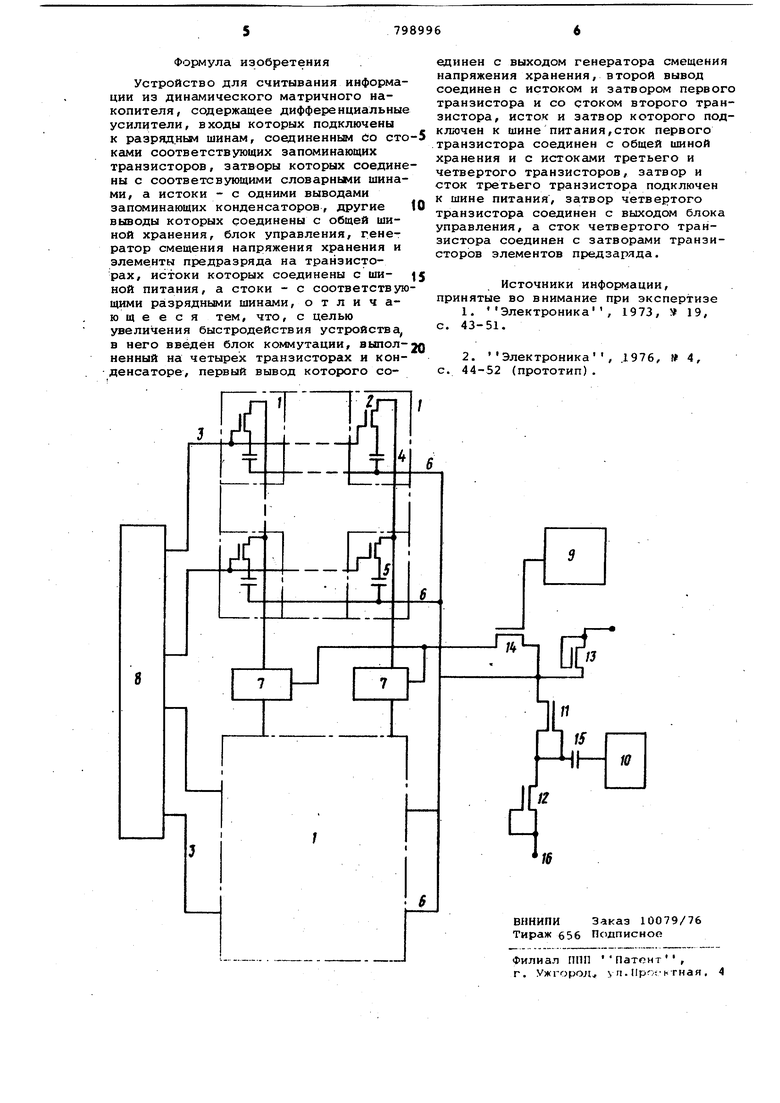

На чертежа изображена схема устройствами Оно содержит матричный накопитель 1, построенный на основе однот ран зисторных элементов памяти . Затворы запоминающих транзисторов 2 элементов памяти соединены по стро- j кам словарными шинами 3, стоки транзисторов 2 соединены по столбцам соответствующими разрядными шинами 4, а истоки транзисторов 2 соединены с запоминающими конденсаторами 5, на « которьЛс хранится информация. Шны хранения информации, которые одновременно являются вторыми электродами конденсаторов 5, соединены мензду собой и представляют общую емкостную шину хранения б. Посредине столбцов рас- 5 положены дифференциальные усилители 7, выполненные на триггерах, плечи которых сое.чнены с соответствующими половинами разрядных шин 4. Словарные шины 3 соединены с дешифратором 8 ДО строк, а разрядные шины 4 через ключи выборки столбцов, управляемые дешифратором столбцов, соединены с о.поком ввода-вывода информации. На чсртежр лешифоатор столбцоа, ключи 5

выбора столбцов и блок ввода-вывода не показаны. Устройство содержит также блок 9 управления, генератор 10 смещения напряжения хранения, блок коммутации, выполненный на четырех транзисторах 11-14 соответственно и конденсаторе 15, и шину 16

питания.

С целью экономии занимаемой площади и снижения потребляемой мощности целесообразно совместить генератор смещения напряжения хранения и генератор смещения подложки кристалла. При включении схемы емкость шины 6 хранения заряжается через транзистор 13 до напряжения питания минус пороговое напряжение транзистора 13. При оптимальном сигнале на выходе генератора 10 смещения через транзистор 12,конденсатор 15 заряжается до напряжения питания минус пороговое напряжение транзистора 12. При положительном сигнале на выходе генератора 10 смещения напряжения на конденсаторе 15 увеличивается и через транзистор 11, включенный диодом происходит дозаряд шины 6 хранения до напряжения большего напряжения питания.

В начале интервала предзаряда с выхода блока 9 управления на затвор транзистора 14 подается высокий уровень напряжения, превосходящий уровен напряжения источника питания. Транзистор 14 переходит в проводя1цее состояние, подключая затворы транзисторов элементов предзаряда к шине 6 хранения, на которой.накоплен высокий напряжения,чем обеспечивается перезаряд разрядных шин до 4 до напряжения источника питания. Когда разрйдные шины 4 заряжены, снимается напряжение с затвора ключевого транзистора 14. Устройство готовят к считыванию или записи информации. Работающий непрерывно генератор смещения 10 поддерживает на общей шине хранения высокий уровень напряжения, которое в следующем интервале предзаряда подают на затворы транзисторов элементов предзаряда, входящих в состав дифференциальных усилителей 7.

Матричный накопитель занимает 60% и более от всей площади запоминающего устройства, поэтому емкость общей шины 6 хранения во много раз больше суммарной емкости затворов транзисторов элементов предзаряда и соединяющей их шины,, и по отношению к зтим емкостям емкость шины 6 хранения в интервале предзаряда является идеальным источником напряжения.Этот факт позволяет увеличивать размеры транзисторов элементов предзаряда разрядных шин, не опасаясь потери уровня напряжения на их затворах, что являет ся одним из источников повышения быстродействия устройства в интервале предзаряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Устройство для выборки информации из матричного накопителя | 1982 |

|

SU1073796A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

Авторы

Даты

1981-01-23—Публикация

1978-12-28—Подача