1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для запоминания и хранеии данных в аналоговой форме в различны системах переработки информации.

Известны аналоговые запоминающие устройства (АЗУ), в которых выходное напряжение образуется путем интегрирования с последующим выпрямлением и сглаживаиием выходного сигнала импульсной формы, поступающего от ячейки аиалоговой памяти, выполненной на разветвленных магнитных сердечниках {I и 2.

Ввиду того, что иитегрирование выходиого сигнала ячейки аналоговой памяти в этих АЗУ осуществляется с помощью интегратора, работающего в режиме непрерывного интегрирования, появление случайной помехи во входиом сигнале интегратора ведет к возникновению переходного процесса в интеграторе, что вызывает значительную погрещность АЗУ в течение этого переходного процесса, длительность которого может составить более 300 периодов тока считывания.

Наиболее близким техническим решени ем к даниому изобретению является АЗУ

в котором интегрирование осуществляется двумя интеграторами, работающими в режиме периодического -сброса (3). Режим периодического сброса осуществляется здесь с помощью ключей, щунтирующих конденсаторы в цепях обратной связи усилителей интеграторов. Эти ключи работают синхронно с током считывания в протнвофазе, замыкаясь в течение одного полупериода тока считывания и размыкаясь в течение другого. Благодаря этому влияиие случайной

Ю помехи на величину выходного сигнала АЗУ может длиться не более полупериода тока считывания. Формирование выходного напряжения АЗУ осуществляется далее путем суммирования на резисторах выходных сигчало интеграторов, фильтрации с помощью

5 JjJ-фнльтра иижиих частот и усиления с по хощью масщтабнрующего усилителя .

Использование двух интеграторов н LCфильтра усложняет АЗУ. Кроме того нали2Q чие двух интеграторов вызывает необходимость подбора составляющих их элементов для выравнивания характеристик интеграторов, что также существеиио усложняет наладку и эксплуатацию.устройстга.

Целью изобретения является упрощение устройства и повышение его надежности.

Указанная цель достигается тем, что в известное АЗУ, содержащее ячей-ку памяти, один из входов которой является входом устройства, другие входы подключены к соответствующим выходам блока управления, интегратор, вход которого подключен к выходу ячейки памяти, ключ, вход которого подключен к выходу блока управления, выходы ключа подключены к установочным входам интегратора, введен блок слежения хранения информации, информационный вход которого подключен к выходу блока управления, а выход является выходом устройства.

Введение блока слежения-хранения позволило отказаться от использования IjC-фильтра,одного из интеграторов и масштабирующего усилителя, что существенно упрощает АЗУ и повыщает его надежность, упрощает наладку и эксплуатацию.

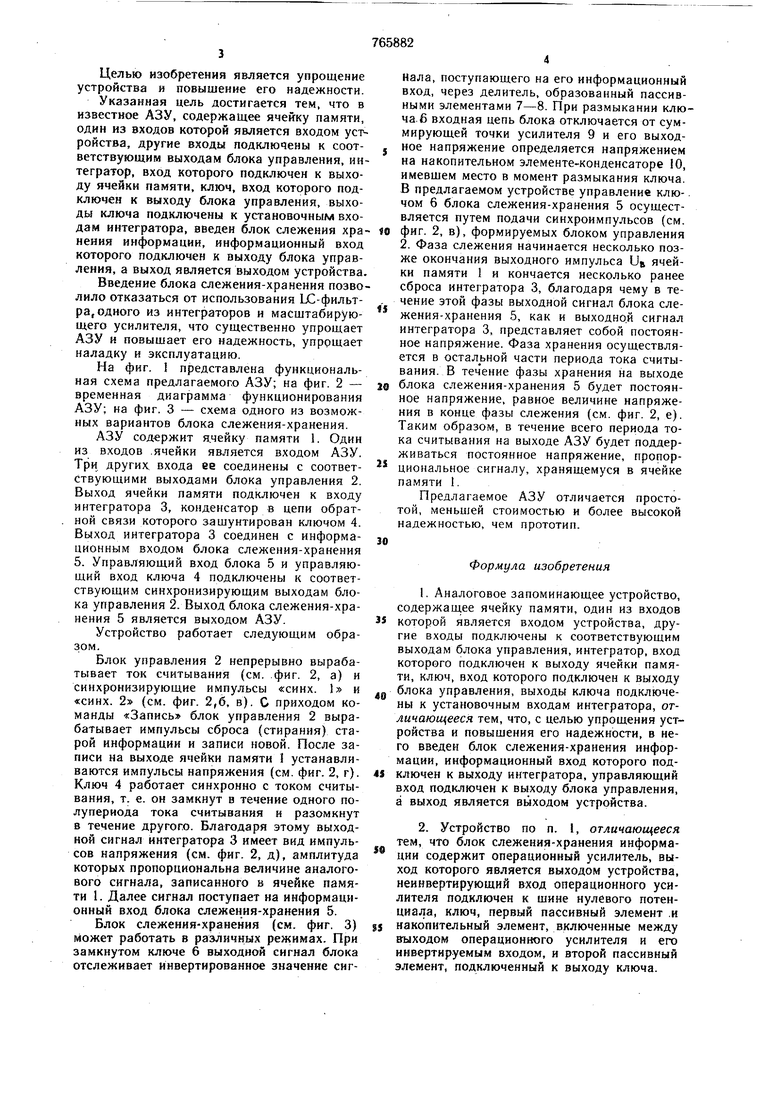

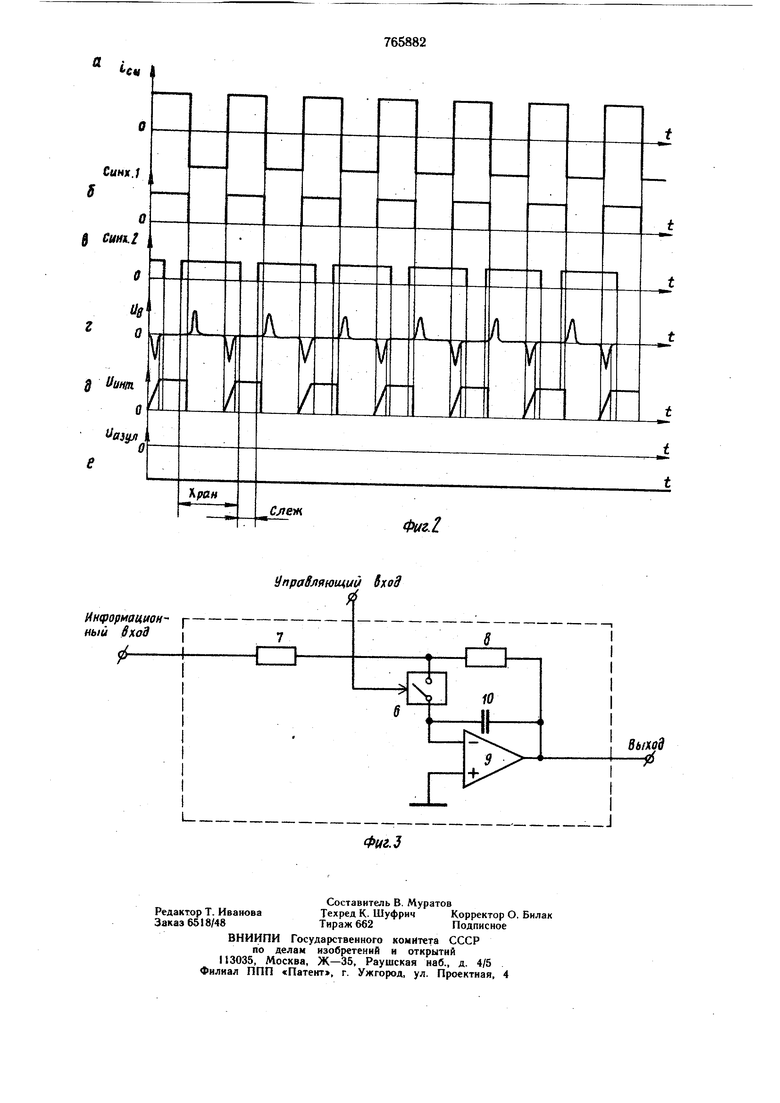

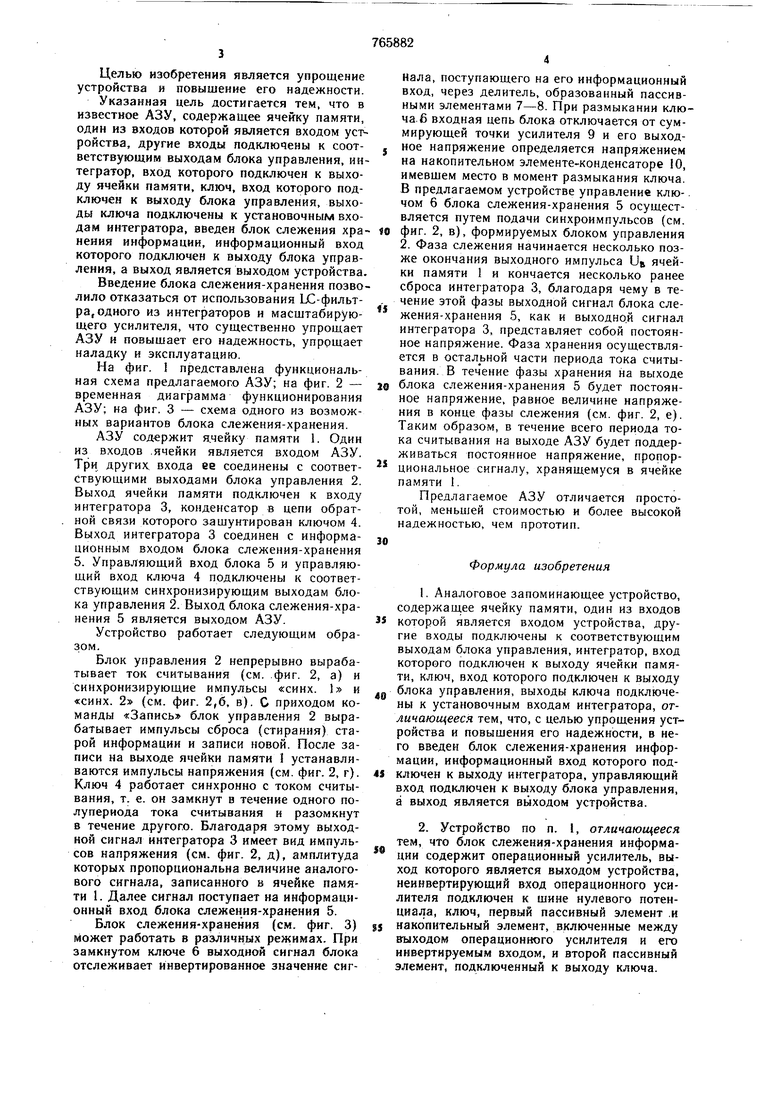

На фиг. 1 представлена функциональная схема предлагаемого АЗУ; на фиг. 2 - временная диаграмма функционирования АЗУ; на фиг. 3 - схема одного из возможных вариантов блока слежения-хранения.

АЗУ содержит ячейку памяти 1. Один из входов .ячейки является входом АЗУ. Три других входа ее соединены с соответствующими выходами блока управления 2. Выход ячейки памяти подключен к входу интегратора 3, конденсатор в цепи обратной связи которого защунтирован ключом 4. Выход интегратора 3 соединен с информационным входом блока слежения-хранения 5. Управляющий вход блока 5 и управляющий вход ключа 4 подключены к соответствующим синхронизирующим выходам блока управления 2. Выход блока слежения-хранения 5 является выходом АЗУ.

Устройство работает следующим образом.

Блок управления 2 непрерывно вырабатывает ток считывания (см. ,фиг. 2, а) и синхронизирующие импульсы «синх. 1 и «синх. 2 (см. фиг. 2,6, в). С приходом команды «Запись блок управления 2 вырабатывает импульсы сброса (стирания) старой информации и записи новой. После записи на выходе ячейки памяти 1 устанавливаются импульсы напряжения (см. фиг. 2, г). Ключ 4 работает синхронно с током считывания, т. е. он замкнут в течение одного полупериода тока считывания и разомкнут в течение другого. Благодаря этому выходной сигнал интегратора 3 имеет вид импульсов напряжения (см. фиг. 2, д), амплитуда которых пропорциональна величине аналогового сигнала, записанного в ячейке памяти 1. Далее сигнал поступает на информационный вход блока слежения-хранения 5.

Блок слежения-хранения (см. фиг. 3) может работать в различных режимах. При замкнутом ключе 6 выходной сигнал блока отслеживает инвертированное значение сигНала, поступающего на его информационный вход, через делитель, образованный пассивными элементами 7-8. При размыкании ключа, б входная цепь блока отключается от суммирующей точки усилителя 9 и его выходное напряжение определяется напряжением на накопительном элементе-конденсаторе 10, имевщем место в момент размыкания ключа. В предлагаемом устройстве управление клю-. чом 6 блока слежения-хранения 5 осуществляется путем подачи синхроимпульсов (см.

фиг. 2, в), формируемых блоком управления 2. Фаза слежения начинается несколько позже окончания выходного импульса U ячейки памяти 1 и кончается несколько ранее сброса интегратора 3, благодаря чему в течение этой фазы выходной сигнал блока слежения-хранения 5, как и выходной сигнал интегратора 3, представляет собой постоянное напряжение. Фаза хранения осуществляется в остал зной части периода тока считывания. В течение фазы хранения на выходе

блока слежения-хранения 5 будет постоянное напряжение, равное величине напряжения в конце фазы слежения (см. фиг. 2, е). Таким образом, в течение всего периода тока считывания на выходе АЗУ будет поддерживаться постоянное напряжение, пропорциональное сигналу, хранящемуся в ячейке памяти 1.

Предлагаемое АЗУ отличается простотой, меньшей стоимостью и более высокой надежностью, чем прототип.

Формула изобретения

1.Аналоговое запоминающее устройство, содержащее ячейку памяти, один из входов

которой является входом устройства, другие входы подключены к соответствующим выходам блока управления, интегратор, вход которого подключен к выходу ячейки памяти, ключ, вход которого подключен к выходу

блока управления, выходы ключа подключены к установочным входам интегратора, отличающееся тем, что, с целью упрощения устройства и повыщення его надежности, в иего введен блок слежения-хранения информации, информационный вход которого подключен к выходу интегратора, управляющий вход подключен к выходу блока управления, а выход является выходом устройства.

2.Устройство по п. 1, отличающееся тем, что блок слежения-хранения информации содержит операционный усилитель, выход которого является выходом устройства, неинвертирующий вход операционного усилителя подключен к шине нулевого потенциала, ключ, первый пассивный элемент .и

накопительный элемент, включенные между выходом операционного усилителя и его инвертируемым входом, и второй пассивный элемент, подключенный к выходу ключа.

Источники информации, принятые во внимание при экспертизе I. Вотрин В. Ф. и др. Использование принципа динамического смещения при записи для построения быстродействующих разомкнутых аналоговых запоминающих устройств на трансфлюксорахЛАвтоматика и телемеханика,1971, № 6.

2.Авторское свидетельство СССР № 474052, кл. О И С 27/00, 1973.

3.Вотрин В. Ф. и др. Быстродействующее устройство считывания информации для аналоговых ЗУ на трансфлюксорах. Приборы и системы информации, 8, 1975, с. 33-34 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| Дискретный интегратор | 1975 |

|

SU705468A1 |

| ФОТОПРИЕМНОЕ УСТРОЙСТВО С КОМПЕНСАЦИЕЙ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ | 1992 |

|

RU2065669C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ | 2012 |

|

RU2521305C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU649042A1 |

| Устройство для измерения ортогональных составляющих сигнала | 1987 |

|

SU1465809A1 |

Команда записи

Упрсг ляющиИ бхвЗ

Авторы

Даты

1980-09-23—Публикация

1979-01-09—Подача