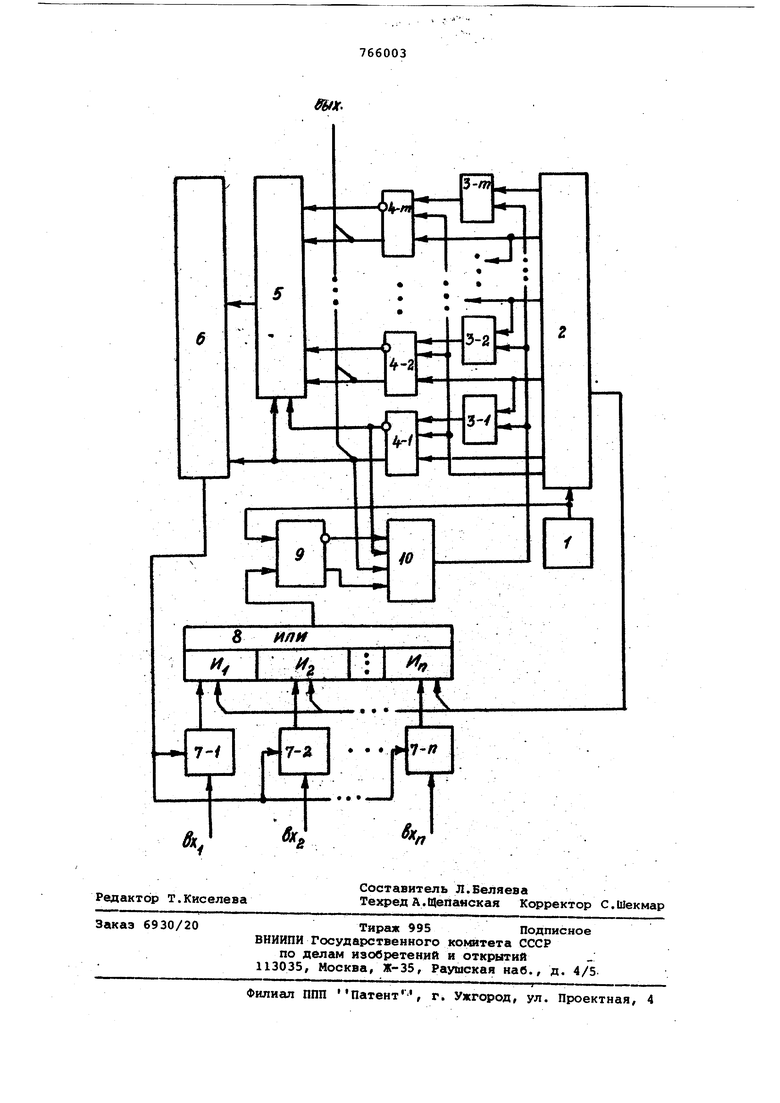

Изобретение относится к аналогоцифровой вычислительной технике и предназначено для преобразования ана логовых сигналов в игровую формуИзвестен цифровой вольтметр для измерения разнополярных напряжений, содержащий блок сравнения, выход которого через блок управления и дешиф тор подключен к цифровому индикатору, и источник опорного напряжения, подключенный через цифроангшоговый преобразователь и аналоговое запоминающее устройство ко входу блока сравнения устройства 1. Его недостатком является низкое быстродействие, обусловленное инерци онностью аналогового запоминающего устройства. Известен аналого-цифровой преобра зователь, содержащий блок управления выход которого через элементы совпадения, триггеры регистра числа и цифроаналоговый преобразователь подключен ко входу сравнивакхцего устройства 2 . Недостатком этого преобразователя является его функциональная ограниченность, так как он не способен пре образовывать в код многоканальную бй .полярную аналоговую информацию. Цель изобретения - расширение функциональных возможностей аналогоцифрового преобразователя. Поставленная цель достигается тем, что в многоканальный аналого-цифровой преобразователь биполярных сигнгшов, содержащий блок сравнения, генератор, выход которого соединен со входом блока управления, -выходы которого подключены к .единичным входам триггеров и через первые входы элементов совпадения к нулевым входам триггеров, цифроаналоговый преобразователь, введены ксжмутатор кодов, п - 1 блок сравнения, элемент 2И - И ИЛИ,Dтриггер, сумматеч по модулю 2, причем эторые вход№ элементов совпадения соединены с выходом сумматора по модулю 2, первый и второй входы которого соединены срртветствеино с инверсным и пря14ым выходами первого триггера, а третий и четвертый входы соединены соответственно с инверсным и прямым выходами D-триггера, тактовый вход . которого соединенс выходом генератора, а О-вход с вьрсодом элемента 2И -И 1ИЛИ, первые входы которого соединены со вторыми выходами блока управления, а вторые входы с выходгши блока сргшнения, первые входы которых подключены ко входным шинам, а вторые входы через цифроаналоговый преобра эователь к выходу коммутатора кодов, при этом выходы триггеров соединены со входами коммутатора, кодов, а прямой выход первого триггера соеди нен со входом цифроаналогового преобразователя, причем третий выход блока.управления подключен к нулевым входам триггеров. На чертеже представлена блок-схема многоканального аналого-цифрового преобразователя биполярных сигналов. Схема содержит генератор 1, блок 2 управления, элементы 3 совпадения, триггеры 4, коммутатор 5 кодов, цифроаналоговый преобразователь б, блол и 7 сравнения, элемент 2И - И ИЛИ 8,ТЭ-триггер 9, сумматор 10 по моду лю 2. Преобразователь работает следующим образом. Триггер 4-1 является знаковым три гером преобразователя, которалй в нулевом состоянии разрешает поступление через коммутатор кодов на вход преобразователя 6 прямого кода с три геров 4-2 . .. 4-W1, а в единичном состоянии обратного кода, таким образом на вход преобразователя 6 пост пает через коммутатор кодов прямой или обратной код с выходов триггеров 4-2 0.0 4-П1« Кроме того, прямым выход триггера 4-1 заведен на вход преобразователя 6, на выходе которого появляется нулевой потенциал, ког Триггер 4-1 в нулевом состоянии и отрицательное напряжение Uy,, (макси мальное отрицательное напряжение, пре образуемое устройством), когда он в единичном состоянии (при этом осталь ные Триггеры отключены). Триггеры 4-2 ..о 4-тформируют на выходе преобразователя 6 положительное напряжение в диапазоне от О до Utytcaii так как раздельное их включение в единич ное состояние (остальные триггеры, кроме рассматриваемого, находятся в нулевом состоянии) дает при включении триггера.4-2 напряжениеУ § ; триггера 4-°3 - и, т.д. Преобразова тель (, примененный в предложенном уст ройстве, является биполярным, так как ра;зличным сочетанием установки в единичное и нулевое состояние триг геров 4--1 - 4-W1 на выходе преобразоватеЛя б можно получить любое напряжение в диапазоне ± Шааа... Ь тройство при пре образрвании положительного напряжения работает сле дукйдим образом. Схема И элемента 2H-(i ИЛИ открыт соответствующей командой блока управ ления, который из выходных импульсов генератора вырабатывает w+ 2 тактЬ-. выз импульса, сдвинутых во времени («-разрядность выходного кода преобр зователя) . Первый тактовый импульс блока управления устанавливает триггеры 4-1...4-1П1В нулевое состояние, при этом на вход преобразователя 6 поступает прямой код (00...0) с выходов триггеров, и на его выходе формируется нулегвой потенциал. Второй тактовый импульс устанавливает триггер 4-1 в единичное состояние, при этом на вход преобразователя 6 поступает в обратный код (11... 1) с триггеров 4-2...4-Уи, который формирует на его выходе положительное напряжение Uyfloi Одновременно по команде триггера 4-1 на выходе формируется отрицательное напряжение Ууцат .Таким Зом суммарный потенциал на выходе преобразователя 6 равен нулю, так как выполняется условие ,, о 2П1-Ч иха-. Так как входное напряжение преобразователя, положительное, то на выходе блока 7-1 сравнения сохраняется i низкий уровень, который через элемент 2H-V ИЛИ поступает на Ю- вход триггера 9, который синхроимпульсом с генег ратора устанавливается в нулевое состо ие и на выходе сумматора 10 появляется высокий (разрешающий) потенциал. Третий тактовый импульх: блока . управления через элемент 3-1 совпадения возвращает триггер 4-1 в нулевое состояние (определяя знак выходного кода преобразователя и устанавливает триггер 4-2 в единичное состояние, при этом на вход преобразователя б поступает прямой код (10..О) с выходов триггеров 4-2...4-hi на выходе преобразователя б появляется положительное напряжение Usgib , Если входное напряжение преобразователя больше выходного потенциала преобразователя б, то на выходе блока 7-1 низкий уровень сохраняется, триггер 9 остается в нулевом состоянии, а на выходе сумматора 10 отсутствует разрешающий поте11циап (триггер 4-1 в нулевом состоянии) . Четвертый, тактовый импульс устанавливает триггер 4-3 в единичное состояние, формируя на выходе преобразователя 6 напряжение . Если входное -напряжение преобразователя после третьего такта меньше вьюсодного потенциала преобразовател.я б, то на выходе блока 7-1 появляется высокий уровень, триггер 9 переключается в единичное состояние и йа выходе сумматора 10 появляется разрешающий потенциал. Четвертый тактовый импульс через схему совпадения 3-2 возвращает триггер 4-2 в нулевое состояние и устанабливает триггер 4-3 в единичное состояние, при этом на выходе преобразователя б появляется напряжение siJ и т.д. По уи+ 2 тактовому импульсу процесс преобразования входного напряжения завершается, а схема управления 2 открывает схему U/j, эле мента 2И-11 ИЛИ.

Предположим, что на входе второгоканала (на входе блока сравнения 7 Ц2) - отрицательное напряжение. Работа устройства по первому и второму тактовым импульсам блока управления аналогична преобразованию положительного напряжения, при этом на выходе блока 7-2 появляется высокий уровень, так как нулевой потенциал на выходе преобразователя 6 выше потенциала на входе блока 7-2. Высокий уровень с блока 7-2 через 2И элемента 2H-h ИЛИ поступает на вход триггера 9, который синхноимпульсом с генератора устанавливается в единичное состояние и на выходе сумматора 10 отсутствует разрешающий потенциал, следовательно, элемент 3-1 совпадения закрыт и ; триггер 4-1 третьим тактовым голпуйьсом не сбрасывается (таким образом, знак выходного кода определен). Третий тактовый импульс устанавливает триггер 4-2 в единичное состояние, при этом на вход преобразователя 6 . поступает обратный код (01...1) с триггеров 4-2...4-П1, а на выходе пре образователя 6 появляется отрицатель ное напряжение - (с выхода преобразователя 6 отключено положительное напряжение 2 (см. выражение) . Если входное напряжение по абсолютной величине больше выходного потенциала преобразователя б, то на выходе блока 7-2 высокий уровень сохраняется, триггер 9 остается в состоянии , следовательно, элемент 3-2 совпадения закрыт и четвертый тактовый импульс устанавливает триггер 4-3 в единичное состояние, при этом на преобразователь 6 поступает обратный код (001...1) с триггеров 4-2 - , а на выходе преобразователя б формируется ,отрицательное напряжение 3/4 Uvncx«., I (о выхода преобразователя 6 отключены Iположительные напряжения и .у ) ,и т.д..

I Таким образом, при преобразовании входного отрицательного напряжения . ; производится отключение н& выходе преобразователя 6 определенного выбора слагаемых , ,... установкой соответствующих три ггеров 4-2 4-(., в единичное состояние. По (п + 2) тактовому импульсу процесс преобразования входного напряжения завершается, а блок управления 2 откры;BaeT Uj элемент 2И-М ИЛИ и т.д.

-Введение в аналого-цифровой преобразователь новых узлов - Ч-1, схем сравнения, блока И-ИЛИ, D-триггера, сумматора по модулю2 и коммутатора

кодов расширяет функциональные возможности АЦП, так как он способен преобразовывать в код многоканальную биполярную аналоговую информацию; повышает гочностЪ преобразования мкогока, наАьнэй информации, так как отсутствует коммутация (перек,таочение) аналоговых сигналов и сопровождающие ее погрешности и помехи; результат преобра.зования выдается в прямом коде для - входных напряжений любой полярности; упрощает переключение каналов.

Формула изобретения

5 Многоканальный аналого-цифровой преобразователь биполярных сигналов, содержащий блок сравнения, генератор, выход которого соединен со входом блока управления, выходы которого подключены к единичным входам триггеров и через первые входы элементов совпадения к нулевым входам триггеров, циф1роаналоговый преобразователь, отличающийся тем, что, с

5 целью расширения функциональных возможностей преобразователя, в него : {введены коммутатор кода,ц -1 блок сравнения, элемент 2И-й ИЛИ, TS-TpHrf irep, сумматор по модулю {2, примем вто :рые входы элементов -совпадения .Ъоедиг.

нены с выходом сумматора подмодулю 2, первый и второй входы которого соединены соответственно ic инверсным и прямым выходами первого триггера, а третий и четвертый входы соединены с

инверсным и прямым выходами В-триггёра, тактовый вход которого соединен с выходом генератора, а в-вход с выходом элемента 2И-ИИЛИ, первые входы которого соединены со вторыми выходами

0 блока управления, а вторые входы с вы. кодами блоков сравнения, первые входы

которых подключены ко входным шинам,

а вторые входы через цифроаналоговый

преобразователь к выходу коммутатора

с содов, при этом выходы триггеров со- , единены со входами коммутатора кодов, а прямой выход первого триггера сое:динен со вторым входом цифроанало о вого преобразователя, причем третий

Q i выход блока управлейиЯ подключен к нулевым входс1м триггеров.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

310387, кл. Н 03 К 13/17, 24.11.69.

2.Шпяндин В.М. Цифровые измери- . тельные преобразователи и приборы. М., Высшая школа , 1973.

3-/w,

94

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для двухкоординатного управления рабочим органом | 1990 |

|

SU1815620A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Регистратор сигналов с усреднением | 1982 |

|

SU1112230A1 |

Авторы

Даты

1980-09-23—Публикация

1978-10-03—Подача