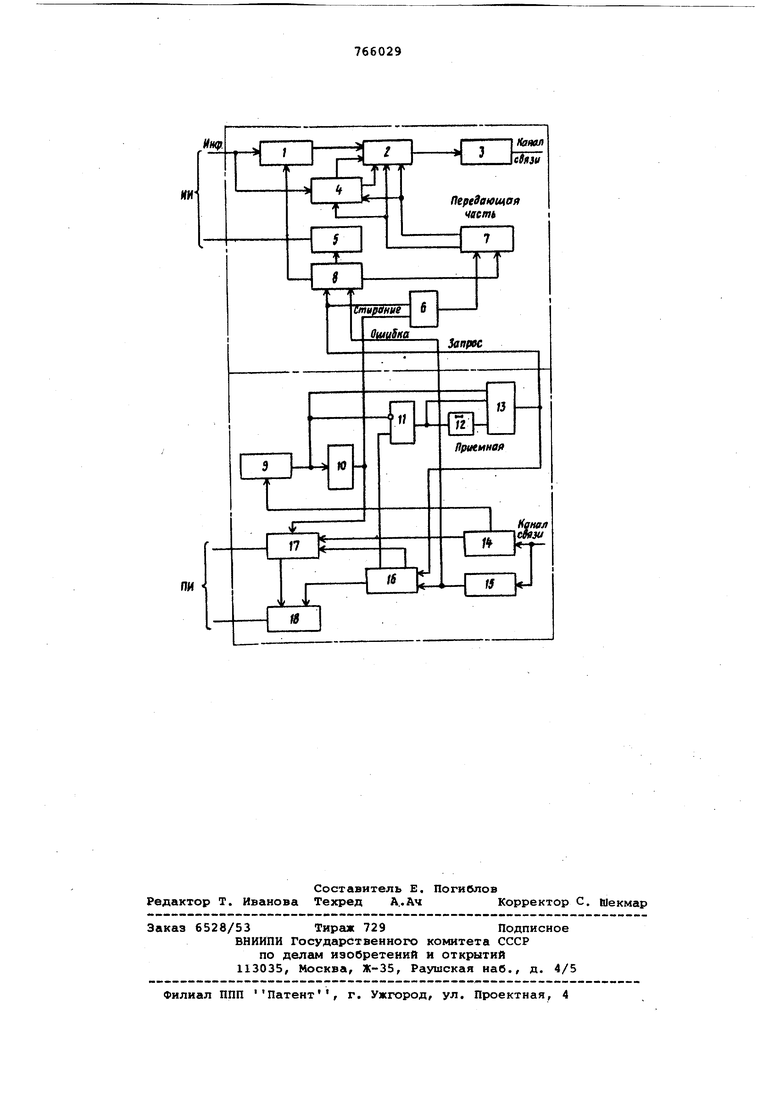

Изобретение относится к технике связи и может использоваться в систе мах передачи данных с решакнцей обратной связью. Известно устройство для ЗсИЦИТЫ от ошибок, содержащее на передаче последовательно соединенные первый входной накопитель, переключатель и кодер, информационный вход первого входного накопителя объединен с первым входом блока памяти, к второму входу которого подключен соответству ющий вход переключателя и выход первого счетчика блокировки, к входу ко торого и к соответствующему входу первого входного накопителя подключе ны соответственно первый и второй выходы датчика команд, третий выход которого подключен к входу датчика сигналов обмена, а выход блока памяти подключен к соответствукмцему входу переключателя, а на приеме - последовательно соединенные второй входной накопитель, выходной накопитель и второй датчик сигналов обмена информационный вход второго входного накопителя объединен с входом декодера, один из выходов которого через второй счетчик блокировки подк.гаочен соответствующим входам второго датчи ка сигналов обмена и выходного накопителя и непосредственно к входу Ошибка датчика служебных команд, а другой (ВЫХОД второго входного накопителя подключен к входу дешифратора служебных команд 1 . Однако известное устройство имеет недостаточную достоверность обиаруже- . ния ошибок. Цель изобретения - повьлаение достоверности обнаружения ошибок. Для этого в устройстве для защиты от ошибок, сьдержсццем на передаче последовательно соединенные первый входной накопитель, переключатель и кодер, информационный вход первого входного накопителя объединен с первым входом блока памяти, к второму входу которого подключен соответствующий вход переключателя и выход первого счетчика блокировки, к входу которого и к соответствующему входу первого входного накопителя подключены соответственно первый и второй выходы датчика . команд, третий выход которого подключен к входу датчика сигналов обмена, а выход блока памяти подключен к соответствующему входу переключателя, а на приеме - последовательно соединенные второй входной накопитель, выходной накопитель и второй датчик сиг налов обмена, информационный вход . второго входного накопителя объединен с входом декодера, один из выходов которого через второй счетчик бло кировки подключен к соответствующим входам второго датчика сигналов обмена и.выходного накопителя и непосредственно к входу Ошибка датчика служебных команд, а другой выход втор.ого входного накопителя подключен к входу дешифратора служебных команд, введены на передаче элемент И, включенный между входом датчика команд и дополнительным входом первого счетчи ка блокировки, а на приеме - последовательно соединенные элемент НЕТ, линия задержки и элемент ИЛИ, к двум другим входам которого подключены соответственно выход элемента НЕТ и вход дополнительного счетчика, соеди ненного с выходом дешифратора служебных команд и одним из входов элемента НЕТ, к другому входу которого подключен дополнительный выход второ го счетчика блокировки, к дополнител ному входу которого подключен выход элемента ИЛИ, соединенный с входом датчика команд, а выход дополнительного счетчика подключен к другому вх ду элемента Инк дополнительному входу выходного накопителя, а допол тнительный выход первого счетчика бло кировки подключен к дополнительным входам переключателя непосредственно и через блок памяти. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство содержит на передающей части входной накопитель 1, переключатель 2, кодер 3, блок 4, памяти, датчик 5 сигналов обмена, элемент И 6, счетчик 7 блокировки и датчик 8 команд, а на приемной части - дешифратор 9 служебных команд, счетчик 10, элемент НЕТ 11, линию задержки 12, элемент ИЛИ 13, входной накопитель 14, декодер 15, счетчик 16 блокировки, выходной накопитель 17 и датчик 18 служебных команд. Устройство работает следующим образом. При отсутствии искажений в принимаемой информации датчик 5 посылает источнику сигнал о готовности принят от него очередную комбинацию, которая записывается во входной накопитель 1 и блок 4 памяти. Затем с помощью кодера 3 вводится необходимая избыточность, и кодовая комбинация поступает в канал связи. На приемной стороне данная комби нация поступает во входной накопитель 14 и одновременно в декодер 15 где происходит обнаружение ошибок в комбинации. Если ошибка не обнару жена, то комбинация переписывается выходной накопитель 17, и датчик 18 сигналов обмена сообщает потребителю информации о готовности выдать ему информацию. Ниже рассматривается работа устройства при искажении информации. Пусть при передаче информации со станции А произошло искажение комбинации В, При обнаружении ошибок на выходе декодера 15 появляется сигнал, который подается на счетчик 16 блокировки и на датчик 8. команд. Сигнал со второго выхода счетчика 16 блокирует прием h-комбинаций в выходной накопитель 17, Датчик 8 записывает комбинацию во входной накопитель 1 и включает счетчик 7 блокировки, сигнал с первого выхода которого обеспечивает считывание h-комбина-; ц,ий из блока 4 памяти через переключатель 2 вслед за командой Нет. Станция А вьщеляет с помощью дешифратора 9 служебных команд команду Нет, сигнал с выхода которого подается на счетчик 16 блокировки, В результате, так же как и на станции Б, осуществляется блокировка выходного накопителя 17 и обратный канал (на станцию А) посылается команда Нет и h-комбинаций из блока 4 :памяти. Таким образом, осуществляется исправление возникающих ошибок в результате повторения передачи hкомбинаций и команды Нет в обоих направлениях. Теперь предполагают, что команда , Нет в обратном: канале исказилась и превратилась в разрешенную комбинацию. На станции А блокировки приемника не происходит, команда на. станцию Б не посылается, станция А продолжает передачу информации от источника, в приемнике станции А появляются лишние комбинации. В конце цикла блокировки на станцию Б вместо команды приходит другая комбинация. В результате сигнал с третьего выхода счетчика 16 блокировки проходит хЧерез открытую схему НЕТ 11 и схему ИЛИ 13 и попадает на датчик 8 команд по шине Запрос. Датчик 8 обеспечивает блокировку приемника на h-комбинаций, посылку команды Нет .Сигнал с выхода элемента НЕТ 11 также проходит через элемент задержки на п элементов (п-длина комбинации),элемент ИЛИ 13 ,и вызывает посылку второй команды Нет в канал связи. При этом сигналом с выхода счетчика 7 блокировки с помощью переключателя 2 обеспечивается увеличение цикла блокировки на 1 комбинацию передачи данных из входного накопителя и передача h-комбинат ций из блока 4 памяти вслед за второй командой Нет. В приемной части станции А дешифратор 9 служебных команд выделяет перНет, в: результате че вую команду го через элемент ИЛИ 13 посылается сигнал Запрос на датчик 8 команд который обеспечивает передачу команJ ды Нет на;- станцию Б, с помощью счетчика 16 блокируется выходной накопитель 17 на время приема h-комбинаций. После прихода второй команды Нет на станцию А срабатывает счетчик 10, сигналом с выхода которого стираются h-комбинаций, накопленных ранее в выходном накопителе 17.Этот же сигнал попадает на второй вход элемента И 6 в передающей части, которая в это время открыта сигналом по шине Запрос. В результате на выходе элемента И б появляется сигнал, попадаюсций на вт рой вход счетчика 7 блокировки. Счет чик срабатывает и появляется сигнал на его втором выходе, который попада ет на пятый вход переключателя.2 и третий вход блока 4 памяти. В резуль тате со второго выхода блока 4 памяти через переключатель 2 описываются в канал связи 2Ь-комбинаций. Таким образом происходит исправле ние появившихся искажений в прямом и обратном каналах. Предлагаемое устройство позволяет уменьшить вероятность появления вста вок и выпаданий комбинаций в принимаемой информации и уменьшить вероятность необнаружения ошибок, поскол ку обнаруживается превращение коман,ды Нет в разрешенную комбинацчкз..; Формула изобретения Устройство для защиты от ошибок, содержащее на передаче последовательно соединенные первый входной на:копитель, переключатель и кодер, информационный вход первого входного накопителя объединен с первым входом блока памяти, к второму входу которого подключен соответствующий вход переключателя и выход первого счетчика блокировки, к входу которого и к соответс1вующему входу первого входного накопителя подключены соответственно первый и второй выходы датчика команд, третий выход которого подключен к входу датчика сигналов обмена, а выход блока памяти подключен к соответствующему входу переключателя, а на приеме - последовательно соединенные второй входной накопитель, выходной накопитель и второй датчик сигналов обмена, информационный вход второго входного накопителя объединен с входом декодера,один из выходов которого через второй счетчик блокировки подключен к соответствующим входам второго датчика сигналов обмена и выходного накопителя и непосредственно к входу Ошибка датчика служебных команд, а другой выход второго входного накопителя подключен к входу дешифратора служебных команд, о т л и ч а ю щ .е е с я тем, что, с целью повышения достоверности обнаружения ошибок, введены на передаче элемент И, включенный между входом датчика команд и дополнительHfcjM входом первого счетчика блокировки, а на приеме - последовательно соединенные элемент НЕТ, линия задержки и элемент ИЛИ, к двум другим входам которого подключены соответственнЗэ выход элемента НЕТ и вход дополнительного счетчика, соединенного с выходом дешифратора служебных.команд и одним из входов элемента НЕТ, к другому входу которого подключен дополнительный выход второго счетчика блокировки, к дополнительному входу которого подключен выход элемента ИЛИ, соединенный с входом датчика команд, а выход дополнительного счетчика подключен к другому входу элемента И и к дополнительному входу выходного накопителя, а дополнительный выход первого счетчика блокировки подключен к дополнительным входам переключателя непосредственно и через блок памяти. Источники информации, принятые во внимание при экспертизе 1. Шпяпоберский В.И. Основы техники передачи дискретных сообщений., М.,СвязьГ 1973, с. 398, фиг. 1 (прототип).

Наяал

Н- паяал ter

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство защиты от ошибок | 1983 |

|

SU1272514A1 |

| Устройство для регистрации и передачи информации | 1976 |

|

SU658592A1 |

| Устройство для регистрации и передачи информации | 1979 |

|

SU781873A2 |

| Устройство для передачи и приема информации | 1985 |

|

SU1338089A1 |

| Устройство защиты от ошибок с решающей обратной связью | 1980 |

|

SU866766A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СОСТОЯНИЯ И УПРАВЛЕНИЯ КАНАЛАМИ И ТЕХНИЧЕСКИМИ СРЕДСТВАМИ В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1991 |

|

RU2007878C1 |

| Устройство обнаружения и исправления вставок и выпадений информации | 1979 |

|

SU866765A1 |

| Устройство для обнаружения неисправного регенератора | 1988 |

|

SU1561207A1 |

| Система передачи дискретной информации | 1982 |

|

SU1061277A1 |

Авторы

Даты

1980-09-23—Публикация

1978-09-05—Подача