1

Изобретение относится к технике передачи дискретной информации и может быть ис.пользовано при модернизации существующей и создании новой аппаратуры передачи данных.

Известно устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенные входной накопитель, дешифратор служебных комбинаций, счетчик блокировки и датчик сигнала обмена, а также декодирующий блок, выходной накопитель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций,а выход распределителя подключен к первым|1входам входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей,а выход входного накопителя подключен к третьему входу выходного накопителя, выход которого подключен к второму входу датчика сигнала обмена,причем третий вход входного накопителя объединен со входом декодирующего блока и является входом устройства 11.

Однако известное устройство обладает низкой помехоустойчивостью.

Цель изобретения - повышение помехоустойчивости.

Для этого в устройство защиты от ошибок срешающей обратной связью, содержсццее последовательно соединенные входной накопитель, дешифратор служебных комбинаций, счетчик блокировки и датчик сигнала обмена, а также декодирующий блок, выходной нако10питель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций, а выход распределителя подключен к первым входам входного и выходного 15 накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей, а выход входного накопителя подключен к третьему входу выходного нако20пителя, выход которого подключен к . второму входу датчика сигнала обмена, причем третий вход входного накопителя объединен со входом декодирующего блока и является входом устрой25ства, введены элемент И и блок анализа результатов декодирования, к первому входу которого и первому входу элемента И подключен выход декодирующего блока, а к вторым входам

30 блока анализа результатов декодирования и элемента И подключен выход распределителя, при этом выход элемента И подключен к второму входу счетчика блокировки. Кроме того, блок анализа результатов декодирования содержит последовательно соединенные первый элемент ЗАПРЕТ,первый элемент И, триггер,второй элемент И,первый счетчик, третий элемент И, второй счетчик и второй элемент ЗАПРЕТ, при этом выход второго счетчика подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход третьего элемента ЗАПРЕТ, а выход элемента ИЛИ подключен к установочным входам первого и второго счетчиков и триггера, второй выход которого подключен к второму входу первого элемента И, первый выход которого подключен к второму входу третьего элемента И и запрещающему входу третьего элемента ЗАПРЕТ, к второму входу которого подключен выход первого счетчика.

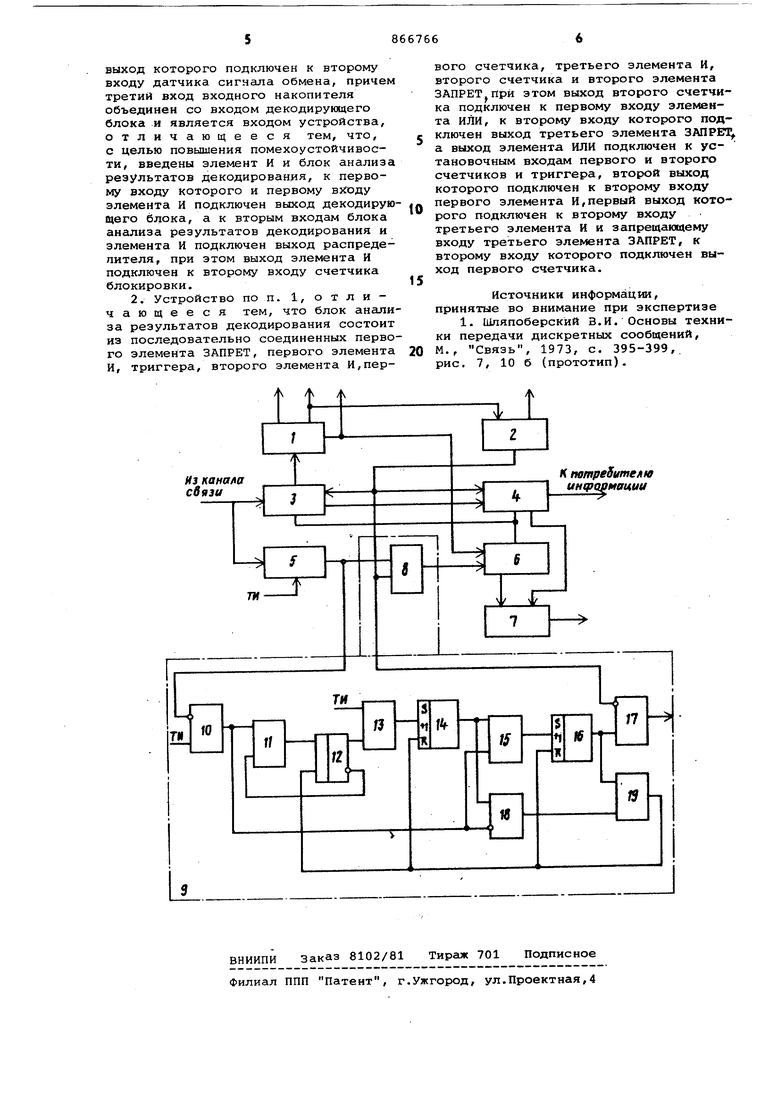

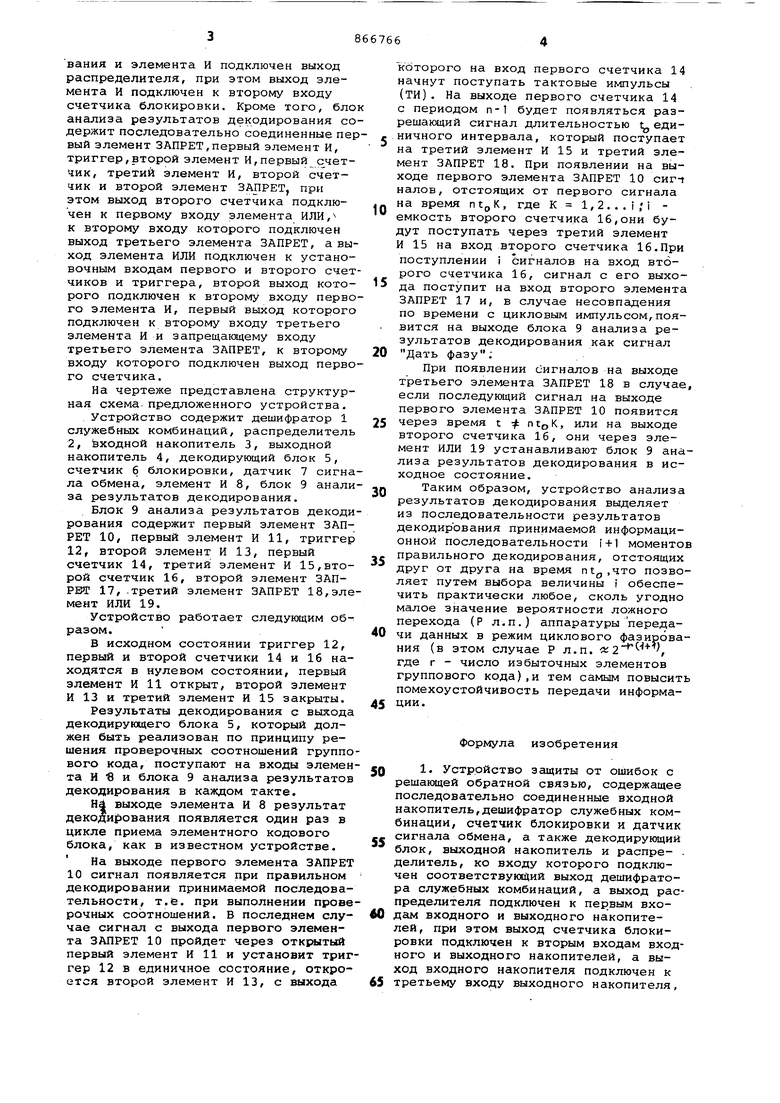

На чертеже представлена структурная схема предложенного устройства.

Устройство содержит дешифратор 1 служебных комбинаций, распределитель 2, входной накопитель 3, выходной накопитель 4, декодирующий блок 5, счетчик б блокировки, датчик 7 сигнала обмена, элемент И 8, блок 9 анализа результатов декодирования.

Блок 9 анализа результатов декодирования содержит первый элемент ЗАПРЕТ 10, первый элемент И 11, триггер 12, второй элемент И 13, первый счетчик 14, третий элемент И 15,второй счетчик 16, второй элемент ЗАПРЕТ 17, .третий элемент ЗАПРЕТ 18,элемент ИЛИ 19.

Устройство работает следующим образом.

В исходном состоянии триггер 12, первый и второй счетчики 14 и 16 находятся в нулевом состоянии, первый элемент И 11 открыт, второй элемент И 13 и третий элемент И 15 закрыты.

Результаты декодирования с выхода декодирующего блока 5, который должен быть реализован по принципу решения проверочных соотношений группового кода, поступают на входы элемента И 8 и блока 9 анализа результатов декодирования в каждом такте.

на выходе элемента И 8 результат декодирования появляется один раз в цикле приема элементного кодового блока, как в известном устройстве.

На выходе первого элемента ЗАПРЕТ 10 сигнал появляется при правильном декодировании принимаемой последовательности, т.е. при выполнении проверочных соотношений. В последнем случае сигнал с выхода первого элемента ЗАПРЕТ 10 пройдет через откцалтый первый элемент И 11 и установит триггер 12 в единичное состояние, откроется второй элемент И 13, с выхода

которого на вход первого счетчика 14 начнут поступать тактовые импульсы (ТИ). На выходе первого счетчика 14 с периодом п-1 будет появляться разрешающий сигнал длительностью t единичного интервала, который поступает на третий элемент И 15 и третий элемент ЗАПРЕТ 18. При появлении на выходе первого элемента ЗАПРЕТ 10 сигп налов, отстоящих от первого сигнала на время ntj,K, где К l,2...i,i емкость второго счетчика 16,они будут поступать череэ третий элемент И 15 на вход второго счетчика 16.При поступлении i Сигналов на вход второго счетчика 16, сигнал с его выхода поступит на вход второго элемента ЗАПРЕТ 17 и, в случае несовпадения по времени с цикловым импульсом,появится на выходе блока 9 анализа результатов декодирования как сигнал Дать

При появлении сигналов на выходе третьего элемента ЗАПРЕТ 18 в случае если последующий сигнал на выходе первого элемента ЗАПРЕТ 10 появится через время t :/: ntpK, или на выходе второго счетчика 16, они через элемент ИЛИ 19 устанавливают блок 9 анализа результатов декодирования в исходное состояние.

Таким образом, устройство анализа результатов декодирования выделяет иэ последовательности результатов декодирования принимаемой информационной последовательности i+1 моменто правильного декодирования, отстоящих друг от друга на время ntg,4TO позволяет путем выбора величины i обеспечить практически любое, сколь угодно малое значение вероятности ложного перехода (Р л.п.) аппаратуры передачи данных в режим циклового фазирования (в этом случае Р л.п. Х2, где г - число избыточных элементов группового кода),и тем самым повысит помехоустойчивость передачи информации.

Формула изобретения

1. Устройство защиты от ошибок с решаклцей обратной связью, содержащее последовательно соединенные входной накопитель,дешифратор служебных комбинации, счетчик блокировки и датчик сигнала обмена, а также декодирующий блок, выходной накопитель и распре- . делитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций, а выход распределителя подключен к первым вхо0 Дс1М входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей, а выход входного накопителя подключен к

5 третьему входу выходного накопителя,

выход которого подключен к второму входу датчика сигнала обмена, причем третий вход входного накопителя объединен со входом декодирующего блока и является входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости, введены элемент И и блок анализа результатов декодирования, к первому входу которого и первому входу элемента И подключен выход декодирующего блока, а к вторым входам блока анализа результатов декодирования и элемента И подключен выход распредепителя, при этом выход элемента И подключен к второму входу счетчика блокировки,

2. Устройство по п. 1, отличающееся тем, что блок анализа результатов декодирования состоит из последовательно соединенных первого элемента ЗАПРЕТ, первого элемента И, триггера, второго элемента И,перИз канала связи

вого счетчика, третьего элемента И, второго счетчика и второго элемента ЗАПРЕТ При этом выход второго счетчика подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход третьего элемента ЗАПРЕТ, а выход элемента ИЛИ подключен к установочным входс1М первого и второго счетчиков и триггера, второ выход которого подключен к второму входу первого элемента И,первый выход котоOрого подключен к второму входу третьего элемента И и запрещающему входу третьего элемента ЗАПРЕТ, к второму входу которого подключен выход первого счетчика.

5

Источники информации, принятые во внимание при экспертизе

1. Шпяпоберский В.И. Основы техники передачи дискретных сообщений, М., Связь, 1973, с. 395-399, рис. 7, 10 б (прототип). К nampeSume/tte информации

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1985 |

|

SU1338089A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство защиты от ошибок | 1983 |

|

SU1272514A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1693732A1 |

| Устройство сопряжения ЭВМ с общим каналом связи | 1988 |

|

SU1668980A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

Авторы

Даты

1981-09-23—Публикация

1980-01-02—Подача