ff/rf sf eflff t o anffff ot/

Й1Г/7гр/т7а

OffOjt

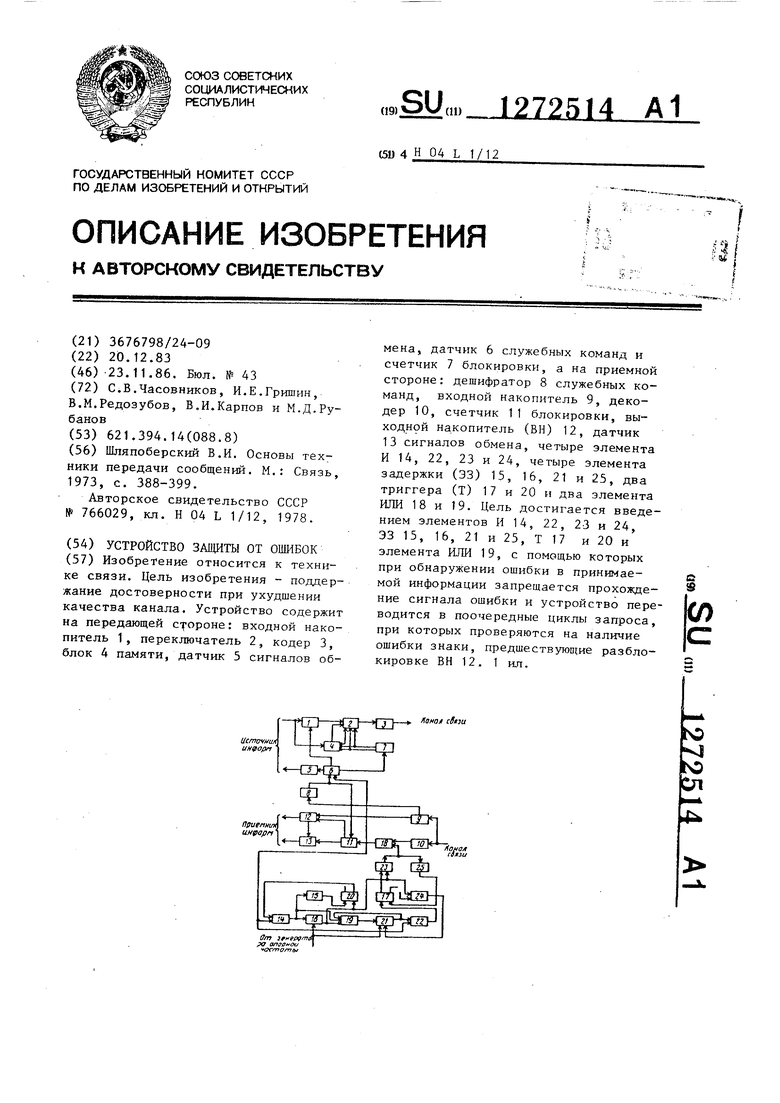

связи f Изобретение относится к технике связи и может быть использовано в системах передачи данных с решающей обратной связью. Цель изобретения - поддержание . достоверности при ухудшении качества канала. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство защиты от ошибок содер жит на передающей стороне входной на копитель 1, переключатель 2, кодер 3, блок 4 памяти, датчик 5 сигналов обмена, датчик 6 служебных команд, счетчик 7 блокировки, а на приемной стороне - дешифратор 8 служебных команд, входной накопитель 9, декодер 10; счетчик 11 блокировки, выходной накопитель 12, датчик 13 сигналов обмена, первый элемент И 14, первый 15 и BTopoit 16 элементы за-, держки, первый триггер 17, первый и второй элементы ИЛИ 18 и 19, второй триггер 20, третий элемент 21 задержки, второй, третий и четвертый элементы И 22 - 24 и четвертый элемент 25 задержки. Устройство защиты от ошибок рабо тает следующим образом, При отсутствии искажений в принимаемой информации датчик 5 сигналов обмена посылает источнику информации сигнал о готовности принять от него очередную комбинацию, которая записывается во входной накопитель 1 и в блок 4 памяти. Затем с помощью кодера 3 вводится необходимая избыточность и кодовая комбинация передается в канал связи. На приемной стороне данная комби нация поступает во второй ВХОДНОР накопитель 9 и одновременно в декодер 10, где происходит обнаружение ощибки в комбинации. Если ошибка не обнаружена, то комбинация переписывается в выходной накопитель 12 и датчик 13 сигналов обмена сообщает потребителю информации о готовности выдать ему информацию. Если приемная станция обнаружит искаженный зна то на выходе декодера 10 появится сигнал, который через первый элеме ИЛИ 18 подается на счетчик 11 блокировки и на датчик 6 служебных команд а также через первый элемент И 14 на вход первого элемента 15 задержки Продвижение единиьц по первому элем 4Z ту 15 задержки осуществляется цикловой частотой fц. Сигнал с второго выхода счетчика 11 блокировки блокирует прием п комбинаций в выходной накопитель 12. Датчик 6 служебных команд записьшает комбинацию Запрос во входной накопитель 1 и включает счетчик 7 блокировки, сигнал с первого выхода которого обеспечивает считывание п комбинаций из блока 4 памяти, через перек лючатель 2 вслед за комбинацией Запрос. При приеме комбинации Запрос которая выделяется с помощью дешифратора 8 служебных команд, сигнал с последнего подается на счетчик 11 блокировки. В результате этого при приеме комбинации Запрос осуществляется блокировка выходного накопителя 12 и в канал связи посылается Запрос и п комбинаций из блока 4 памяти. При обнаружении ошибки сигнал из декодера 10 через первый элемент ИЛИ 18 и первый элемент И 14 поступаI-ет также на вход первого и второго элементов 15 и 16 задержки, а через i элемент ИЛИ 19 - на вход третьего элемента 21 задержки. Второй элемент 16 задержки задерживает сигнал на п тактов ; цикловой частоты, а третий элемент 21 задержки - на п-1 такт цикловой частоты, t Через один такт после записи единицы на вход второго элемента 16 задержки и на вход первого элемента 15 задержки второй триггер 20 сигналом первого элемента 15 задержки переводится в положение, при котором с его выхода не поступает потенциал на первый вход первого элемента И 14. В результате этого запрещается прохождение сигнала Ошибка с выхода первого элемента ИЛИ 18 через первый элемент И 14. За один цикл .до снятия блокировки с выходного накопителя 12 на выходе третьего элемента 21 задержки появляется импульс. Если в это время декодер 10 обнаружит ошибку в принимаемой информации, то сигнал Ошибка с его выхода че- рез первый элемент РШИ 18, второй элемент И 22 поступит на первый вход первого триггера 17, которьй разрешит прохождение сигнала с выхода второго элемента 16 задержки через третий элемент И 23 на вход первого элемента ИЛИ 18. Если даже, после разблокировки выходного накопителя 12 ошибка в пр нимаемой информации не обнаружена, прием информации снова заблокируетс аппаратура переведется в очередной цикл запроса и на вход второго элемента 16 задержки запишется единица Поскольку выход третьего элемента 2 задержки замкнут через второй элемент ИЛИ 19 с его выходом, то в трет ем элементе 21 задержки во втором цикле запроса циркулируют друг за другом две следующие единицы и, следовательно, в этом цикле проверя ются на наличие ошибки два знака, предшествующие разблокировке выход ,ного накопителя 12, Эта проверка происходит аналогично описанному, т.е. при обнаружении ошибок в одном или обоих знаках, предшествующих разблокировке, сигнал Ошибка из декодера 10 через первый элемент J-ШИ 18 и второй элемент И 22 переведет первый триггер 17 в состояние, разрешающее передачу сигнала С выхода второго элемента 16 задер ки через третий элемент И 23 на вхо первого элемента ИЛИ 18 и далее на вход счетчика 1t блокировки и на вход датчика 6. Аппаратура переведется g очередной цикл запроса и повторения, в третий элемент 21 задер1(ки записывается третья единица. В следующем цикле запроса на на личие ошибки проверяется уже четыре комбинации, предшествующие разблоки ровке выходного накопителя 12. Число единиц в третьем элементе 21 задержки увеличивается с каждым циклом запроса, пока этот элемент заде жки не заполнится полностью, после чего проверке подвергаются все знаки, поступающие на прием во время блокировки выходного накопителя 12. Если в течение цикла запроса ошибки в принимаемой информации не обнаружены, то сигналы с выхода третьего элемента 21 задержки на вход первого триггера 17 через второй элемент И 22 не поступают. Вследствие этого первьй триггер 1 7 останется в состоянии, разрешающем прохождение сигнала с выхода второго элемента 16 задержки через четвертый элемент И 24 для стирания сигналов в третьем элементе 21 задержки. В этом случае в момент поступления импульса с выхода второго элемента 16 задержки устройство переводится в исходное состояние, при котором запрос корреспонденту посьитается при очередном обнаружении ошибки в принимаемой информации. Формула изобретения Устройство защиты от ошибок, содержащее на передающей стороне последовательно соединенные входной на- : копитель, переключатель и кодер, при этом информационный вход входного накопителя- обьединен с первым входом блока памяти,.к второму входу которого подключен второй выход переключателя, а также датчик служебных команд, первый, второй и третий выходы которого подключены соответственно к входу датчика сигналов обмена, второму входу входного накопителя и к входу счетчика блокировки, первый и второй выходы которого подктпочены к соответствующим входам переключателя и блока памяти, на приемной стороне объединенные по входу декодер и входной накопителе , первьй и второй выходы которого подключены соответственно к входу дешифратора служебных команд и к первому входу выходного накопителя, выход которого подключен к первому входу датчика сигналов обмена, к второму входу которого подключен первый выход счетчика блокировки, второй выход которого подключен к второму входу выходного накопителя, а также первый элемент ИЛИ, отличающееся тем, что, с целью поддержания достоверности при ухудшении качества канала, на приемной стороне введены второй элемент ИЛИ, первьй, второй, третий и четвертьй элементы И, первьй и второй триггеры,первьй, второй, третий и четвертьй элементы задержки, при этом выход декодера подключен к первому входу первого элемента ИЛИ, выход которого подключен к первому входу счетчика блокировки и первым входам первого и второго элементов И, выход первого элемента И подключен к входам первого и второго элементов задержки и к первому входу второго элемента ИЛИ, выход которого подключен к первому входу третьего элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ и второму входу втоSрого элемента И, выход которого подключен к первому входу первого триг гера, первый и второй выходы которого подключены соответственно к первым входам третьего и четвертого элементов И, выход третьего элемента И подключен к второму входу перво го элемента ИЛИ и к входу четвертого элемента задержки, выход которого подключен к второму входу первого триггера выход первого элемента задержки подключен к первому входу второго триггера, к второму входу которого и к вторым входам третьего и четвертого элементов И подключен 146 выход второго элемента задержки, выход четвертого элемента И подключен к второму входу третьего элемента задержки, а выход второго триггера подключен к второму входу первого элемента И,причем выход дешифратора служебных команд подключен к второму входу счетчика блокировки и к первому входу датчика служебных команд, к второму входу которого подключен выход первого элемента ИЛИ, при этом вторые входы второго и треты его элементов частоты задержки имеют объединенные входы опорной частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Устройство защиты от ошибок | 1984 |

|

SU1197115A1 |

| Устройство для передачи и приема информации | 1985 |

|

SU1338089A1 |

| Устройство для согласования потоков информации | 1983 |

|

SU1107320A1 |

| Устройство для регистрации и передачи информации | 1976 |

|

SU658592A1 |

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| Устройство для защиты от ошибок | 1972 |

|

SU503276A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1984 |

|

SU1197114A1 |

Изобретение относится к технике связи. Цель изобретения - поддержание достоверности при ухудшении качества канала. Устройство содержит на передающей стороне: входной накопитель 1, переключатель 2, кодер 3, блок 4 памяти, датчик 5 сигналов обмена, датчик 6 служебных команд и счетчик 7 блокировки, а на приемной стороне: дешифратор 8 служебных команд, входной накопитель 9, декодер 10, счетчик 11 блокировки, выходной накопитель (ВН) 12, датчик 13 сигналов обмена, четыре элемента И 14, 22, 23 и 24, четыре элемента задержки

| Шляпоберский В.И | |||

| Основы техники передачи сообщений | |||

| М.: Связь, 1973, с | |||

| Уровень с пузырьком | 1922 |

|

SU388A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-11-23—Публикация

1983-12-20—Подача