1

Изобретение относится к радиотехнике и может быть использовано в системах передачи дискретной информации с решающей обратной связью.

Известно устройство обнаружения и исправления вставок и выпгщений информации, содержащее выходной накопитель, первый элемент ИЛИ, блок сравнения, последовательно соединенные переключатель и дополнительный накопитель, а также последовательно соединенные входной накопитель, блок обнаружения ошибок и блок управления, к второму входу которого подключен выход дешифратора комбинации Запрос, а первый и второй выходы блока управления подключены ко входу переключателя и первому входу выходного накопителя 1.

Однако известное устройство обладает низкой скоростью передачи информации в системе.

Цель изобретения - повышение достоверности и скорости передачи информаДии.

Для этого в ycTpo+icTBO обнаружения и исправления вставок и выпадений информации, содержащее выходной аакопитель, первый элемент ИЛИ, блок

сравнения, последовательно соединенные переключатель и дополнительный накопитель, а также последовательно соединенные входной накопитель, блок обнаружения ошибок и блок управления, к второму входу которого подключен выход дешифратора комбинаций Запрос, а первый и второй выходы блока управления подключены ко входу

10 переключателя н первому входу выходного накопителя, введены второй элемент ИЛИ, блок сброса и датчик комбинации Пробел, ко входу которого подключен выход блока обнаружения

15 ошибок, а выход датчика Пробел подключен к первому входу входного накбпителя, к BTOpoiviy входу которого подключен выход переключателя,при этом первые выходы входного и испол20нительного накопителей через первый элемент ИЛИ подключены ко входу дешифратора комбинации Запрос и первому входу блока сравнения, к второму входу которого и второму входу

25 выходного накопителя через второй элемент ИЛИ подключены вторые выходы входного и дополнительного .накопителей, а выход блока сравнения подключен к третьему входу блока управления, первый и третий выходы которого подключены ко входам блока сброса, выход которого подключен к третьему входу входного накопителя и второму входу дополнительного накопителя.

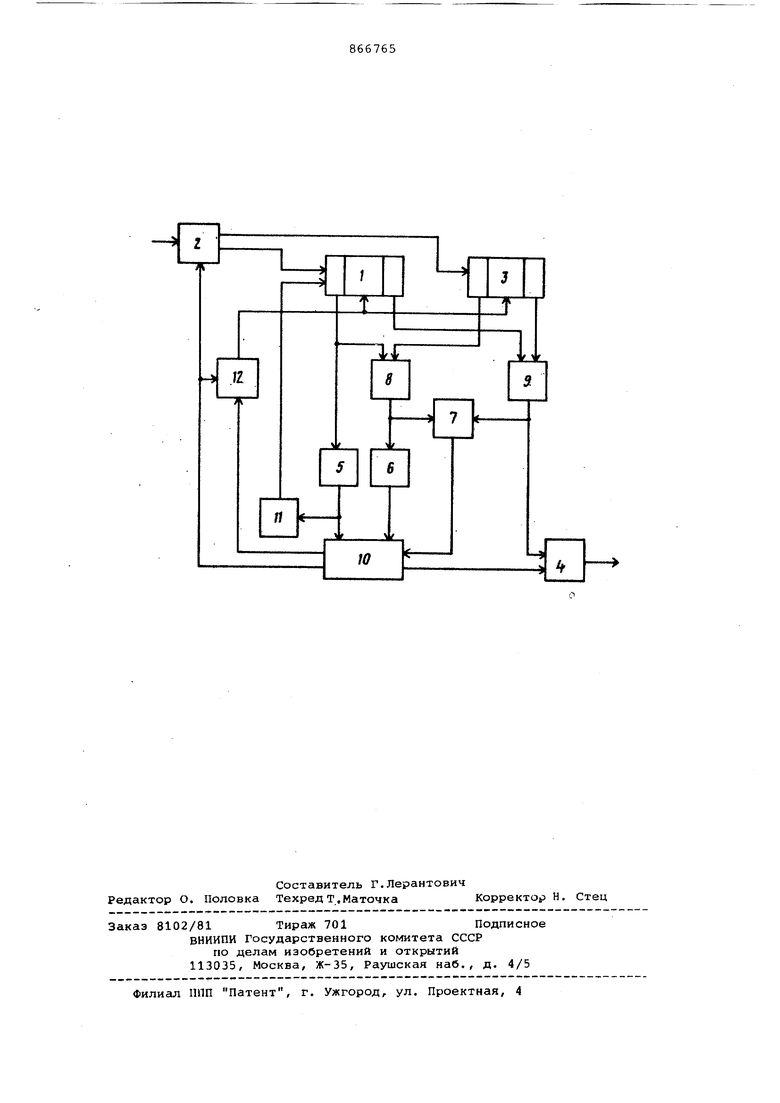

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство содержит входной накопитель 1, переключатель 2, дополнительный накопитель 3, выходной накопитель 4, блок 5 обнаружения ошибок, дешифратор 6 комбинации Запрос блок 7 сравнения, первый элемент ИЛИ 8, второй элемент ИЛИ 9, блок 10 управления, датчик 11 комбинации Пробел, блок 12 сброса.

Устройство работает следующим об.разом.

Принимаемые кодовые комбинации через переключатель 2 по мере поступления записываются во входной накопитель 1. С выхода первого разряда комбинации поступают на блок 5 обнаружения ошибок и через первый элемент ИЛИ 8 - на первый вход блока 7 сравнения и дешифратор 6 комбинации Запрос. Комбинации с выхода последнего разряда входного .накопителя 1 через второй элемент ИЛИ 9 поступают на второй вход блока 7 сравнения и в выходной накопитель 4. Одновременно блок 7 сравнения осущуствляет попарное сравнение принимаемых комбинаций,записываемых в первый и последний разряды входного накопи теля 1, на заданное число совпадений подряд (Z).Емкости входного 1 и дополнительного 3 накопителей одинаковы и выбраны равными (h + 2), где h - емкость буферного ,накопителя передачи на противоположной станции. Такая емкость входного 1 и дополнительного 3 накопителей обеспечивает поступление на первый и второй входы блока 7 сравнения принимаемых комбинаций, сдвинутых по времени на цикл повторения . системы с решающей обратной связью (h + ОСц, где длительность кодовой комбинации. Порог срабатывания блока 7 сравнения выбирается из условия Z h -1, при этом с него на блок 10 управления с вероятностью, близко к единице, сигнал поступает лишь в случае искажений в канале связи и на личи повторений информации в системе Ci решающей обратной связью.

При отсутствии искажений в канале связи блок 10 управления выдает сигнал в выходной накопитель 4,разрешающий считывание принятых и записанных в нем комбинаций потребителю. При искажении в канале связи неразрешенная комбинация поступит в первый разряд входного накопителя 1 и будет обнаружена блоком 5 обнаружения ошибок как ошибка. Блок 5 обнаружения ошибок выдает сигнал на .блок 10 управления и датчик 11 комбинации Пробел. По принятому алгоритму работы аппаратуры с решающей обратной связью в этом случае на противоположную станцию будут переданы комбинация Запрос и h комбинаций из буферного накопителя, по которому та станция также передает комбинацию Запрос и повторит h ранее переданных комбинаций.

По сигналу с блока 5 обнаружения ошибок на втором выходе блока 10 управления на время цикла блокировки появится напряжение, которое,поступив на переключатель, обеспечит отключение на это время от приемного канала входного накопителя 1 и подключение дополнительного накопителя 3. Кроме того, это напряжение подготовит к срабатыванию блок 12 сброса.

Одновременно датчик 11 комбинации Пробел осуществит запись на месте принятой ошибки комбинации Пробел. Во время цикла блокировки также происходит сравнение комбинаций, поступающих на блок 7 сравнения с выхода первого разряда дополнительного накопителя 3 и последнего разряда входного накопителя 1 через первый и второй элементы ИЛИ 8 и 9 соответственно.

Если за время блокировки в дополнительный накопитель 3 поступит комбинация Запрос, то она с выхода первого разряда через первый элемент ИЛИ 8 поступит на дешифратор б комбинации Запрос и последний выдает сигнал на блок 10 управления. При первом выходе блока 10 управления появится сигнал и поступит на блок 12 сброса, который произведет в момент окончания блокировки стирание информации из входного и дополнительного накопителей 1 и 3. При выбранной емкости входного и дополнительного накопителей 1 и 3 к моменту окончания,-блокировки комбинация Пробел, записанная во входной накопитель 1, будет переписана в предпоследний разряд. После окончания блокировки напряжение на втором выходе блока 10 управления снимается я переключатель 2 осуществит обратную коммутацию, т.е. отключение от приемного канала дополнительного накопителя 3 и подключение к нему входного накопителя 1. Поступающая во входной накопитель 1 после окончания блокировки повторяемая комбинация является той комбинацией, которая ранее была искажена в канале связи,

Если за время блокировки в дополнительный накопитель 3 комбинация Запрос не поступит, а блок 7 сравнения обнаружит Z совпадений подряд, то это будет свидетельствовать о том что посылаемый с противоположной станции Запрос исказился в канале связи. В этом случае с блока 7 сравнения в блок 10 управления поступит

сигнал, по которому в конце цикла блокировки блок 12 сброса произведет стирание информации из входного и дополнительного накопителей 1 и 3.

Таким образом, предлагаемое устроиство сохраняет принятый алгоритм работы системы с решающей обратной связью. .

Если после обнаружения ошибки за время блокировки блок 7 сравнения не выявит Z совпадений подряд, а в принимаемой информации будет отсутствовать комбинация Запрос, то это - явится свидетельством того, что посланный на противоположную станцию Запрос трансформировался в канале связи в разрешенную комбинацию и имеет место выпадение информации. Поскольку в предлагаемом устройстве принимаемые во время блокировки комбинации записываются в дополнительный накопитель 3, то выпадение их исключается, а этом случае на блок 12 сброса с первого выхода блока 10 управления никакого сигнала не поступит и он, в свою очередь, не произведет стирание информации из входного и дополнительного накопителей 1 и 3. При этом по окончании блокировки принимаемые комбинации начнут поступать в освободившийся входной нако.питель 1, а записанные во время блокировки в дополнительный накопитель 3 комбинации через второй элемент ИЛИ 9 будут поступать в выходной накопитель 4..

Если в принимаемой информации отсутствуют ошибки и комбинации Запрос, а блок 7 сравнения обнаружит Z совпадений подряд, то это будет признаком того, что комбинация Запрос, переданная противоположной станцией, трансформировалась в канале связи в разрешгиощую комбинацию и, тем саь«лм, имеет место вставка информации. При этом блок 7 сравнения вьадает сигнал на блок 10 управления и на первом выходе последнего появится импульс, воздействующий на блок 12 сброса,который произведет стирание информации из входного накопителя 1, в котором записаны повторяемые комбинации.Этим исключается вставка информации.

Использование предлагаемого устройства в аппаратуре систем передачи дискретной информации с решающей обратной связью позволяет обнаруживать и исправлять вставки и выпгщения информации на той станции, где эти явления имеют место. Как показывают расчеты, исключение необходимости обмена сигналами о наличии вставок и выпадений и необходимости повторной передачи информации для ее исправления увеличивает скорость передачи на 6-10%.

Формула изобретения

(О

Устройство обнаружения и исправления вставок и выпадений информации, содержаидее выходной накопитель, первый элемент ИЛИ, блок сравнения,последовательно соединенные переключатель и дополнительный накопитель, а также последовательно соединенные ВХОДНОЙ накопитель, блок обнаружения ошибок и блок управления, к второму

входу которого подключен выход дешифратора комбинаций Запрос, а первый и второй выходы блока управления подключены ко входу переключателя и первому входу выходного накопителя,

отличающееся тем, что, с целью повышения достоверности, и скорости передачи информации, введены второй элемент ИЛИ, блок сброса и датчик комбинации Пробел, ко входу которого подключен выход блока обнаружения ошибок, а выход датчика комбинации Пробел подключен к первому входу входного накопителя, к второму входу которого подключен выход переключателя, при этом первые выходы входного и дополнительного накопителей через первый элемент ИЛИ подключены ко входу дешифратора комбинации Запрос и первому входу блока сравнения, к второму входу которого

0 и второму входу выходного накопителя через второй элемент ИЛИ подключены вторые выходе входного и дополнительного накопителей, а выход блока сравнения подключен к третьему входу бло- ка управления, первый и третий выходы которого подключены ко входам блока сброса, выход которого подключен к третьему входу входного накопителя и второму входу дополнительного накопителя.

Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 468381, кл. Н 04 L 1/16, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Устройство для регистрации и передачи информации | 1976 |

|

SU658592A1 |

| Устройство обнаружения вставок и выпадений информации в системах передачи данных с решающей обратной связью | 1971 |

|

SU468381A1 |

| Устройство защиты от ошибок | 1983 |

|

SU1272514A1 |

| Телеграфное устройство для исключения обнаруженных ошибок | 1979 |

|

SU773941A2 |

| Телеграфное устройство для исключения обнаруженных ошибок | 1976 |

|

SU660286A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Телеграфное устройство для исключения обнаруженных ошибок | 1975 |

|

SU562932A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

Авторы

Даты

1981-09-23—Публикация

1979-12-21—Подача