1338089

блок 2 переключения, блок 3 кодирования, буферный накопитель 4, распределитель 5, блок 6 управления, задающий г-р 7, эл-т ИЛИ 8, блок 9 эл-тов И, блок 10 делителей частоты, на приемной стороне - реверсивный

1

Изобретение относится к электросвязи и может использоваться в телеграфии.

Целью изобретения является повышение пропускной способности уст ройства путем обеспечения возможности переключения скорости передачи и приема информации при изменении качества канала.

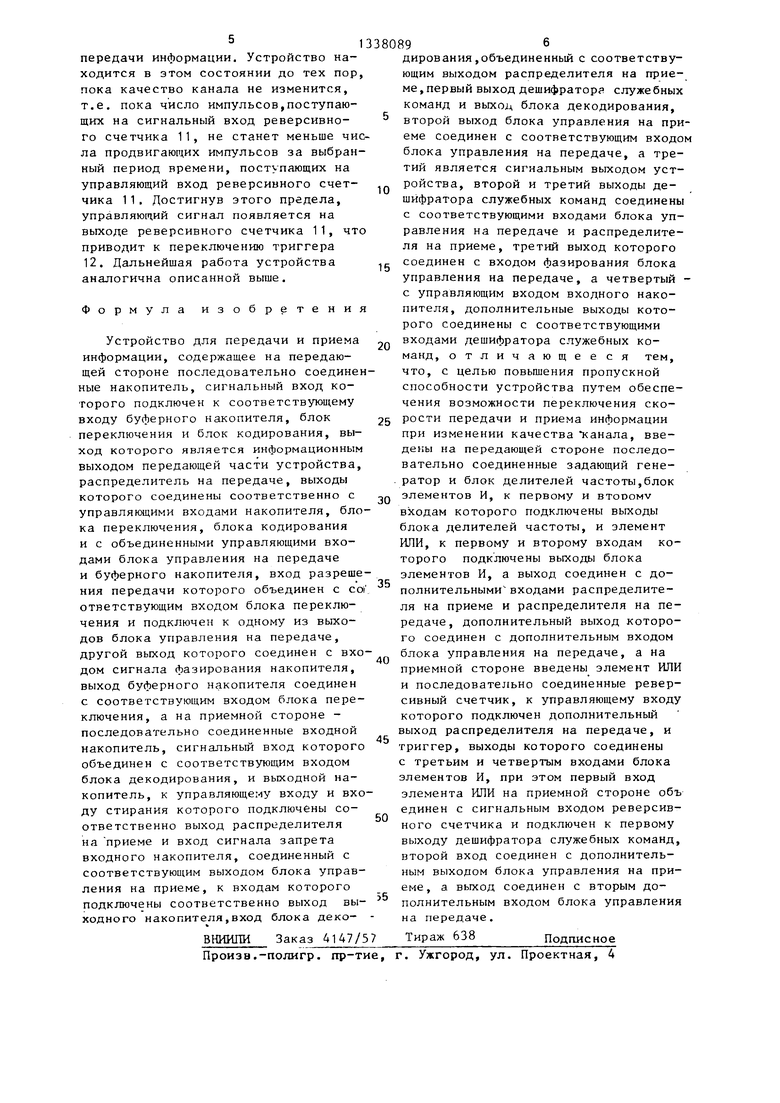

На чертеже изображена структурна электрическая схема устройства для передачи и приема информации.

Устройство для передачи и приема информации содержит на передающей стороне накопитель 1, блок 2 переключения, блок 3 кодирования, буфеный накопитель 4, распределитель 5 на передаче,блок 6 управления на передаче, задающий генератор 7, элемент ИЛИ 8, блок 9 элементов И,блок 10 делителей частоты, на приемной стороне - реверсивный счетчик 11, триггер 12, входной накопитель 13, выходной накопитель 14, блок 15 декодирования, дешифратор 16 служебны команд, распределитель 17 на приеме блок 18 управления на приеме, элемент ИЛИ 19.

Блок 6 управления на передаче со держит датчик 20 служебных комбинаций, датчик 21 команд, счетчик 22 блокировки; блок 9 элементов И содержит первый 23 и второй 24 элементы И; блок 10 делителей частоты содержит первый 25 и второй 26 делители частоты; блок 18 управления на приеме содержит счетчик 27 ошибки, счетчик 28 блокировки и датчик 29 сигналов.

Устройство для передачи и приема информации работает следующим образом.

В исходном состоянии управляющий сигнал с выхода триггера 12 воздейсчетчик 11, триггер 12, входной 13 и выходной 14 накопители, блок 15 декодирования, дешифратор 16 служебных команд, распределитель 17, блок 18 управления, эл-т ИЛИ 19.1 ил.

ствует на вход элемента И 24 блока 9. Вследствие этого продвигающие импульсы от задающего генератора 7

через делитель 25 блока 10, другой вход элемента И 24 блока 9, элемент ИЛИ В поступают на вход распределителя 5 на передаче и вход распределителя 17 на приеме. Управляющие импульсьг с выходов распределителя 5 поступают соответственно на входы накопителя 1, буферного накопителя 4, блока 6 управления на передаче, блока 3 кодирования, блока 2 переклю.чения ц реверсивного счетчика 11. Управляющие импульсы с выходов распределителя 17 поступают соответственно на входы блоков 15 и 18, входного накопителя 13, блока 6 и выходного накопителя 14.

До начала работы устройства в режиме передачи и приема информации производится фазирование: на инициирующей станции датчик 21 команд

блока 6 формирует команду Фаза 1, которая поступает ла вход накопителя 1 и - через блок 2 переключения, блок 3 кодирования по каналу связи - на противоположную станцию, а

с нее - на.вход входного накопителя 13 и через его выходы на дешифратор 16 служебных команд. В результате на выходе дешифратора 16 появляется сигнал, который поступает

на вход распределителя 17, осуществляя его фазирование. По завершении фазирования с выхода распределителя 17 управляющий сигнал поступает на вход датчика 21 команд блока 6. По

этому сигналу датчик 21 формирует команду Фаза 2, которая поступает через накопитель 1, блок 2, блок 3 по каналу связи на инициирующую станцию, а с нее - на вход накопителя

13 и далее на дешифратор 16. R ре3133

зультате на выходе дешифратора 16 пог является управляющий сигнал, который поступает на вход датчика 21 блока 6, что приводит к прекращению выдачи датчиком 21 команды Фаза 1, Процесс фазирования в одном направлении заканчивается. Фазирование в ппотиво- положном направлении осуществляется аналогично.

После завершения процесса фазирования с выхода датчика 20 блока 6 выдается сигнал о готовности устройства к передаче.

Информация, поступающая от источ

ника, записывается в накопитель 1 и буферный накопитель 4. Затем в моменты времени, определяемые распределителем 5, информация в виде К-раз- рядных кодовых комбинаций через блок 2 переключения подается в блок 3 кодирования, где перекодируется, а затем передается в канал связи. Принятая комбинация поступает во входной накопитель 13 и параллельно в блок 15 декодирования. При отсутстви ошибок в принятой комбинации по сигналу, поступающему на вход входного накопителя 13 с распределителя 17, комбинация переписывается в выходной накопитель 14. С его выхода на вход датчика 29 блока 18 выдается сигнал, который с выхода датчика 29 через выход блока 18 поступает к получателю информации, сигнализируя о готовности выдать информацию, что производится подачей управляющего сигнала на вход выходного накопителя 14.

При искажении принимаемой комбинации на выходе блока 15 появляется сигнал, который через блок 18 управления проходит на вход счетчика 28, счетчика 27 ошибок и через элемент ИЛИ 19 - на вход датчика 21 команд блока 6. В результате на выходах счетчика 28 появляется управляющий сигнал, под действием которого закрывается на М циклов выходной накопитель 13 и стирается информация в выходном накопителе 14.

Под действием сигнала с другого выхода счетчика 28 происходит блокировка выдачи сигнала готовности получателю.

По сигналу, поступившему на вход датчика 21 команд, происходит срабатывание, в результате чего с выхода 21 команд поступает комбинапия Запрос на вход нако

пителя 1, которая затем передается в канал связи, а с другого выхода датчика 21 команд выдается сигнал на вход счетчика 22 блокировки. С выхода счетчика 22 сигнал поступает на вход буферного накопителя 4 и блока 2 переключения, разрешая передачу в канал связи вслед за командой Запрос всех комбинаций, хранящихся в буферном накопителе. При приеме комбинации Запрос противоположной станцией на выходе депшфра- тора 16 появляется сигнал, поступаю- щий на входы счетчика 28. ре версивно- го счетчика 11 и элемента ИЛИ 19. В результате счетчик 28 прекращает выдачу управляющих сигналов.

Под действием сигнала, поступающего через вход элемента ИЛИ 19 на вход датчика 21 команд, на передающую станцию передается комбинация Запрос, в результате чего начинается повторная передача информации из буферн ого накопителя 4. После, этого устройство возвращается в режим нормальной работы.

При потере синфазности с выхода 15 декодирования с частотой циклов поступает сигнал Ошибка. Когда число этих сигналов превысит га, на выходе счетчика 27 ошибок появится сигнал, поступающий на вход датчика 21 команд блока 6 и вызывающий

5

0

5

0

5

передачу в канал связи команды Фа-/ за 1, по которой процесс фазирования, описанный выше, повторяется.

Если качество канала связи ухудшается, передаваемая комбинация подвергается искажениям, что приводит к формированию команды Запрос и повторению передаваемых комбинаций. Когда число сигналов, соответствующих приему команды Запрос с выхода дешифратора 16 служебных команд, поступающих на вход реверсивного счетчика 11, за определенный период времени превысит установленное число продвигающих импульсов, поступав ющих на вход реверсивного счетчика 11, управляющий сигнал появляется на другом выходе реверсивного счетчика 11. Триггер 12 под воздействием этого сигнала переключается, и на вход распределителей 5 и 17 поступают продвигающие импульсы с выхода второго делителя 26 частоты, имеющего больший коэффициент деления, т.е. происходит сн1Ежение скорости

передачи информации. Устройство находится в этом состоянии до тех пор, пока качество канала не изменится, т.е. пока число импульсов,поступающих на сигнальный вход реверсивного счетчика 11, не станет меньше числа продвигающих импульсов за выбранный период времени, поступающих на управляющий вход реверсивного счетчика 11, Достигнув этого предела, управляющий сигнал появляется на выходе реверсивного счетчика 11, что приводит к переключению триггера 12. Дальнейшая работа устройства аналогична описанной выше.

Формула изобретения

Устройство для передачи и приема информации, содержащее на передающей стороне последовательно соединенные накопитель, сигнальный вход которого подключен к соответствующему входу буферного накопителя, блок переключения и блок кодирования, выход которого является информационным выходом передающей части устройства, распределитель на передаче, выходы которого соединены соответственно с управляющими входами накопителя, блока переключения, блока кодирования и с объединенными управляющими входами блока управления на передаче и буферного накопителя, вход разрешения передачи которого объединен с cot ответствующим входом блока переключения и подключен к одному из выходов блока управления на передаче, другой выход которого соединен с входом сигнала фазирования накопителя, выход буферного накопителя соединен с соответствующим входом блока переключения, а на приемной стороне - последовательно соединенные входной накопитель, сигнальный вход которого объединен с соответствующим входом блока декодирования, и выходной накопитель, к управляющему входу и входу стирания которого подключены соответственно выход распределителя на приеме и вход сигнала запрета входного накопителя, соединенный с соответствующим выходом блока управления на приеме, к входам которого подключены соответственно выход выходного накопителя,вход блока деко- ВНИИПИ Заказ 4147/5

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

0

5

0

5

0

5

0

5

0

5

дарования,объединенный с соответствующим выходом распределителя на приеме , первый выход дешифратора служебных команд и выходу блока декодирования, второй выход блока управления на приеме соединен с соответствующим входом блока управления на передаче, а третий является сигнальным выходом устройства, второй и третий выходы дешифратора служебных команд соединены с соответствующими входами блока управления на передаче и распределителя на приеме, третий выход которого соединен с входом фазирования блока управления на передаче, а четвертый - с управляющим входом входного накопителя, дополнительные выходы которого соединены с соответствующими входами дешифратора служебных команд, отличающееся тем, что, с целью повышения пропускной способности устройства путем обеспечения возможности переключения скорости передачи и приема информации при изменении качества канала, введены на передающей стороне последовательно соединенные задающий генератор и блок делителей частоты,блок элементов И, к первому и BTODOMV входам которого подключены выходы блока делителей частоты, и элемент ИЛИ, к первому и второму входам которого подключены выходы блока элементов И, а выход соединен с дополнительными входами распределителя на приеме и распределителя на передаче, дополнительный выход которого соединен с дополнительным входом блока управления на передаче, а на приемной стороне введены элемент ИЛИ и последовательно соединенные реверсивный счетчик, к управляющему входу которого подключен дополнительный выход распределителя на передаче, и триггер, выходы которого соединены с третьим и четвертым входами блока элементов И, при этом первый вход элемента ИЛИ на приемной стороне объ единен с сигнальным входом реверсивного счетчика и подключен к первому выходу дешифратора служебных команд, второй вход соединен с дополнительным выходом блока управления на приеме, а выход соединен с вторым дополнительным входом блока управления на передаче.

Тираж 638 Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| Устройство защиты от ошибок | 1984 |

|

SU1197115A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1693732A1 |

| Устройство для приема команд телеуправления | 1981 |

|

SU991473A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2012149C1 |

| Устройство защиты от ошибок с решающей обратной связью | 1980 |

|

SU866766A1 |

| Устройство приема и передачи для систем с решающей обратной связью | 1984 |

|

SU1241484A1 |

| Устройство статистического кодирования и декодирования факсимильных сигналов | 1981 |

|

SU1040623A1 |

Изобретение относится к электросвязи и повышает пропускную способность устр-ва путем обеспечения возможности переключения скорости передачи и приема информации при изменении качества канала. Устр-во содержит на передающей стороне накопитель 1, (Л со со 00 о 00 со

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений | |||

| М.: Связь, 1973 г., с.398,фиг.7, 10. |

Авторы

Даты

1987-09-15—Публикация

1985-05-16—Подача