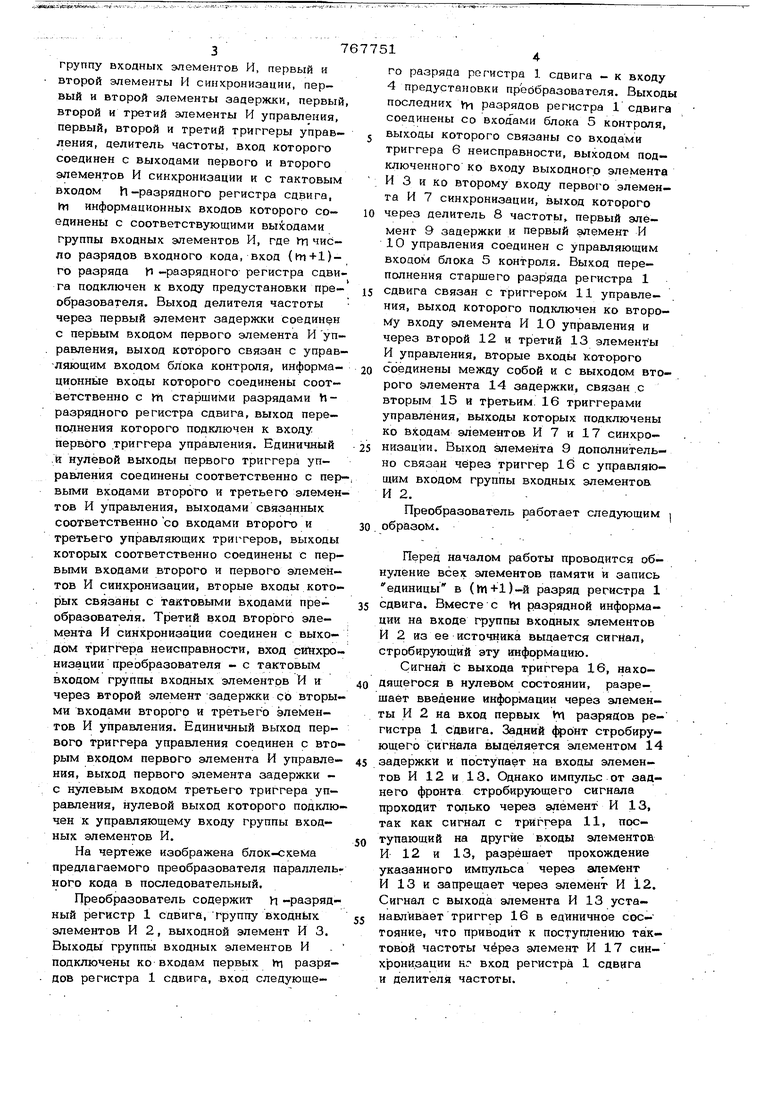

Изобретение относится к области ав--. тематики и вычислительной текники и может быть использовано при построении преобразователей последовательности параллельных кодов в последовательный код. Известен преобразователь параллельного кода в последовательный, содержащий сдвиговый регистр, выходной элемент И, входные элементы И и блок управления ll. Недостатки этого преобразователя сос тоят в низкой достоверности результатов преобразования, связанной с отсутствием блоков контроля, и невозможности преобразования последовательности входных чисел. Наиболее близким к изобретению по технической сущности и схемному построению является I преобразователь парал- лельно1 о кода в последовательный, содержащий Ц -разрядный регистр сдвига, где п - число разрядов выходного кода, выходной элемент И, первый вход KOTOрого соединен с выходом старшего разряда и -разрядного регистра сдвига, блок контроля, триггер неисправности, входы которого соединены с выходами блока контроля, а выход триггера неисправности связан со вторым входом выходного элемента И 2 Недостаток этого преобразователя заключается в относительно низкой надежности преобразования. Цель изобретения - уйеличение надежности преобразования, Для этого преобразователь параллельного кода в последовательный, содержащий П -разрядный регистр сдвига, где -число разрядов выходного кода, выходкой элемент И, первый вход которого соединен с выходом старшего разряда П -разрядного регистра сдвига, блок контроля, триггер неисправности, входы которого соединены с выходами блока контроля, а единичный выход триггера неисправности связан со вторым входом выходного элемента И, дополнительно содержит 37 группу входных элементов И, первый и второй элементы И синхронизации, первый и второй элементы задержки, первый второй и третий элементы И управления, первый, второй и третий триггеры управления, целитель частоты, вход которого соединен с выходами первого и второго элементов И синхронизации и с тактовым входом h -разрядного регистра сдвига, m информационных входов которого соединены с соответствующими выходами группы входных элементов И, где п число разрядов входного кода, вход {ш+1)го разряда П -разрядного регистра сдвига подключен к входу предустановки преобразователя. Выход делителя частоты череа первый элемент задержки соединен с первым входом первого элемента Иуправления, выход которого связан с управляющим входом блока контроля, информационные входы которого соединены соответственно с m старшими разрядами Празрядного регистра сдвига, выход переполнения которого подключен к входу первого триггера управления. Единичный .и нулевой выходы первого триггера управления соединены соответственно с пер выми входами второго и третьего элемен тов И управления, выходами связанных соответственно со входами второго и третьего управляющих триггеров, выходы которых соответственно соединены с первыми входами второго и первого элементов И синхронизации, вторые входы которых связаны с тактовыми входами преобразователя. Третий вход второго элемента И синхронизации Соединен с выходом триггера неисправности, вход сийхронизации преобразователя - с тактовым входом группы входных элементов И и через второй элемент задержки с6 вторыми входами второго и третьего элементов И управления. Единичный выход первого триггера управления соединен с вторым входом первого элемента И управле- ния, выход первого элемента задержки с нулевым входом третьего триггера управления, нулевой выход которого подклю чен к управляющему входу группы входнык элементов И. На чертеже изображена блок-схема предлагаемого преобразователя параллель ного кода в последовательный. Преобразователь содержит Yi -разрядный регистр 1 сдвига, труппу входнЬгх элементов И 2, выходной элемент И 3. Выходы группы входных элементов И . подключены ко входам первых iri разрядов регистра 1 сдвига, вход следующе- 1 го разряда регистра 1 сдвига - к входу 4 предустановки преобразователя. Выходы последних 1и разрядов регистра 1 сдвига соединены со входами блока 5 контроля, выходы которого связаны со входами триггера 6 неисправности, выходом подключенного ко входу выходного элемента И 3 и ко второму входу первого элемента И 7 синхронизации, выход которого через делитель 8 частоты,, первый элемент 9 задержки и первый элемент И 10 управления соединен с управляющим входом блока 5 контроля. Выход переполнения старшего разряда регистра 1 сдвига связан с триггером 11 управления, выход которого подключен ко второму входу элемента И 10 управления и через второй 12 и третий 13 элементы И управления, вторые входы которого соединены между собой и с выходом второго &лемента 14 задержки, связан с вторым 15 и т|эетьим. 16 триггерами управления, выходы которых подключены ко Входам элементов И 7 и 17 синхронизации. Выход апемейта 9 дополнительно связан через триггер 16с управляющим входом группы входных элементов Преобразователь работает следующим i образом. Перед началом работы проводится обнуление всех элементов памяти и запись единицы в (|11+1)-й разряд регистра 1 сдвига. Вместе с in разрядной информации на входе группы входных элементов И 2 нз ее источника выдается сигнал, стробирующИй эту информацию. Сигнал С выхода триггера 16, находящегося в нулевом состоянии, разрешает введение информации через элементы И 2 на вход первых Wi разрядов регистра 1 сдвига. Задний (|рЬнт стробирующего сигнала выделяется элементом 14 задержки и поступает на входы элемен- тов И 12 и 13. Однако импульс от ааднего фронта стробирующего сигнала проходит только через элемент И 13, так как сигнал с триггера 11, поступающий на другие входы элементов И 12 и 13, разрешает прохождение указанного импульса через элемент И 13 и запрещает через элемент И 12. Сигнал с выхода элемента И 13 устанавливает триггер 16 в единичное состояние, что приводит к поступлению тактовой частоты через элемент И 17 синхронизации КС вход регистра 1 сдвига и делителя частоты. В том случае, если псх тугшение параллельного кода на входы группы входных элементов И 2 производится с частотой ,| 7mf,, где 2. частота передачи последовательной кодограммы или если пауза между поступлением последнего блока информации на входы элементов И 2 и выдачей всей кодограм мы в последовательном виде должна быть минимальной., то на вход элемента И 17 должна подаваться соответственно более высокая частота тактовых импульсов, чем на вход элемента И 7. Если же ограничения отсутствуют, то частота тактовых импульсов на входах элементов И 7 и 17 может быть одна и та же. После поступления hi импульсов информация, записанная в ш первых разряда и единица, записанная в (vn+1)- и раз 1 сдвига, оказываются про ряд регистра винутыми на 1 разрядов. Импульс же переполнения с выхода делителя 8 часто ты поступает через элемент 9 задержки на нулевой вход триггера 16, Изменение состояния триггера 16 прекратит поступление тактовой частоты через элемент И 17, и преобразователь будет подготовлен к приему следующего блока информации из Vri разрядов. Боле раннее введение этой информации будет запрещено отсутствием разрешающего сигнал с выхода триггера 16 на вход группы входных элементов И 2. Следующий цикл приема In разрядов информации аналогичен описанному. Поступление предпоследнего Vn -раз рядного блока информации и сцвиг его на уп разрядов регистра 1 приводит к появлению на выходе переполнения старшего разряда регистра 1 единицы, записанной во время предустановки в (|ти-1)-й разряд регистра 1. Этот сигнал изменяет состояние триггера 11, сигнал с выхода которого.разрешает поступление импульсов переполнения с выхода делителя 8 через элемент И Ю на вход блока 5 контроля, разрешает поступление последнего строба через элемент И 12 на вход триггера 15 и запрещает поступление этого строба через элемент И 13. Сигнал с выхода элемента 9 задержки проходит через элемент И 10 на управляющий вход блока 5 контроля, на выход которого посту пают сигналы результатов контроля (Норма, Ненорма). Триггер 6, который меняет свое состояние при положительных результатах контроля, открывает элемент И 3 и подготавливает элемент И 7. В случае, если результаты контроля отрицательные, то сигнал об этом с выхода блока 5 контроля может быть использован для индикации необходимости повторной, выдачи информации или для изменения порога восстановления органа, установленного на выходе устройства. Последний Vt -разрядный блок информации записывается в регистр 1, а сигнал от заднего фронта импульса строба через элемент И 12 меняет состояние триггера 15, сигнал с выхода которого открывает элемент И 7, через который тактовая частота начинает поступать на делитель 8 частоты и регистр 1. С этого момента начинается этап выдачи последовательной кодограммы на устройства. При сдвиге кода на УИ разрядов сигнал с выхбда делителя 8 через элемент 9 задержки поступает на управляющий вход блока 5 контроля. Триггер 6 в зависимости от результатов контроля либо разрешает выдачу очередных w разрядов на выход устройства, либо закрывает элемент И 3. Передача оканчивается выдачей последних Y разрядов кодограммы на выход устройства, что соответствует нулевой информации в последних П разрядах регистра 1. Блок 5 контроля формирует сигнал Ненорма, и элементы И 3 и 7 закрываются. Преобразователь готов к передаче следующего Y -разрядного кода. Таким образом, проведение контроля информации после сдвига позволяет обнаружить возможное искажение этой информации на окончательном этапе преобразования - после прохождения 1 информации почти через все цепи и элементы преобразователя, участвующие в выдаче последовательной кодограммы. Операции ввода информации в регистр 1 сдвига и контроля ее осуществляются не на всех И разрядах, а только на Уи разрядах (( ц ГДе k - целое число). Введением контроля и уменьшением количества входных элементов И достигается повышение достоверности передаваемой кодограммы, т. е. повышение надежности преобразования. Формула изобретения Преобразователь параллельного кода в последовательный содержащий И - раз

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для передачи сигналов | 1990 |

|

SU1709533A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для сопряжения | 1981 |

|

SU966687A1 |

| Преобразователь кодов | 1980 |

|

SU917340A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Преобразователь последовательного кода в параллельный | 1981 |

|

SU970355A1 |

| Устройство для соряжения цифровой вычислительной машины с внешним накопителем | 1975 |

|

SU575653A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

Авторы

Даты

1980-09-30—Публикация

1977-07-22—Подача