(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обмена информацией, реализующих способ предварительного накопления массивов информации.

Известен преобразователь, содержащий информационные входы, два распределителя импульсов, два генератора импульсов, выходной регистр, феррит-диодную матрицу преобразования последовательных кодов группы чисел в последовательность чисел, представленных параллельным кодом 1.

Недостатки данного преобразователя заключаются в сравнительно больщом объеме оборудования и ограниченных функциональных возможностях.

Объем оборудования обусловлен необходимостью применения в преобразователе двух систем адресации с помощью первой из которых осуществляется последовательный ввод группы чисел исходного массива информации в элементы ферритовой матрицы, а с помощью второй системы адресации - выборка из элементов ферритовой матрицы исходного массива информации с одновременным его преобразованием в последовательВ ПАРАЛЛЕЛЬНЫЙ

ность чисел, представленных параллельным кодом, что не позволяет использовать в преобразователе элементы памяти, имеющие одну систему адресации, структура которых наиболее оптимальна для реализации в виде больщих интегральных схем.

Ограничение функциональных возможностей заключается в отсутствии преобразования исходного массива информации в последовательность чисел, представленных последовательным кодом.

Наиболее близким к предлагаемому является преобразователь, содержащий входной регистр, распределитель импульсов, элемент задержки, счетчик, дещифратор, группу 15 элементов И, группу регистров, группу коммутаторов, элемент И и элемент ИЛИ 2 .

Недостатками известного преобразователя являются больщие аппаратурные затраты обусловленные наличием, как системы выборки для поразрядной записи массива информации в регистры, так и системы выборки для почислового считываня информации из регистров, что исключает возможность использования в устройстве больших интегральных схем памяти, имеющих одну систему адресной выборки информации. Кроме того, известные преобразователи имеют ограниченные функциональные возможности, которые заключаются в том, что отсутствует возможность преобразования исходного массива информации в последовательность последовательных кодов.

Цель изобретения - сокращение аппаратурных затрат преобразователя.

Поставленная цель достигается тем, что преобразователь последовательного кода в параллельный, содержащий входной регистр распределитель имнульсов, первый элемент И, первый элемент задержки, блок памяти, счетчик по модулю m (ш - количество чисел преобразуемого массива информации), счетчик по модулю п (п - количество разрядов чисел преобразуемого массива информации), причем разрядные входы входного регистра являются входами преобразователя, вход синхронизации преобразователя соединен с установочным входом входного регистра, дополнительно содержит три элемента 2 И-ИЛИ, второй элемент И, второй элемент задержки, триггер, выходной регистр, при этом вход пуска распределителя импульсов соединен с входом синхронизации преобразователя и с входом записи входного регистра, первый выход распределителя импульсов соединен с входом считывания блока памяти, второй выход - с первыми входами первого и второго элементов 2 И-ИЛИ и с входами сдвига входного и выходного регистров, третий выход распределителя импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого элемента задержки, первым входом второго элемента И, вторыми входами первого и второго элементов 2 И-ИЛИ и первым входом третьего элемента 2 И-ИЛИ, вход управления режимом блока памяти, третьи входы первого и второго элементов 2 И-ИЛИ и второй вход третьего элемента 2 И-ИЛИ соединены с нулевым выходом триггера, единичный выход которого соединен с входом первого элемента задержки, выход переноса счетчика по модулю m соединен с четвертым входом второго элемента 2 И-ИЛИ, третьим входом третьего элемента 2 И-ИЛИ и через второй элемент задержки с четвертым входом третьего элемента 2И-ИЛИ, S-вход триггера соединен с выходом переполнения счетчика по модулю п, четвертым входом первого элемента 2 И-ИЛИ и вторым входом второго элемента И, R-вход триггера соединен с входами установки нуля счетчиков по модулю шипи является управляющим входом преобразователя, счетные входы счетчиков по модулю тип соединены соответственно с выходами первого и второго элементов 2 И-ИЛИ, разрядные выходы - соответственно с входами старших и млэдщих разрядов адреса блока памяти, информационный

выход которого соединен с информационным входом выходного регистра и является выходом последовательной информации преобразователя, разрядные выходы выходного регистра являются выходами преобразователя,

выходы первого и второго элементов И являются соответственно первыми и вторыми выходами синхронизации преобразователя, выход третьего элемента 2 И-ИЛИ соединен с входом останова распределителя импульсов, информационный вход блока па мяти соединен с информационным выходом входного регистра.

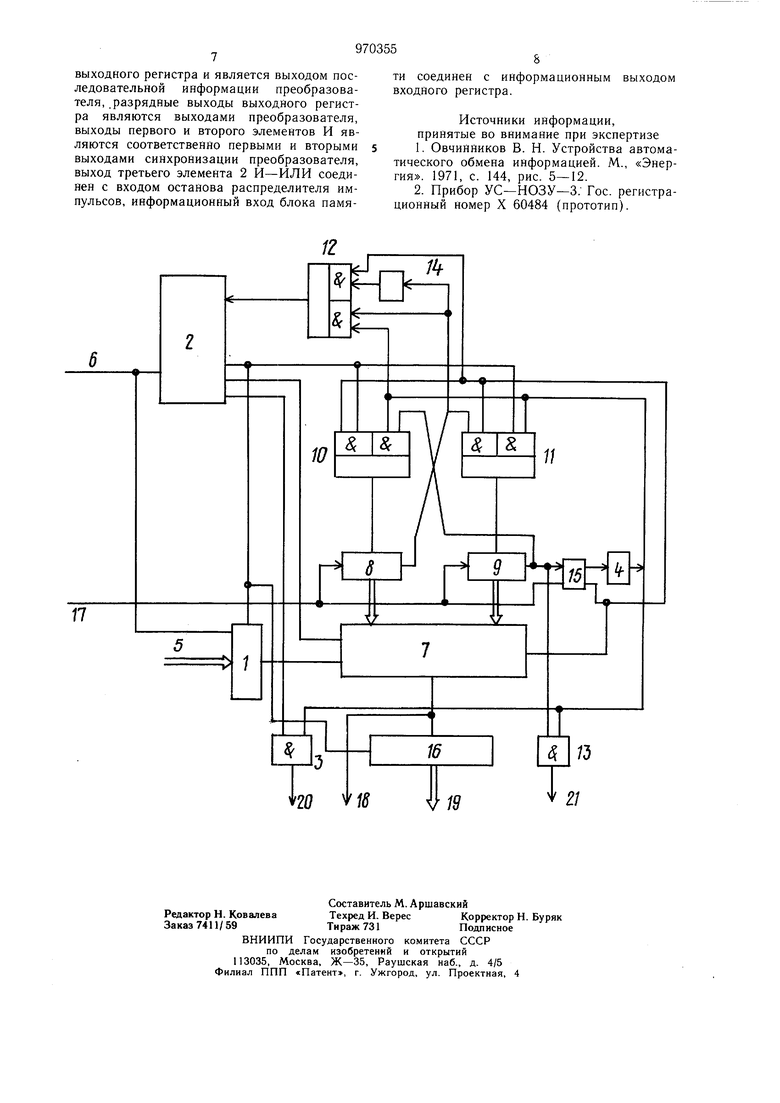

На чертеже приведена электрическая схема предлагаемого преобразователя.

Преобразователь содержит входной регистр 1, распределитель 2 импульсов, первый элемент И 3, первый элемент 4 задержки, информационные входы 5 преобразователя, вход 6 синхронизации, блок 7 памяти, счетчик 8 по модулю т, счетчик 9 по модулю п, элементы И-ИЛИ 10-12, второй элемент

И 13, второй элемент 14 задержки, триггер 15, выходной регистр 16, управляющий вход 17, выход 18 последовательной информации преобразователя, выход 19 параллельной информации, первый выход 20 синх5 ронизации, второй выход 21 синхронизации. Управляющий вход 17 является сигналом начала массива.

Первый и второй выходы 20 и 21 осуществляют соответственно разрядную и числовую синхронизацию.

0 Преобразователь работает следующим образом.

Сигнал, поступающий на вход 17 начала массива информации, устанавливает в нулевое состояние счетчик 8 по .модулю т, счетчик 9 по модулю п и триггер 15. Следующий далее i-ый сигнал На вход 6 синхронизации производит запись i-oro разряда (,... п) слов 1,...п преобразуемого массива информации, поступающих на входы 5 преобразователя, в соответствующие разря0 ды входного регистра 1. По фронту спада i-ro сигнала на входе 6 запускается распределитель 2 импульсов, на выходах которого вырабатываются циклические последовательности импульсов.

В каждом J-OM (J 1,..., т) цикле работы распределителя 2 по сигналу с его первого выхода происходит обращение к блоку 7 памяти и запись в него элемента (i - 1) m + j массива информации с выхода регистра 1. Сигнал с второго выхода распределителя 2 импульсов, поступая на вход сдвига регистра 1, производит сдвиг на один разряд находящегося в нем кода, а поступая на первый вход первого элемента И-ИЛИ 10 и далее на счетный вход счетчика 8 прибавляет единицу к его содержимому. В цикле m работы распределителя импульсов счет чик 8 по модулю m вырабатывает сигнал переноса, который, поступая на четвертый вход элемента И-ИЛИ И и далее с его выхода на счетный вход счетчика 9 по модулю п, увеличивает его содержимое на единицу. Сигнал переноса счетчика 8, проходя также через элемент задержки и элемент И-ИЛИ 12 на вход стопа распределителя 2 импульсов, останавливает поступление импульсов на его выходах. В цикле m работы распределителя 2 импульсов по записи в блок 7 памяти элемен . nm массива информации вырабатывается сигнал переноса счетчика 9,который устанавливает в единичное состояние триггер 15 сигнал с нулевого выхода которого запрещает поступление сигнала переноса счетчика 8 с выхода элемента 14 задержки через И-ИЛИ 12 на вход стопа распределителя 2 импульсов, а также переводит блок 7 памяти в режим считывания. В первом цикле работы распределителя 2 импульов после установки режима считывания информации из блока 7 памяти по сигналу с первого выхода распределителя 2 импульсов происходит считывание из блока 7 памяти сигнала первого разряда первого слова, который по сигналу сдвига со второго выхода распределителя импульсов записывается в выходной регистр 16. Аналогично первому разряду первого слова будут считываться и остальные разряды первого слова, последовательно записываясь в выходной регистр 16 и одновременно поступая на выход 18 преобразователя. Последовательная выдача разрядов числа на выход 18 преобразователя сопровождается сигналами, поступающими с выхода элемента И 3 на выход 20 синхронизации преобразователя. А параллельная выдача разрядов числа - сигналом, поступающим с выхода элемента И 13. После считывания из блока 7 памяти п-разрядов первого слова на выходе счетчика 9 вырабатывается сигнал переноса, который через элемент И 13 поступает на выход 21 синхронизации, сопровождая выдачу параллельного кода числа, а поступая через элемент И-ИЛИ 10 на счетный вход счетчика 8, увеличивает его содержимое на единицу. Последовательная выдача разрядов числа На выход 18 преобразователя сопровождается сигналами, поступающими с выхода элемента И 3 на выход 20 синхронизации преобразователя. Выдача остальных чисел массива информации происходит аналогично выдаче первого. После считывания из блока 7 памяти последнего элемента массива на выходе счет чика 8 образуется сигнал переноса, который, проходя через элемент И-ИЛИ 12, прекращает работу распределителя 2 импульсов. Таким образом, предлагаемый преобразователь помимо преобразования последовательных кодов группы чисел в последовательность чисел, представленных параллельным кодом, может производить также преобразование исходного массива в последовательность чисел, представленных последовательным кодом, что расщиряет функциональные возможности преобразователя, сокращает аппаратурные затраты. Формула изобретения Преобразователь последовательного кода в параллельный, содержащий входной регистр, распределитель импульсов, первый элемент И, первый элемент задержки, блок памяти, счетчик по модулю m (m - количество чисел преобразуемого массива информации), счетчик по модулю п (п - количество разрядов чисел преобразуемого массива информации), причем разрядные входы входного регистра являются входами преобразователя, вход синхронизации преобразователя соединен с установочным входом входного регистра, отличающийся тем, что, с целью сокращения аппаратурных затрат, он дополнительно содержит три элемента 2 И-ИЛИ, второй элемент И, второй элемент задержки, триггер, выходной регистр, при этом вход пуска распределителя импульсов соединен с входом синхронизации преобразователя и с входом записи входного регистра, первый выход распределителя импульсов соединен с входом считывания блока памяти, второй выход - с первыми входами первого и второго элементов 2 И - ИЛИ и с входами сдвига входного и выходного регистров, третий выход распределителя импульсов соединен с первым в.ходом первого элемента И, второй вход которого соединен с выходом первого элемента задержки, первым входом второго элемента И, вторыми входами первого и второго элементов 2 И-ИЛИ и первым входом третьего элемента 2 И-ИЛИ, вход управления режимом блока памяти, третьи входы первого и второго элементов 2 И-ИЛИ и второй вход третьего элемента 2 И-ИЛИ соединены с нулевым выходом триггера, единичный выход которого соединен с входом первого элемента задержки, выход переноса счетчика по модулю m соединен с четвертым входом второго элемента 2 И-ИЛИ, третьим входом третьего элемента 2 И- ИЛИ и через второй элемент заде.х-кки с четвертым входом третьего элемента 2 И-ИЛИ, S-вход триггера соединен с выходом переполнения счетчика по модулю п, четвертым входом первого элемента 2 И - ИЛИ и вторым входом второго элемента И, R-вход триггера соединен с входами установки нуля счетчиков по модулю m и п и является управляющим входом преобразователя, счетные входы счетчиков по модулю шип соединены соответственно с выходами первого и второго элементов 2 И-ИЛИ, разрядные выходы - соответственно с входами старщих и младщих разрядов адреса блока памяти, информационный выход которого соединен с информационным входом

выходного регистра и является выходом последовательной информации преобразователя, .разрядные выходы выходного регистра являются выходами преобразователя, выходы первого и второго элементов И являются соответственно первыми и вторыми выходами синхронизации преобразователя, выход третьего элемента 2 И-ИЛИ соединен с входом останова распределителя импульсов, информационный вход блока памяти соединен с информационным выходом входного регистра.

Источники информации, принятые во внимание при экспертизе

1.Овчинников В. Н. Устройства автоматического обмена информацией. М., «Энергия. 1971, с. 144, рис. 5-12.

2.Прибор УС-НОЗУ-3.- Гос. регистрационный номер X 60484 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1981 |

|

SU1005019A1 |

| Преобразователь последовательного кода в параллельный | 1990 |

|

SU1805548A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ | 1990 |

|

RU2007865C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Преобразователь кодов | 1980 |

|

SU917340A1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

Авторы

Даты

1982-10-30—Публикация

1981-02-27—Подача