Изобретение относится к вычислительной технике и может бытьиспользовано для синхронизации вычислительных систем.

Цель изобретения - расширение функциональных возможностей .за счет обеспечения передачи кодированных тактовых сигналов.

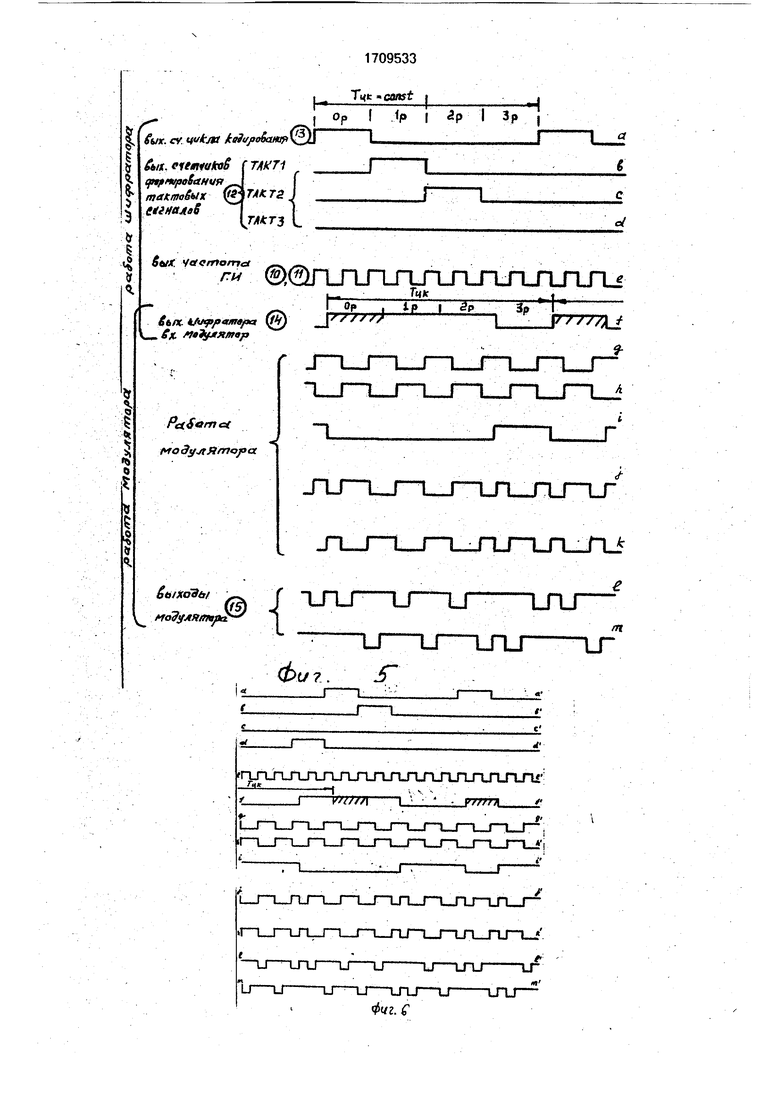

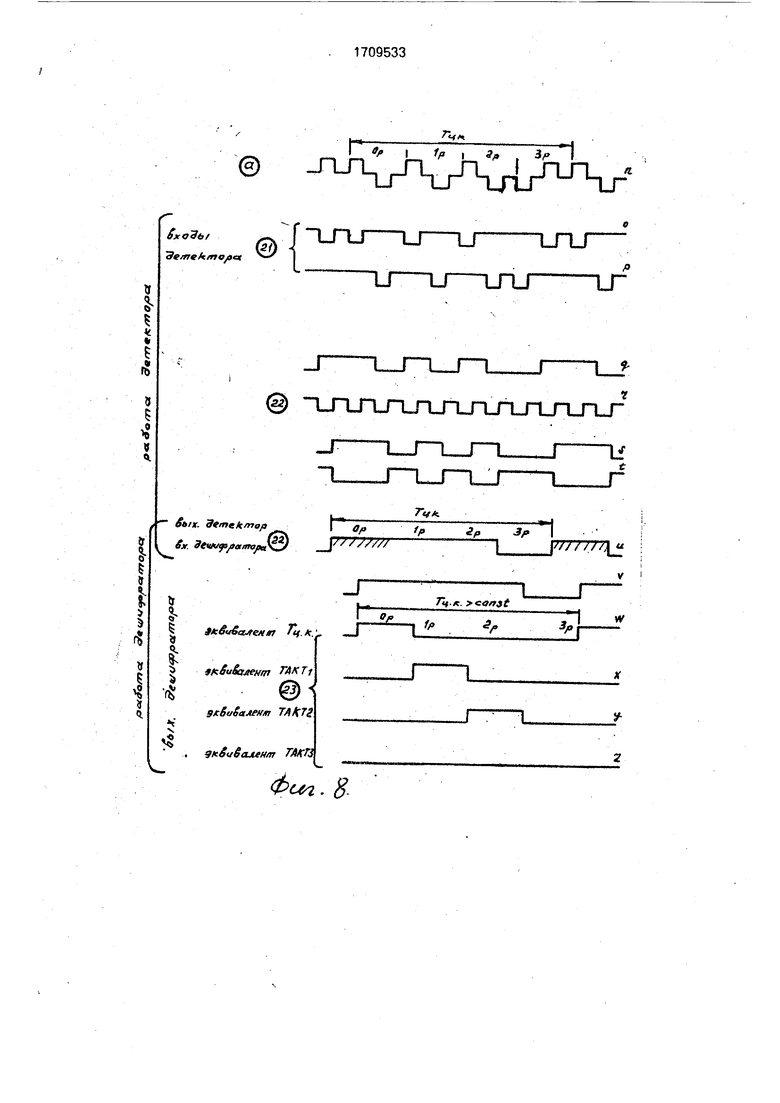

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - схема шифратора; на фиг.З - схема модулятора; на фиг.4 - схема детектора; на фиг.5-10 - временные диаграммы работы устройства.

Устройство содержит тактовый генератор 1, его выход 2, регистр 3 сдвига, распределитель 4 импульсов, преобразователь 5 цифрового кода в биполярный, счетчики 6 и 7 распределителя 4, шифратор 8, модулятор 9. тактовый вход 10 шифратора, вход 11 модулятора, информационные входы 12 и 13 шифратора, выход 14 шифратора, выходы 15 модулятора, преобразователь 16 биполярного кода в цифровой, детектор 17. дешифратор 18, формирователи 19 импульсов..

выходы 20. выходы 21 преобразователя 16. выходы 22 детектора и выходы 23 дешифратора.

Шифратор 8 содержит элемент ИЛИ 24. элемент НЕ 25 и триггер 26.

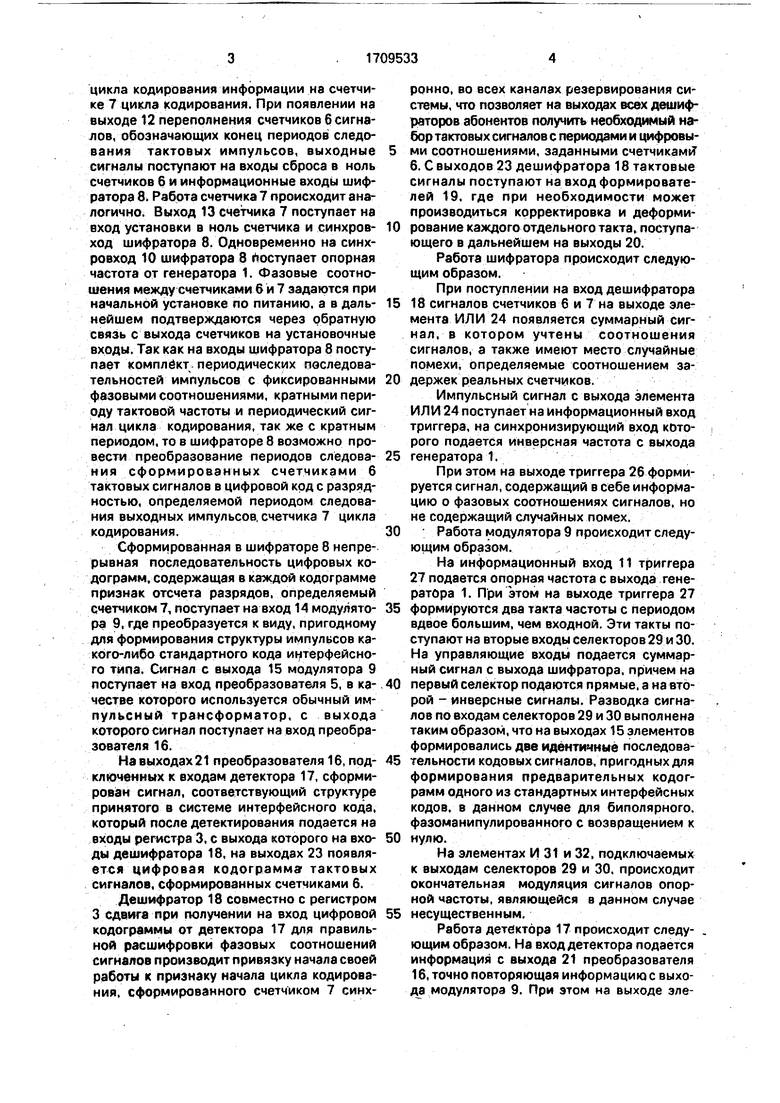

Модулятор 9 содержит счетный триггер 27. элемент НЕ 28. селекторы 29 и 30 и элементы И 31 и 32.

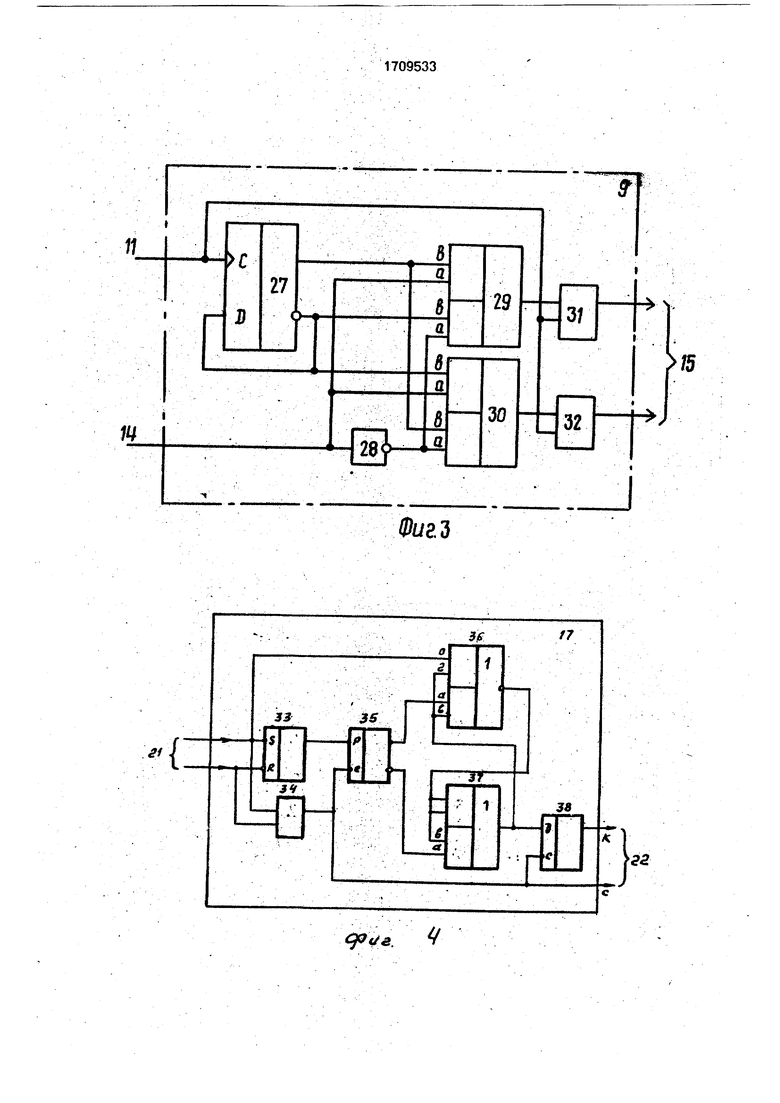

Детектор 17 содержит триггер 33. элемент ИЛИ 34. триггер 35. селекторы 36 и 37 и триггер 38.

Устройство работает следующим образом.

При включении питания происходит установка в исходное состояние счетчиков 6 и 7. на информационных входах которых заранее задан код начала отсчета. После того, как на входах счетчиков появляется частота, счетчики начинают отсчет времени периодов следования тактовых импульсов, величина которых определяется коэффициентом деления и обусловлена требованиями к характеру тактовых импульсов системы. Одновременно начинается отсчет времени

цикла кодирования информации на счетчике 7 цикла кодирования. При появлении на выходе 12 переполнения сметчиков 6 сигналов, обозначающих конец периодов следования тактовых импульсов, выходные сигналы поступают на входы сброса в ноль счетчиков 6 и информационные входы шифратора 8. Работа счетчика 7 происходит аналогично. Выход 13 счетчика 7 поступает на вход установки в ноль счетчика и синхровход шифратора 8. Одновременно на синхровход 10 шифратора 8 {поступает опорная частота от генератора 1. Фазовые соотношения между счетчиками 6 и 7 задаются при начальной установке по питанию, а в дальнейшем подтверждаются через обратную связь с выхода счетчиков на установочные входы. Так как на входы шифратора 8 поступает комплект, периодических последовательностей импульсов с фиксированными фазовыми соотношениями, кратными периоду тактовой частоты и периодический сигнал цикла кодирования, так же с кратным периодом, то в шифраторе В возможно провести преобразование периодов следования сформированных счетчиками 6 тактовых сигналов в цифровой код с разрядностью, определяемой периодом следования выходных импульсов, счетчика 7 цикла кодирования.

Сформированная в шифраторе 8 непрерывная последовательность цифровых кодограмм, содержащая в каждой кодограмме признак отсчета разрядов, определяемый счетчиком 7, поступает на вход 14 модулятора 9, где преобразуется к виду, пригодному для формирования структуры импульсов какого-либо стандартного кода и 51терфейсного типа. Сигнал с выхода 15 модулятора 9 поступает на вход преобразователя 5, в качестве которого используется обычный импульсный трансформатор, с выхода которого сигнал поступает на вход преобразователя 16.

На выходах 21 преобразователя 16, подключенных к входам детектора 17, сформирован сигнал, соответствующий структуре принятого в системе интерфейсного кода, который после детектирования подается на входы регистра 3. с выхода которого на входы дешифратора 18, на выходах 23 появляется цифровая кодограмма тактовых сигналов, сформированных счетчиками 6.

Дешифратор 18 совместно с регистром 3 сдвига при получении на вход цифровой кодограммы от детектора 17 для правильной расшифровки фазовых соотношений сигналов производит привязку начала своей работы к признаку начала цикла кодирования, сформированного счетчиком 7 синхронно, во всех каналах резервирования системы, что позволяет на выходах всех дешифраторов абонентов получить необходимый набор тактовых сигналов с периодами и цифровыми соотношениями, заданными счетчикамИ 6. С выходов 23 дешифратора 18 тактовые сигналы поступают на вход формирователей 19, где при необходимости может производиться корректировка и деформирование каждого отдельного такта, поступающего в дальнейшем на выходы 20.

Работа шифратора происходит следующим образом.

При поступлении на вход дешифратора

5 18 сигналов счетчиков 6 и 7 на выходе элемента ИЛИ 24 появляется суммарный сигнал, в котором учтены соотношения сигналов, а также имеют место случайные помехи, определяемые соотношением задержек реальных Счетчиков.

Импульсный сигнал с выхода элемента ИЛИ 24 поступает на Информационный вход триггера, на синхронизирующий вход которого подается инверсная частота с выхода

5 генератора 1.

При этом на выходе триггера 26 формируется сигнал, содержащий в себе информацию о фазовых соотношениях сигналов, но не содержащий случайных помех.

0 ; Работа модулятора 9 происходит следующим образом.

На информационный вход 11 триггера 27 подается опорная частота с выхода генератора 1. При этом на выходе триггера 27

5 формируются два такта частоты с периодом вдвое большим, чем входной. Эти такты поступают на вторые входы селекторов 29 и 30. На управляющие входы подается суммарный сигнал с выхода шифратора, причем на

0 первый селектор подаются прямые, а на второй - инверсные сигналы. Разводка сигналов по входам селекторов 29 и 30 выполнена таким образом, что на выходах 15 элементов формировались две идентичные последовательности кодовых сигналов, пригодных для формирования предварительных кодограмм одного из стандартных интерфейсных кодов, в данном случае для биполярного, фазоманипулированного с возвращением к

0 нулю.

На элементах И 31 и 32, подключаемых к выходам селекторов 29 и 30, происходит окончательная модуляция сигналов опорной частоты, являющейся в данном случае

5 несущественным.

Работа детектора 17 происходит следу- , ющим образом. На вход детектора подается информация с выхода 21 преобразователя 1 б, точно повторяющая информацию с выхода модулятора 9. При этом на выходе элемента ИЛИ 34 из кодограмм выделяется опорная частота 1, а с помощью триггеров 33 и 35 и селекторов 36 и 37 выделяется сигнал, содержащий информацию о фазовых соотношениях сигналов, сформированных счетчиками б и 7. Триггер 38 предназначен для защиты последующей схемы от помех, вызванных случайным соотношением задержек элементов схемы, выходы триггера 38 и элемента ИЛИ 34 являются выходами 22 детектора.,

На информационный вход регистра 3 подается кодовая последовательность импульсов с выхода 22 детектора 17, а на синхровход подается частота с выхода 22 элемента ИЛИ 34, При этом число разрядов регистра 3 выбирается таким образом, что за интервал времени, определяемый счетчиком 7 цикла кодирования, сменяют свое состояние все разряды. Выделение тактовыу сигналов, эквивалентных сигналам на выхо-х де счетчиков б и 7, производится дешифратором 18, разрядность которого также определяется исходя из числа исходных тактовых сигналов. Сигналы с выхода 23 дешифраторапоступают на вход формирователей 19, в качестве которых могут использоваться, например,одновибраторы 133 АГЗ или аналогичные,

Формула изобретения Т. Устройство для передачи сигналов, содержащее тактовый генератор, распределитель импульсов, шифратор, преобразователь цифрового кода в бипрлярный, преобразователь .биполярного кода в цифровой, дешифратор и группу формирователей импульсов, причем дешифратора соединены с входами формирователей импульсов группы, выходы которых являются выходами устройства, отличающееся .тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения пере-, дачи кодированных тактовых .сигналов, в него введены модулятор, детектор и регистр сдвига, причем выход тактового генератора соединен с синхровходом модулятора и входом распределителя импульсов, выходы которого соединены с входами шифратора, выход которого соединен с информационным входом модулятора, выходы которого соединены с входами преобразователя ц11фрового кода в биполярный, выход которого соединен с входом преобразователя биполярного кода в цифровой, выходы которого соединены с входами детектора, первый выход которого соединен с информационным входом первого разряда регистра сдвига, синхровход которого соединен с вторым

выходом детектора, выходы регистра сдвига соединены с входами дешифратора.

2. Устройство поп.1,отличающеес я тем, что модулятор содержит счетный триггер, два селектора, элемент НЕ и два элемента И, причем счетный вход счетного триггера соединен с первым входом первого элемента И, первым входом второго элемента И и является информационным входом модулятора, прямой выход счетного триггера соединен с первыми информационными входами первого и второго селекторов, вторые информационные входы которых соединены с инверсным выходом счетного триггера, вход элемента НЕ соединен с первым управляющим входом первого селектора, с вторым управляющим входом второго селектора и является синхровходом модулятора, выход элемента НЕ соединен с первым управляющим -входом второго селектора и вторым управляющим входом первого селектора, выходы первого и второго элементов И являются соответственно первым и вторым выходами модулятора. / 3. Устройство по п.1,отличающееся тем, что детектор содержит три триггера, элемент ИЛИ и два селектора, причем вход установки в единицу первого триггера.соединен с первым входом элемента ИЛИ, первым информационным входом первого селектора и является первым входом детектора, вход сброса первого триггера соединен с вторым входом элемента ИЛИ и является вторым входом детектора, выход первого триггера соединен с информационным входом второго триггера, синхровход которого соединен с выходом элемента ИЛИ, с синхровходом третьего триггера и является первым выходом детектора прямой выход второго триггера соединен с вторым информационным входом первого селектора, инверсный выход второго триггера соединен с первым информационным входом второго селектора, первый управляющий вход которого соединен с вторым управляющим входом второго селектора, вторым информационным входом второго селектора и инверсным выходом первого селектора, выход второго селектора соединен с информационным входом третьего триггера, первым и вторым управляющими входами первого селектора, выход третьего триггера является вторым выходом детектора.

4. Устройство по П.1, отличающеес я тем, что шифратор соодержит элемент ИЛИ, триггер и элемент НЕ, причем входы элемента ИЛИ являются информационными входами шифратора, выход элемента ИЛИ соединен с информационным входом триггера, синхровход которого соединен с выходом элемента НЕ, вход которого является тактовым входом шифратора, выход триггера является выходом шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для идентификации кодограмм-сообщений | 1990 |

|

SU1805481A1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для передачи и приема дискретной информации | 1979 |

|

SU1099321A1 |

| Устройство для сопряжения канала передачи данных с магистралью | 1986 |

|

SU1444787A1 |

| Система передачи и приема информации | 1987 |

|

SU1411795A1 |

| Устройство для контроля работы оператора | 1990 |

|

SU1718263A2 |

Изобретение относится к вычислительной технике, может быть использовано для синхронизации вычислительных систем и позволяет сократить число передающих линий. Цель изобретения - расширение функциональных возможностей за счет обеспечения передачи коди- рованных тактовых сигналов. Это достигается за счет введения модулятора 9. детектора 17 и регистра 3 сдвига. 3 з,п. ф-лы. 10 ил.

W

Фиг 2

31

Фигд

Op ( p I i2p I 3p ftM Чччтогпс .. ,,,1,.. г ©©TLTiJnjnjajijn fb/K. tf ffnuf Q ffff ,д; PetSomet Af ЗулЯ/по а

ёшходь/

о9улЯ1тр

(

rUTJTjnjTJTJXTUTJTJXnJTJTJTJTJTJTl:

7ч

Тц«: const

Ч

г ip I Зр

ии-

Л7

ч4(/г. . -tутттт)

сч

1

1

с/ /nJTJT-TUOJ JTJlJTJTJl.

/

Yffyff/(

J L

Cft. J- - ЧгГЧУЧг г гЧг

Of IP Sft . 3f

deffreft/nofat

Ч.

r§

Ч.

. dfmeftmofl tviuyifaiaofn

SkSvSetJteHn ftf. .

fsfu&rjtejvfft TAKTi

дкбаёллент 7Af(J

дкбчёсиинт ТАКП

ФС4. 8 uглJlJ JlJlJ J

уТТТТТ/

W

L

/.

J7T7777I

Ul

w

иIT

V77///r

фс(г. /

У////7,

| Bonpocti радиоэлектроники Серия ЭВТ,вып | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU105A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-02—Подача