:,. 1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислитель-.; ных машинах, и устройствах дискретной автоматики. 5

Известны устройства сдвига, построенные на сдвиговых регистрах fl} или в виде комбинационных схем/23и з}.

Недостатком первых является увеличение времени при сдвиге на п разря- 10 дов пропорционально п.

Наиболее близким техническим решением к изобретению является устройство параллельного сдвига информации, содержащее элементы И,ИЛИ, сгуппиро- j ванные по разрядам и яpycclм, и узлы управления каждого яруса, причем камшый разряд каждого яруса содержит два элемента И и один.элемент ИЛИ, входы которого подключены к выходам JQ элементов И своето разряда, первый вход первого элемента И i-ro (, 2...,n) (n-число разрядов устройства) разряда и первый вход второго элемента И (i+l)-ro разряда первого 25 яруса подсоединены к i-му информационному входу устройства, выход элемента ИЛИ i-ro разряда j-ro яруса (,2,...,t) (t - число ярусов схемы) подключен к первому входу первр- JQ

го. элементб И i -го разряда и первому элемента И (Я-2)-го разряда (j+l)-ro яруса, выходы элементов ИЛИ последнего яруса - к выходам устройства, вторые входы первых элементов И и вторые входы вторых элементов И каждого разряда j-ro яруса подключены соответственно к j-му инверсному и j-му прямому управляющим входам устройства 2.

Недостаток этого устройства в том, что оно предназначено только для логических сдвигов вправо или влево, т.е. сдвигов с потерей младших или старпшх , причем для обеспечения сдвигов влево необходимо в первые п-2 разряды кал-дого j-ro яруса вводить дополнительный элемент И.

Цель изобретения - расширение функциональных возможностей устройства параллельного сдвига информации путем обеспечения циклического сдвига вправо и влево.

Постайленная цель достигается тем, что в каждом J-M ярусе первый вход второго элемента И i-ro разряда (1 1,2,.. . ,2) подключен к выходу элемента ИЛИ (п-2 +i )-го разряда (j-l)-ro яруса, вторые входы первых

элементов И разрядов, начиная с (2. )-го по ()-и подсоединены к первому выходу узла управления j-ro яруса, вторые |зходы первых элементов И остальных разрядов - ко второму выходу узла управления j-ro яруса, вто-. рые-входы вторых элементов И разря- ; дов, начиная с первого по 2 соединёна с третьим выходом узла управления j-ro, яруса, при этом вторые .Входы вторых элементов И остальные разрядов соединены с четвертым входом j-ro узла управления, вторые входы первых элементов И последнего t-ro яруса () разрядов, начиная с первого по ( -1)й подключены, к первому вмходу; узла управления t-rOяруса, вторые входы первых элементов И остальных разрядов подключёны ко второму выходу узла управлеНИИ яруса, вторые входы- вторых элементов И Ь-гс яруса разрядов , начиная с первого по ()-й,подклю ijeHiar К третьёму выходу узла управления t-ro яруса, второй вход второго элемента И последнего разряда подсоединенКчетвертому входу узла управления t-ro яруса, вторые входы вторых элементов И остальных разрядов t-ro яруса подключетл к пятому входу узла улравлёния t-ro яруса, входы узла ,., йравлёния j-ro яруса - к управляю-. -, щим входам устройства.

Узел управления j-ro яруса ( 2,...t-1, где t - число ярусов устройства), содержит.элемент НЕ и два элемента И, причем первый вход узла уйравления подключен к первому входу первого элемента И, второй вход КОвторому входу второго элемента И, третий вход - ко. входу элемента НЕ и первому входу второго элемента И, выход элемента НЕ подсоединен ко Второму входу второго элемента и.

Узел управления t-ro яруса (где t --ЧИСЛО ярусов устройства) содержит элемент НЕ и три элемента И, причем первый вход узла управления t-гойруса соединен с первым входом первого элемента И и вторым входом третьего элемента И, второй вход уза )ЕШ вводом второго ;элёмён-та И, третий вход узла - с первым входом третьего элемента И, вход элемента НЕ подклйфён к пятому .выхо- у узла, к третьему входу узла и к ервому вхОдувторого элемента.И, : ыход элемента НЕ подключен соответтвенно кО второму входу первого элеента И и первому выходу узла управения. ..- ,;,-.;.--.,-. -.-.....:...,-: . . .

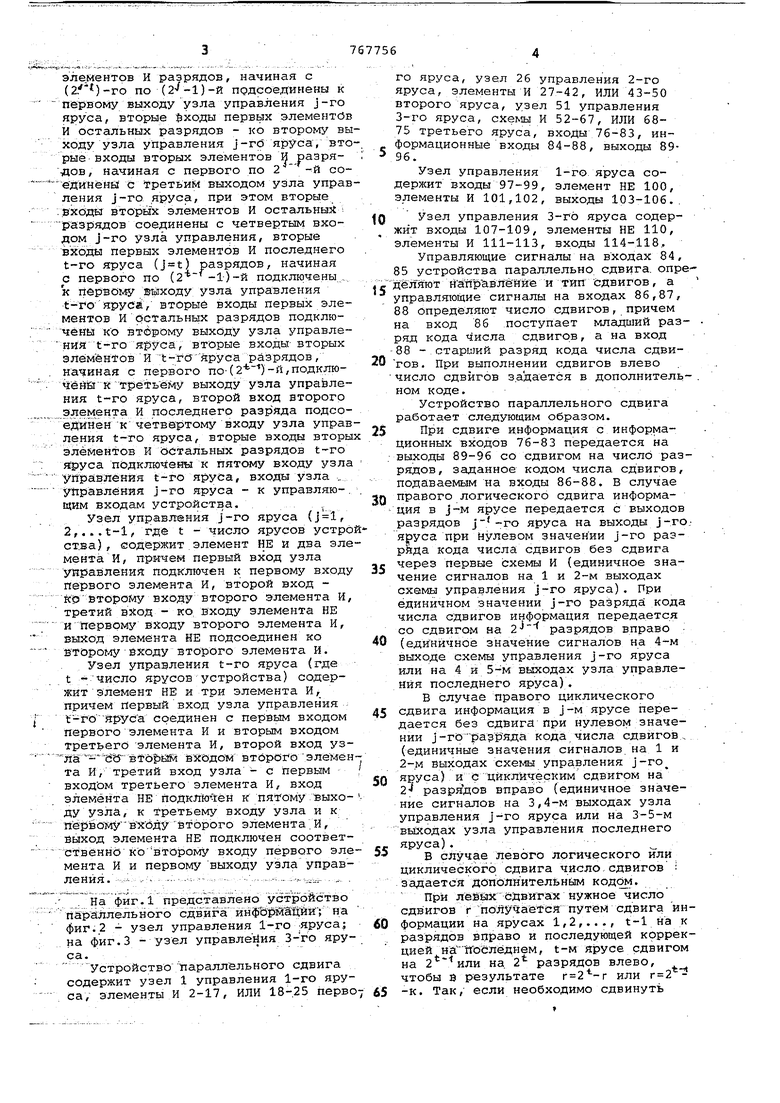

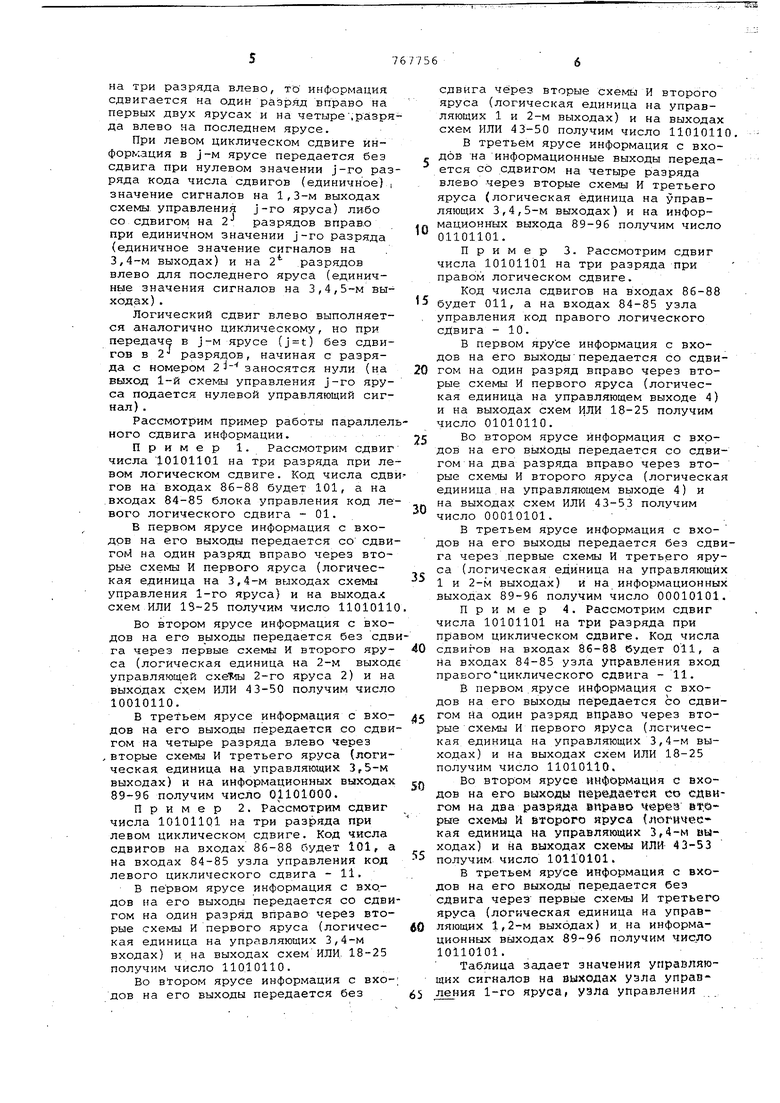

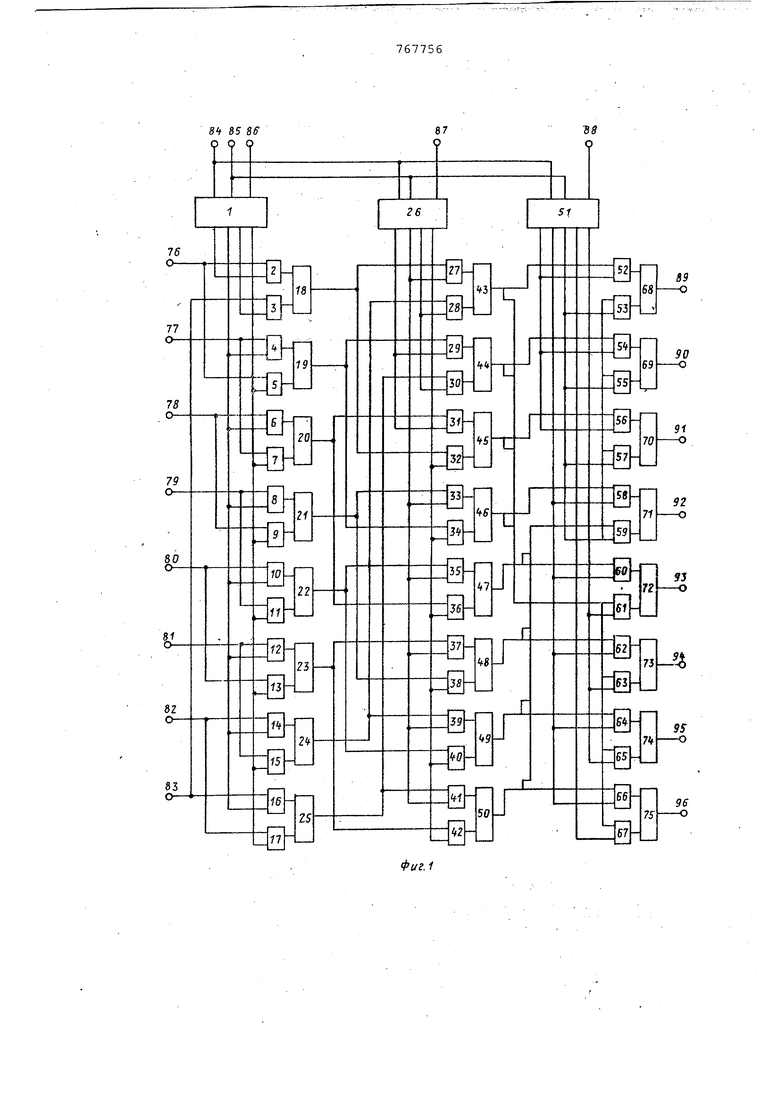

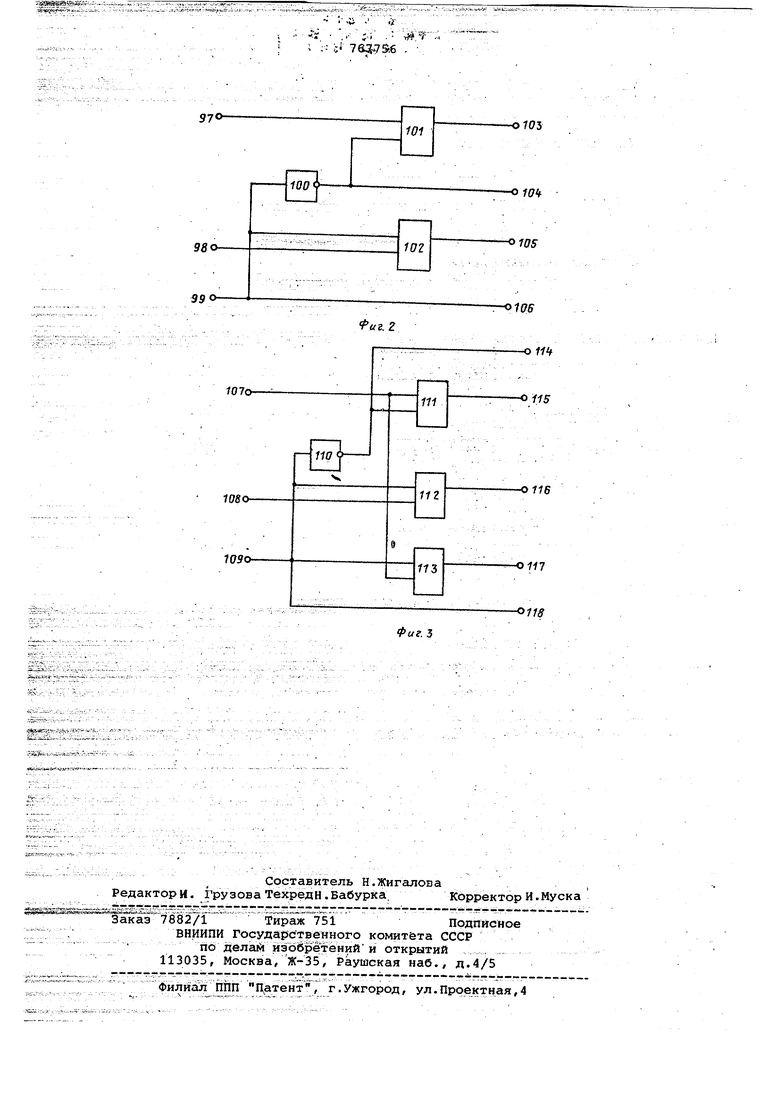

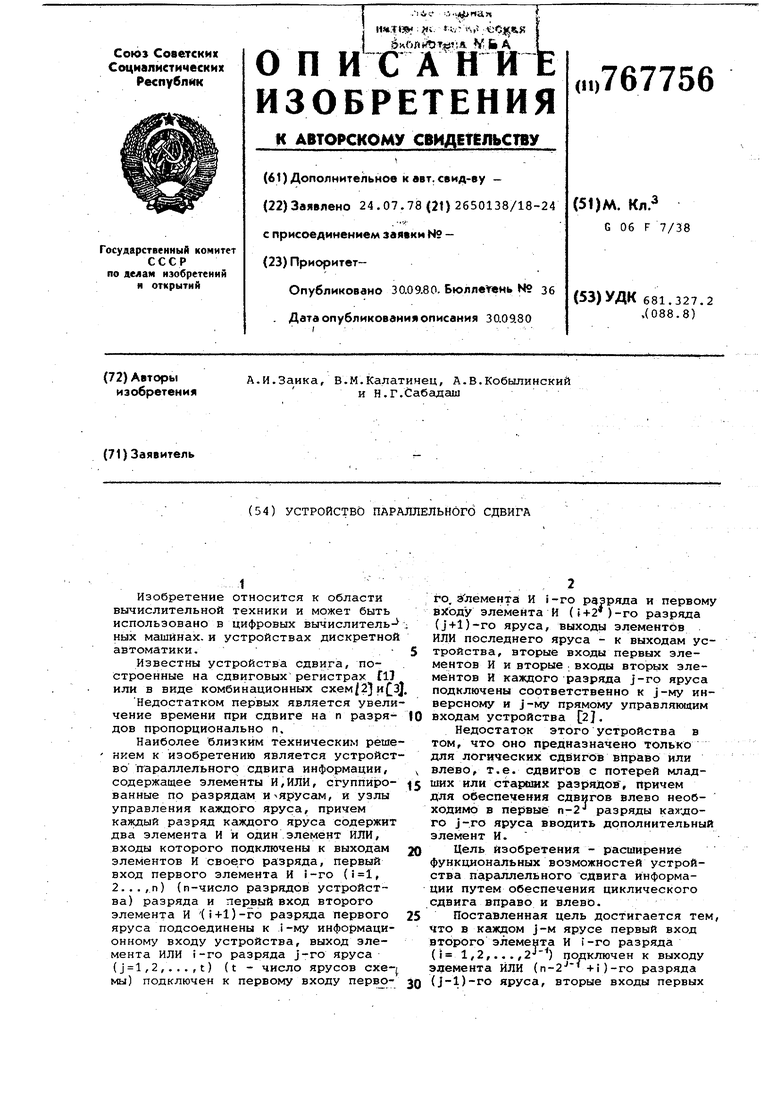

На фиг.1 представлено Устройство парйллельного сдвига йнфЬрйай йй ; на фиг.2 - узел управления 1-го :Яруса; на фиг.З - узел управлейия З-го яруса.

Устройство параллельного сдвига содержит узел 1 управления 1-го яруса, элементы И 2-17, ИЛИ 18-25 первого яруса, узел 26 управления 2-го яруса, элементы И 27-42, ИЛИ 43-50 второго яруса, узел 51 управления 3-го яруса, схемы И 52-67, ИЛИ 6875 третьего яруса, входы 76-83, информационные входы 84-88, выходы 8996.

Узел управления 1-го яруса содержит входы 97-99, элемент НЕ 100, элементы И 101,102, выходы 103-106..

Узел управления 3-гО яруса содержит входы 107-109, элементы НЕ 110, элементы И 111-113, входы 114-118..

Управляющие сигналы на входах 84, 85 устройства параллельно сдвига, опрДёШют на пр&влёййе и тип сдвигов, а управляющие сигналы на входах 86,87, 88 определяют число сдвигов, причем на вход 86 .поступает младший разряд кода чсисла сдвигов, а на вход 88 -.старший разряд кода числа сдвигов. При выполнении сдвигов влево число сдвигов з.адается в дополнительном коде..

Устройство параллельного сдвига работает следующим образом.

При сдвиге информация с информационных входов 76-83 передается на выходы 89-96 со сдвигом на числО разрядов, заданное кодом числа сдвигов, подаваемым на входы 86-88. В случае правого логического сдвига информация в J-M ярусе передается с выходов разрядов яруса на выходы j-ro яруса при Нулевом значении j-ro разряда кода числа сдвигов без сдвига через первые схемы И (единичное значение сигналов на 1 и 2-м выходах схемы управления j-ro яруса). При единичном значении j-ro разряда кода числа сдвигов информация передается со сдвигом на 2 разрядов вправо (единйчное значение сигналов на 4-м выходе схемы управления j-ro яруса или на 4 и 5-м выходах узла управления последнего яруса).

В случае правого циклического сдвига информация в J-M ярусе передается без сдвига при нулевом значении j-гO pa pядa кода числа сдвигов. (единичные значения сигналов.на 1 и 2-.М выходах схемы управления j-ro яруса) и с циклическим сдвигом на 2- разрядов вправо (единичное значение сигналов на 3,4-м выходах узла управления j-ro яруса или на 3-5-м вьйсодах узла управления последнего яруса) . .

В случае левого логического 11ли циклического сдвига число, сдвигов задается дополнителбнам кодом.

При левах йДвйгах нужное число сдвигов г получается путем сдвига информации на ярусах 1,2,..., t-1 на к разрядов вправо и последующей коррекцией на гГОслёднем, t-M ярусе сдвигом

на 2 или на. 2

разрядов влево,

или г 2 чтобы S результате

-к. Так, если необходимо сдвинуть

на три разряда влево, то информация сдвигается на один разряд вправо на первых двух ярусах и на четыре .разряда влево на последнем ярусе.

При левом циклическом сдвиге информация в j-м ярусе передается без сдвига при нулевом значении j-ro разряда кода числа сдвигов (единичное) ; значение сигналов на 1,3-м выходах схемы управления j-ro яруса) либо со сдвигом на 2- разрядов вправо при единичном значении j-ro разряда (единичное значение сигналов на 3,4-м выходах) и на 2 .разрядов влево для последнего яруса (единичные значения сигналов на 3,4,5-м выходах) .

Логический сдвиг влево выполняется аналогично циклическому, но при передаче в j-м ярусе () без сдвигов в 2 разрядов, начиная с разряда с номером 2 J заносятся нули (на выход 1-й схемы управления j-ro яруса подается нулевой управляющий сигнал) .

Рассмотрим пример работы параллелного сдвига информации,

Пример 1. Рассмотрим сдвиг числа 10101101 на три разряда при левом логическом сдвиге. Код числа сдв гов на входах 86-88 будет 101, а на .входах 84-85 блока управления код левого логического сдвига - 01.

В первом ярусе информация с входов на его выходы передается со сдвигоМ на один разряда вправо через вторые схемы И первого яруса (логическая единица на 3,4-м выходах схемы управления 1-го яруса) и на выходах схем ИЛИ 15-25 получим число 11010110

Во втором ярусе информация с входов на его выходы передается без сдвга через первые схемы И второго яруса (логическая единица на 2-м выход управляющей схеТш 2-го яруса 2) и на выходах схем ИЛИ 43-50 получим число 10010110.

В третьем ярусе информация с вхо.дов на его выходы передается со сдвигом на четыре разряда влево через , вторые схемы И третьего яруса (логическая единица на управляющих 3,5-м выходах) и на информационных выходах 89-96 получим число 01101000.

Пример 2. Рассмотрим сдвиг числа 10101101 на три разряда при левом циклическом сдвиге. Код числа сдвигов на входах 86-88 будет 101, а на входах 84-85 узла управления код левого циклического сдвига - 11.

В первом ярусе информация с BXQдов на его выходы передается со сдвигом на один разряд вправо через вторые схемы И первого яруса (логическая единица на управляющих 3,4-м входах) и. на выходах схем ИЛИ.. 18-25 получим число 110.10110.

Во втором ярусе информация с входов на его выходы передается без

сдвига через вторые схемы И второго яруса (логическая единица на управляющих 1 и 2-м выходах) и на выходах схем ИЛИ 43-50 получим число 11010110.

В третьем ярусе информация с вхоg дов на информационные выходы передается со сдвигом на четыре разряда влево через вторые схемы И третьего яруса (логическая единица на управляющих 3,4,5-м выходах) и на информационных выхода 89-96 получим число

0 01101101.

Пример 3. Рассмотрим сдвиг числа 10101101 на три разряда при правом логическом сдвиге.

Код числа сдвигов на входах 86-88

5 будет 011, а на входах 84-85 узла управления код правого логического сдвига - 10.

В первом ярусе информация с входов на его ВЫХОДЫпередается со сдви0гом на один разряд вправо через вторые схемы И первого яруса (логическая единица на управляющем выходе 4) и на выходах схем ИЛИ 18-25 получим число 01010110.

Во втором ярусе информация с вхо5дов на его выходы передается со сдвигом на два разряда вправо через вторые схемы И второго яруса (логическая единица.на управляющем выходе 4) и на выходах схем ИЛИ 43-53 получим

0 число 00010101.

В третьем ярусе информация с входов на его выходы передается без сдвига через первые схемы И треть.его яруса (логическая единица на управляющих

5 1 и 2-м выходах) и на информационных выходах 89-96 получим число 00010101.

Пример 4. Рассмотрим сдвиг числа 10101101 на три разряда при правом циклическом сдвиге. Код числа

0 сдвигов на входах 86-88 будет 011, а на входах 84-85 узла управления вход правого циклического сдвига - 11.

В первом .ярусе информация с входов на его выходы передается со сдвигом на один разряд вправо через вто5рые схемы И первого яруса (логическая единица на управляющих 3,4-м выходах) и на выходах схем ИЛИ 18-25 получим число 11010110.

Во втором ярусе информация с вхо0дов на его выходы пёредаетей ео сдвигом на два разряда вправо через вторые схемы И второго яруса (логическая единица на управляющих 3,4-м выходах) и на выходах схемы ИЛИ 43-53 5 получим число 10110101.

В третьем ярусе информация с входов на его выходы передается без сдвига через первые схемы И третьего яруса (логическая единица на управляющих 1,2-м выходах) и на информа0ционных выходах 89-96 получим число 10110101.

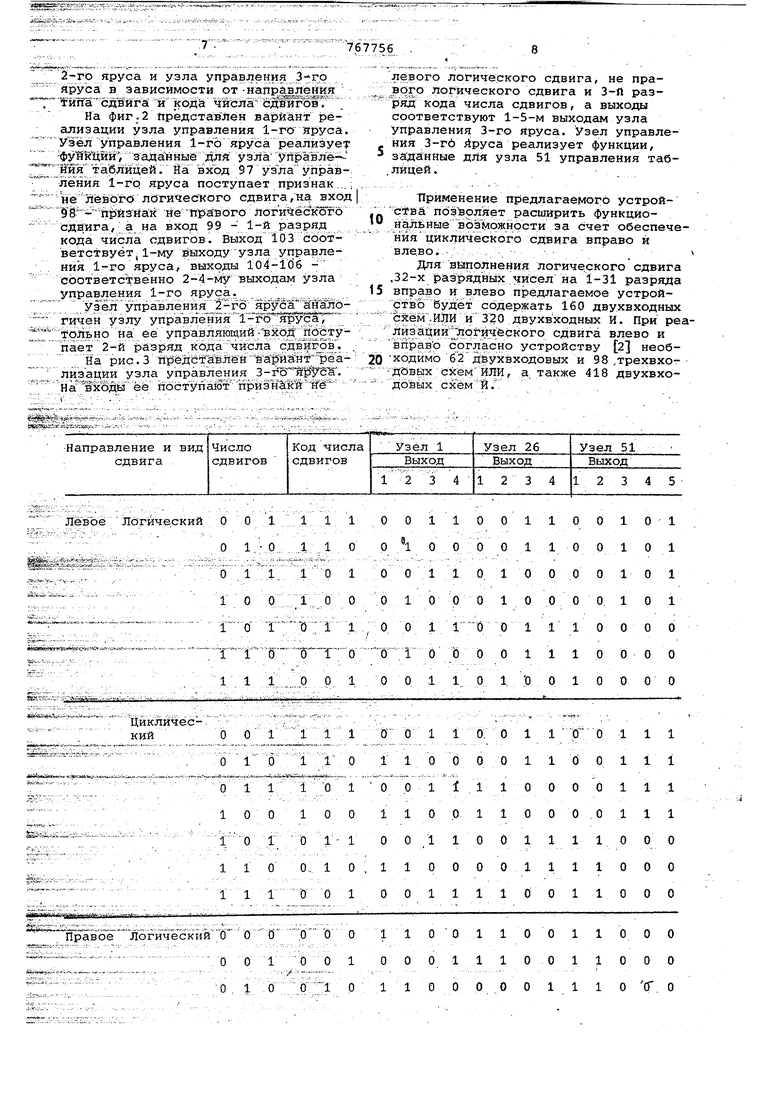

Таблица задает значения управляющих сигналов на выходах узла управления 1-го яруса, узла управления

2-гр яруса и узла управления З-то яруса в зависимости от-напр,лед|(я

T iffia cSSiii и кодй чй М е даигов ; На фиг.2 Прёдставглён вариант реализации узла управления 1-го яруса.

Уз ел управле н ия 1-го ярус а реализует з Шзайныё дли узла Угт авлё- ия таблицей. На вход 97 управ-; лёнйя 1-го яруса поступает признак.; не йевогс) логичестссго Сдвига,на вход S8 - прйэ йак йе прайого логичесШго сдв.ига, а на вход 99 -1-:а разряд кода числа сдвигов. Выход 103 Соответствует, 1-му в 1аходу узла управления 1-го яруса, выходы 104-1об -; сЬответственно 2-4-й;у выходам узла управления 1-го яруса. .. Управлени я 2-г6 , гичен узлу управления Г-Тг-о яруса,

тольно на ее управляющийвход поступаетГ2 й разряд кода числа сдвигов.

На рис.3 представлен sapiHctHT Лйзации узла управления 3-1о й:У7йЖ.

На 1Шда ее поступают признакиrfe

5 %eiii.-Hr ; :- : --/--- iSRS X ii--; i : Scu; - - -;. --;певого логического сдвига, не праj BOro логического сдвига и З-П разРЯД кода числа сдвигов, а выходы соответствуют 1-5-м выходам узла управления 3-го яруса. Узел управления 3-гб йруса реализует функции, заданные для узла 51 управления таб,лицей.

Применение предлагаемого устрой cfB пбз оляег расширить функцйо.нальнае возможности за счет обеспечения циклического сдвига вправо и влево.--, . , - -. - ч

Для ваполнениз Логиче.ского сдвига .32-х разрядных чисел на 1-31 разряда 15 вправо и влево предлагаемое устройство будет содержать 160 двухвходных схем-ИЛИ и 320 двухвходных И. При реализации логического сдвига влево и вправо согласно устройству 2 необ0 ходимо 62 дьухвходовых и 98 ,трехвхоДЪвых схем ИЛИ, а также 418 двухвходовых И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации | 1983 |

|

SU1117632A1 |

| Устройство для сдвига информации | 1975 |

|

SU643864A1 |

| Устройство для параллельного сдвига информации | 1977 |

|

SU622079A1 |

| Запоминающее устройство с параллельным произвольным доступом к строкам и окнам данных | 1987 |

|

SU1499355A1 |

| Устройство для уплотнения информации | 1981 |

|

SU978140A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для параллельного сдвига информации | 1978 |

|

SU700865A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

О О О 1 Правое Логический О О О О о 1 О О 1 : .----- 0. 1 о 01 0 1 001 1 О О 1 1 00 О 001110011000 1 О О 00 о 1 1 1 о V. о

Формула изобретения

элемента И i-ro разряда (,2,..., 2) .подключен к выходу элемента ИЛИ ( +i) разряда (j-l)-ro яруса.

Продолжение таблицы

(вторые входи первых элементов И разрядов, начиная с ()-го по (2 -1)-й подключены к первому выходу узла управления j-го яруса, вторые входы первых элементов И остальных разрядов подсоединены ко второму выходу узла управления j-ro яруса, а вторые входы вторых элементов. И раз- рядов, начиная с первого по 2 -и соединены с/третьим выходом узла управления J-ro яруса, при этом вторые входы вторых элементов И остальных разрядов соединены .с четвертым входом узла управления З-гояруса, втбрые входы первых элементов И последнего t-ro яруса разрядов, начиная с с nt-

первого по (2 -1)-й, подключены к первому выходу t-ro узла управления, вторые входы первых элементов И остальных разрядов подключены ко вто- .

рому выходу t-ro узла управления-, вторые входы вторых элементов И t-ro яруса разрядов, начиная с первого по ( 2)-и, подключены к третьему выходу узла управления t-ro яруса, второй вход второго элемента И последнего разряда подключен к четвертому входу узла управления t-ro яруса, вторые входы вторых элементов И остальных разрядов t-ro яруса подключены к пятому входу узла управления

t-ro яруса, входы узла управления

j-го яруса подключе ны к управляющим входам устройства.

где t - число ярусов устройства), Содержит элемент НЕ и два элемента И, причем первый вход узла управления подключен к первому входу первогб элёмёнта И, второй вход подключен к второму входу второго элемента И, третий вход подключен ко входу

элементаНЕ и первому входу :втд|)6г6

элемента И, зыход элемента НЕ подключен ко второму входу второго эле мёнта И. - - - -- -3.Устройство по П.1, о т л- и ч аю щ е е с я тем, что узел управления t-ro яруса (где t - число ярусов устройства) содержит,элемент НЕ и три элемента И, причем первый вход узла управления t-ro яруса соединен

с первым входом первого элемента И

iteffiSSS; :

и вторым входом третьего элемента И, второй вход узла соединен со вторым входом второго элемента И, третий вход узла соединен с первым входом третьего Элемента И, вход элемента НЕ подключен к пятому , выходу узла, к третьему входу узла и к первому входу второго Элемента И, выход элемента НЕ подключен соответственно ко второму входу первого элемента И и первому выходу узла управления.

Источники информации, принятые во внимание при экспертизе

S 85 Sff

Ъ8

67 О

89

68

|53 ГЧ

69

jsslи

70

0 Ш71

ШШ

72

т

г

73

Ё. W

74

65|G6

75

&

. ,r i-. . -.-r ; - i (€ ,

Авторы

Даты

1980-09-30—Публикация

1978-07-24—Подача