(|-1)-го операционного блока и четве тым информационным входом (i+l)-ro операционного блока, первый и второй информацион 1ые входы п-го операционного блока соединены с первым информационным входом процессора, третий, четвертый и пятый информационные входы h-ro операционного блока соединены соответственно с выходом второго коммутатора связи, выходом (h-l)-ro операционного блока и вторым информационным входом процессора вторые информационные входы первого и второго коммутаторов связи подключены к управляющему входу процессора отличающийся тем, что, с целью повьшения производительности; он содержит регистр множителя, регистр множимого, группу мультиплексоров данных, элемент ИЛИ и группу управлягацих мультиплексоров, управляющие входы которых соединены с вторым выходом выходного коммутатора, управляющие и информационные входы и выходы мультиплексоров данных группы подключены соответственно к второму выходу выходного коммутатора, первому информационному входу процессора и информационному входу регистра множителя, управляющий вход и выход которого соединены соответственно с вторым выходом выходного коммутатора и первым информационным входом первого управлякнцего мультиплексора, вход и выход элемента ИЛИ подключены соответственно к выходу регистра множителя и второму информационному входу входного кокмутатора, информационный и. управляющий входы регистра множимого соединены соответственно с первым информационным входом процессора и вторым выходом выходного коммутатора, . выходы регистра множимого и адресного мультиплексора подключены к первым и вторым информационным входам соответствукнцих управляющих мультиплексоров группы, а выходы управляющих мультиплексоров группы соединены с адресными входами соответствующих операционных блокЬв.

2. Процессор по п. 1,отлич ающийся тем, что операционный блок содержит четыре операционных модуля, включающих блок памяти, два адресных коммутатора, узел формирования переноса, регистр числа, регистр операнда и коммутатор данных, управляющий вход, первый, второй, третий и четвертый информационные входы которого соединены соответственно с управляющим входом, первый, вторым, третьим и пятым информационными входами блока, управляющий и информационный входы регистра операнда подключены соответственно к управляющему и первому информационному входам блока, управлякщий и информационный входы и выход .регистра числа соединены соответственно с управляющим входом блока, выходом коммутатор данных и информационным входом блока памяти, адресный вход которого подключен к адресному входу блока и выходам первого и второго адресных коммутаторов, первые информационные и управляющие входы которых соединен соответственно с адресным и управляющим входами блока, управляющий вход и выход блока памяти подключены соответственно к управляющему входу блока и информационному входу регистра операнда; вторые входы первого и второго адресных коммутаторов соединены соответственно с выходом регистра операнда и четвертым ин-формационным вгсодом блока, первый, второй и третий входы и выход узла формирования переноса подключены соответственно к четвертому информационному входу блока, выходу регистра операнда, выходу регистра числа и выходу ёлока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Устройство для табличной реализации многоместных логических функций | 1982 |

|

SU1019455A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Процессор для реализации операций над элементами расплывчатых множеств | 1985 |

|

SU1256010A1 |

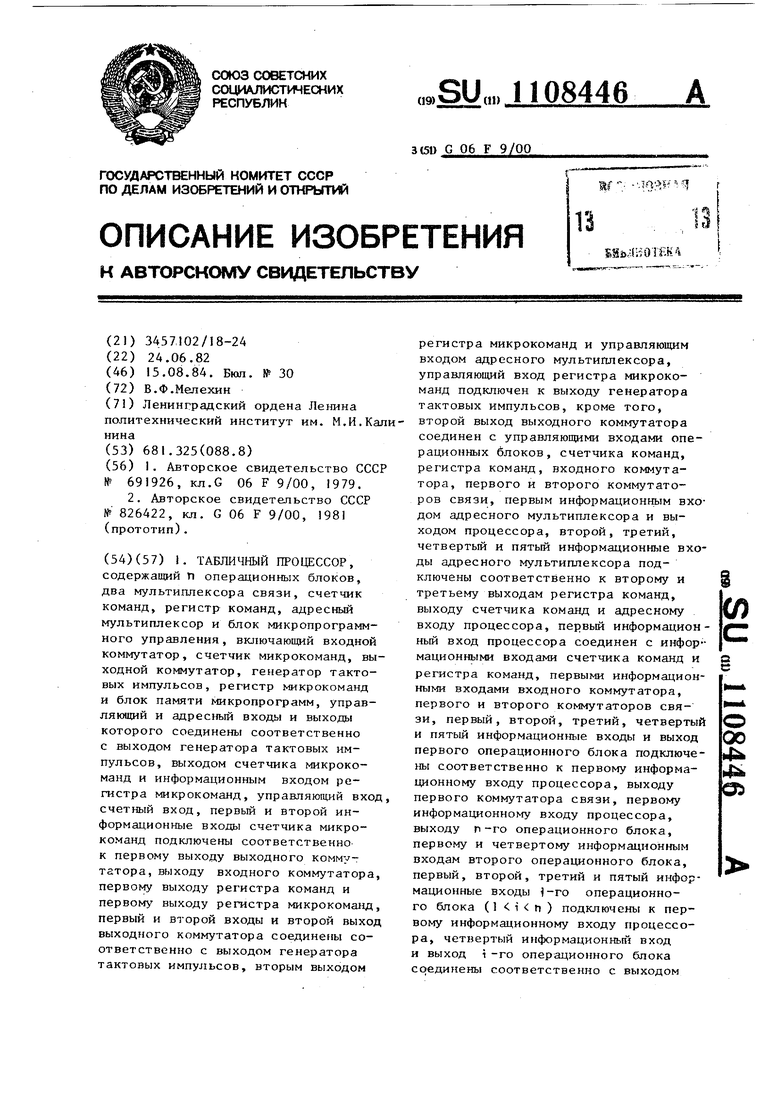

1. ТАБЛИЧНЫЙ ПРОЦЕССОР, содержащий п операционных блоков, два мультиплексора связи, счетчик команд, регистр команд, адресный fyльтиплeкcop и блок микропрограммного управления, включаюгщй входной коммутатор, счетчик микрокоманд, выходной коммутатор, генератор тактовых импульсов, регистр микрокоманд и блок памяти микропрограмм, управляющий и адресный входы и выхода которого соединены соответственно с выходом генератора тактовых импульсов, выходом счетчика микрокоманд и информационным входом регистра микрокоманд, управляющий вход, счетный вход, первый и второй информационные входы счетчика микрокоманд подключены соответственно к первому выходу выходного коммутатора, выходу входного коммутатора, первому выходу регистра команд и первому выходу регистра микрокоманд, первый и второй входы и второй выход выходного коммутатора соединены соответственно с выходом генератора тактовых импульсов, вторым выходом регистра микрокоманд и управляющим входом адресного мультиплексора, управляющий вход регистра микрокоманд подключен к выходу генератора тактовых импульсов, кроме того, второй выход выходного коммутатора соединен с управляющими входами операционных блоков, счетчика команд, регистра команд, входного коммутатора, первого и второго коммутаторов связи, первым информационным входом гщресного мультиплексора и выходом процессора, второй, третий, четвертый и пятый информационные входы адресного мультиплексора подключены соответственно к второму и третьему выходам регистра команд, (Л выходу счетчика команд и адресному входу процессора, первый информационС ный вход процессора соединен с информационнь1ми входами счетчика команд и о е регистра команд, первыми информационными входами входного коммутатора, первого и второго коммутаторов связи, первый, второй, третий, четвертый и пятый информационные входы и выход 00 4i первого операционного блока подключены соответственно к первому информаи О ционному входу процессора, выходу первого коммутатора связи, первому информационному входу процессора, выходу п-го операционного блока, первому и четвертому информационным входам второго операционного блока, первый, второй, третий и пятый информационные входы -го операционного блока

Изобретение относится к вычислительной технике.

Известно логическое эапоминаицее устройство, основными компонентами

которого являются одноразрядные блоки памяти, в которых табличным способом ялполняются логические преобразовашя, а переносы при суммировании

выявляются схемно-табличным способом 1,

Известен одноразрядные блок ло1-ической памяти 2. На базе таких блоков может быть построено устройство хранения и преобразования ин,формации, в котором помимо хранения информации, как в запоминающем устройстве, выполняются табличным способом все функции преобразования информации, характерные для арифметико-логических устройств.

Недостатком известных устройств являются Ьольшие затраты времени на выполнение операций умножения и деления, peaлизye « x с использова1шем операцией суммированиями сдвигов..

Цель изобретения - повьпнение производительности.

Цель достигается тем, что в табличный процессор, содержащий п операционных блоков, два мультиплексора связи, счетчик команд, регистр команд, адресный мультиплексор и блок микропрограммного управления, включающий входной коммутатор, счетчик микрокоманд, выходной коммутатор, генератор тактовых импульсов, регистр микрокоманд и блок памяти микропрограмм, упрАвлягаций и адресный входы и выходы которого соединены соответственно с выходом генератора тактовых импульсов, выходом счетчика микрокоманд, и информационным входом регистра микрокоманд управляющий вход, счетный вход, первый и второй информационные входы счетчика микрокоманд подключе соответственно к первому выходу выходного коммутатора, выходу входного коммутатора, первому выходу регистра команд и первому выходу регистра микрокоманд, первьм и второй входы и второй выход выходного коммутатора соединены соответственно с выходом генератора тактовых импульсов, вторым выходом регистра мирокоманд и управляющим входам адресного мультиплексора, управляющий вход регистра микрокоманд подключен к выходу генератора тактовых импульсов, кроме того, второй-выход выходного коммутатора соединен с управляющими входами операционных блоков, счетчика команд, регистра команд, входного коммутатора, певого и второго коммутаторов связи, первым информационным входом адресного мультиплексора и выходом процессора, второй, третий, четвертый и пятый информационтше входы адресного мультиплексора подключены соответственно к BTopobfy и третьему выходам регистра команд, выходу счетчика команд и адресному входу процессора, первый информационный вход процессора соединен с информационными входами счетчика команд и регистра команд, первыми информационными входами входного коммутатора, первого и второго коммутаторов связи, первый, второй, третий, четвертый и пятый информационные входы и выход первого операционного блока подключены соответственно к первому информационному входу процессора, выходу первого коммутатора связи, первому информационному входу процессора, выходу п-го операционного блока, первому и четвертому информационным входам второго операционного блока, первый, второй, третий и пятый информационные входы i-ro операционного блока () подключены к перво му информационному входу процессора, четвертый информационный вход и выход i-ro операционного блока соединены соответственно с выходом (i-l)-ro операционного блока и четвертым информационным входом (1-ь1)-го операционного блока, первый и второй информационные входы п-го операционного блока соединены с первым информационным входом процессора, третий, четвертый и пятый информационные входы п-го операционного блока соединены соответственно с выходом второго коммутатора связи, выходом (n-I)-ro операционного блока и вторым информационным входом процессора, вторые информационные входы первого и второго коммутаторов связи подключены к управляющему входу процессора, дополнительно введены регистр множителя, регистр множимого, группа мультиплексоров данных, элемент ШШ и группа управляюпщх мультиплексоров, управляющие входы которых соединены с вторым выходом выходного коммутатора, управлякицие и информационные входы и выходы мультиплексоров данных группы подключены соответственно к второму выходу выходного коммутатора, первому информационному входу процессора и информационному входу регистра множителя, управляющий вход и выход которого соединены соответственно с вторым выходом выходного KOMNfyraropa и первым информационным входом первого управляющего мультиплексора, вход и выход элемента ИЛИ подключены соответственно к выходу регистра множителя и второму информационному входу входного коммутатора, информационньй и управляющий входы регистра множимого соединены соответственно с первым информационным входом процессора и вторым выходом выходного коммутатора, выходы регистра множимого и адресного мультиплексора подключены к первым и вторым информационным входам соответствующих управляю1цих мультиплексоров группы, а выходы управляющих мультиплексоров группы соединены с адресными входами соответствующих операционных блоков.

Кроме того, операционный блок содержит четыре операционных модуля, включающих блок памяти, два адресных коммутатора, узел формирования переноса, регистр числа, регистр операнда и коммутатор данных, управляющий вход,первый, второй, третий и четвертый информационные входы которого соединены соответственно с управляющим входом, первым, вторым третьим и пятым информационными входами блока, управляющий и информационный входы регистра операнда подключены соответственно к управляющему и первому информационному входам блока, управляющий и информационный входы и выход регистра числа соединены соответственно с управляющим входом блока, выходом коммутатора данных и информационным входом блока памяти, адресный вход которого подключен -к адресному входу блока и выходам первого и второго адресных коммутаторов, первый информационные и управляющие входы которых соединены соответственно с адресным и управляняцим входами блока, управляющий вход и выход блока памяти подключены соответственно к управляющему входу блока и информационному входу регистра операнда, вторые входы первого и второго адресных коммутаторов соединены соответственно с выходом регистра операнда и четвертым информа1щонным входом блока, первый, второй и третий входы и выход узла формирования переноса подключены соответственно к четвертому информационному входу блока, выходу регист операнда, выходу регистра числа и входу блока.

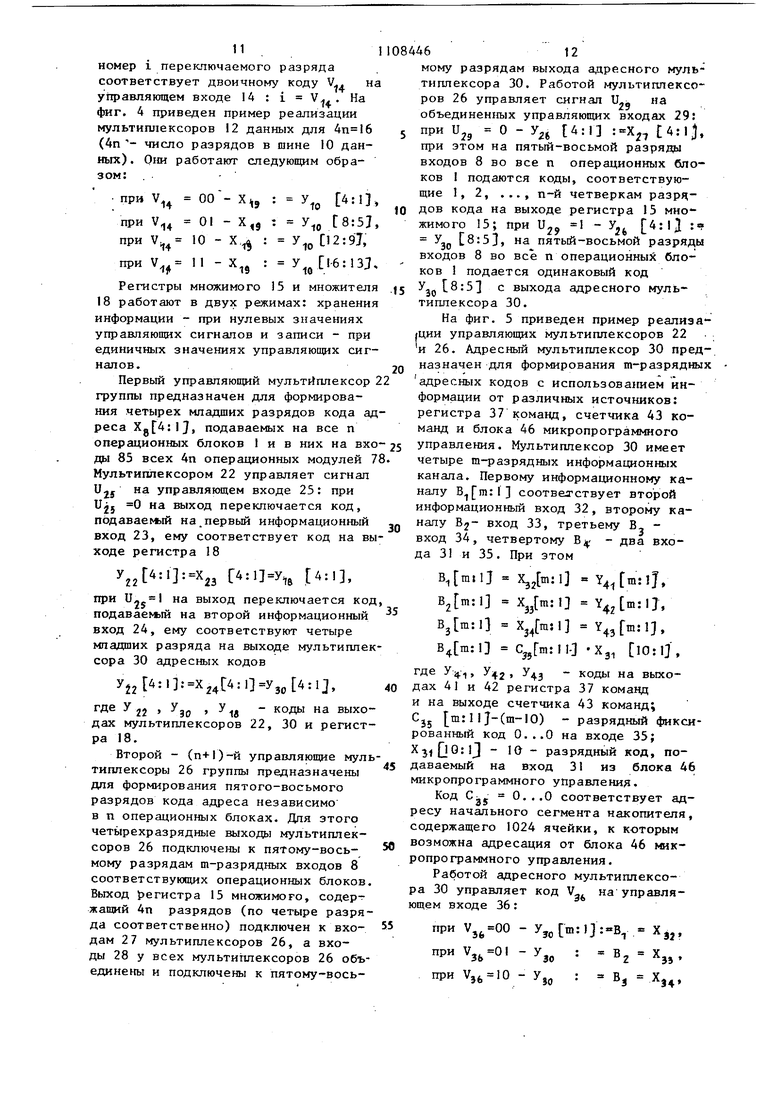

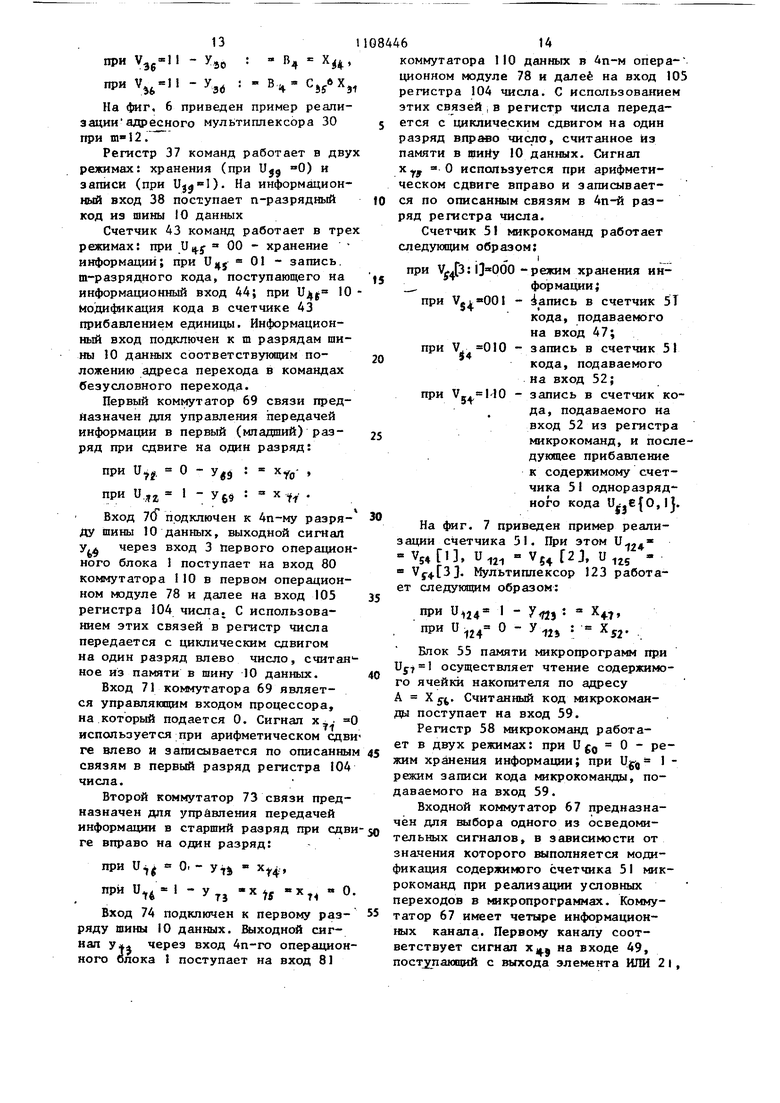

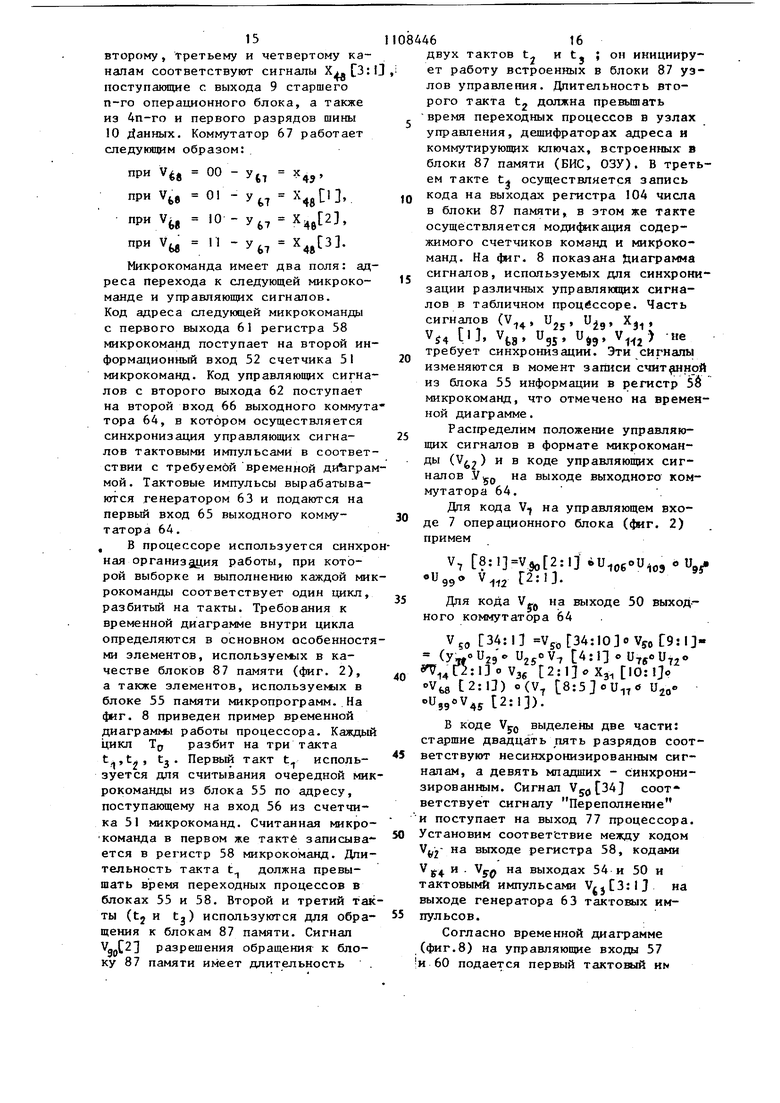

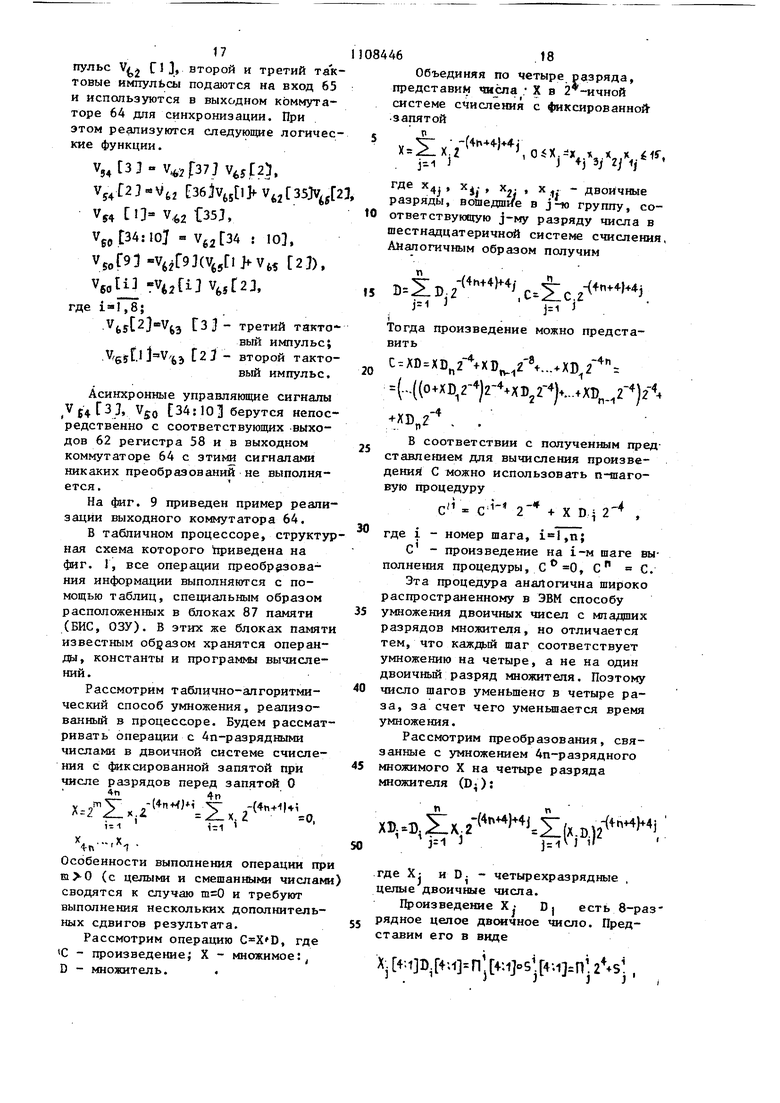

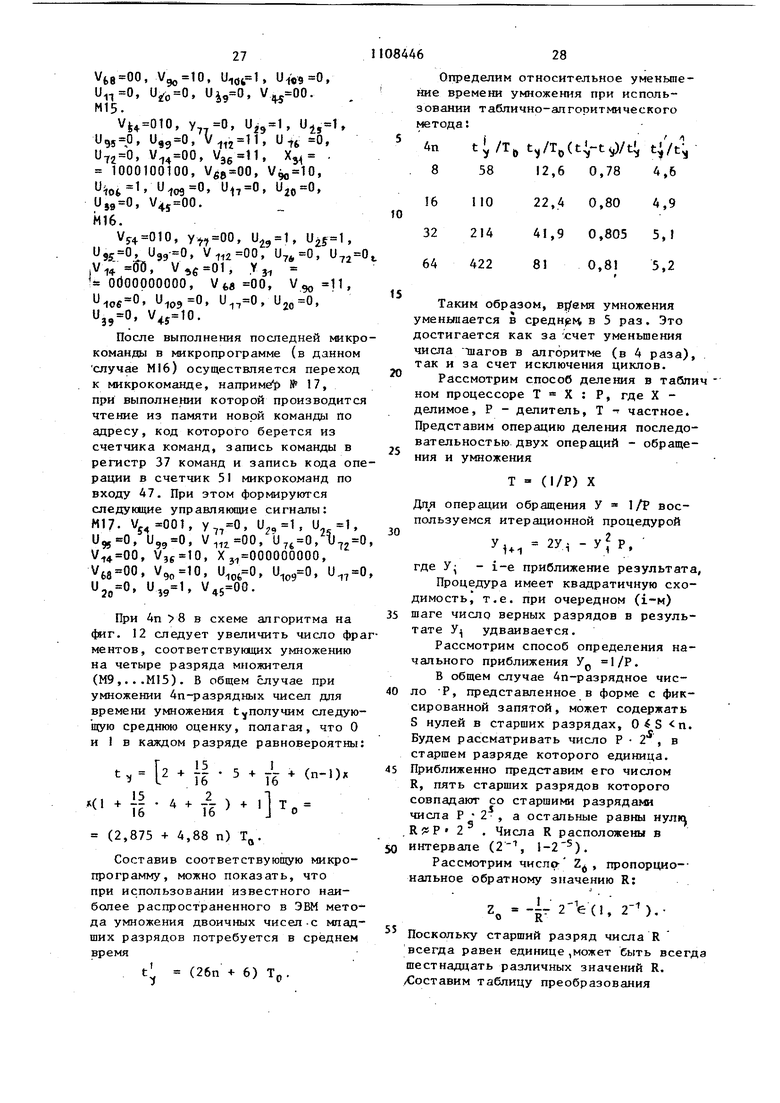

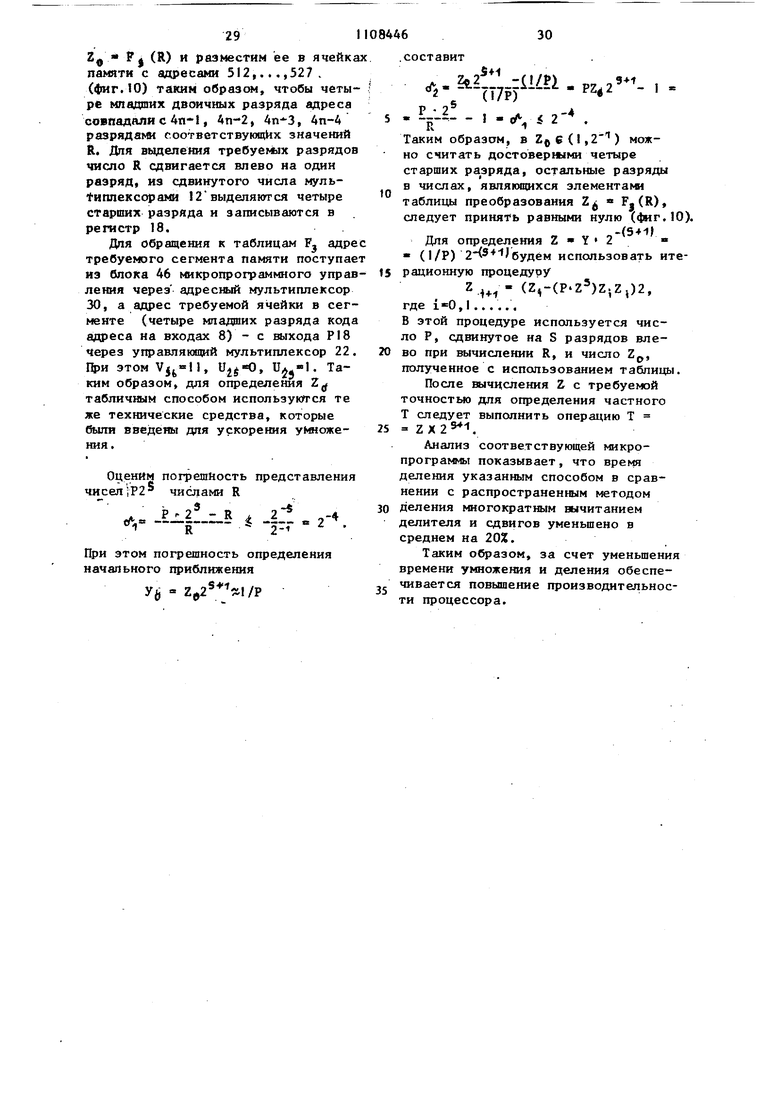

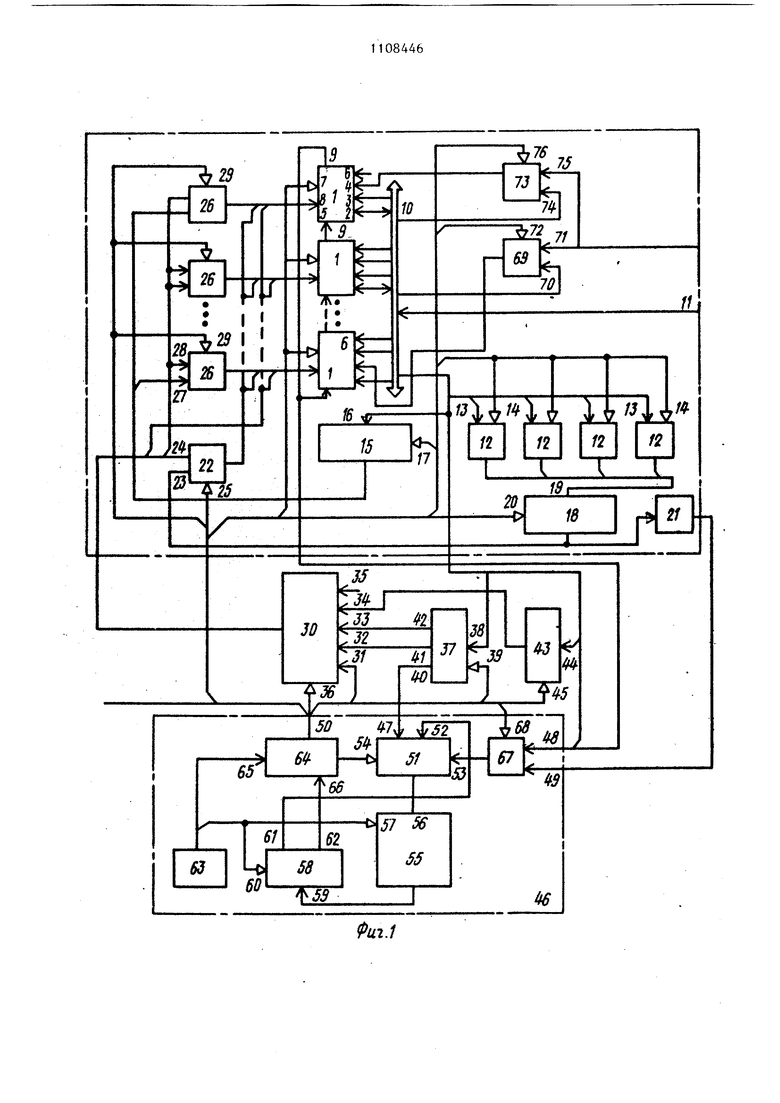

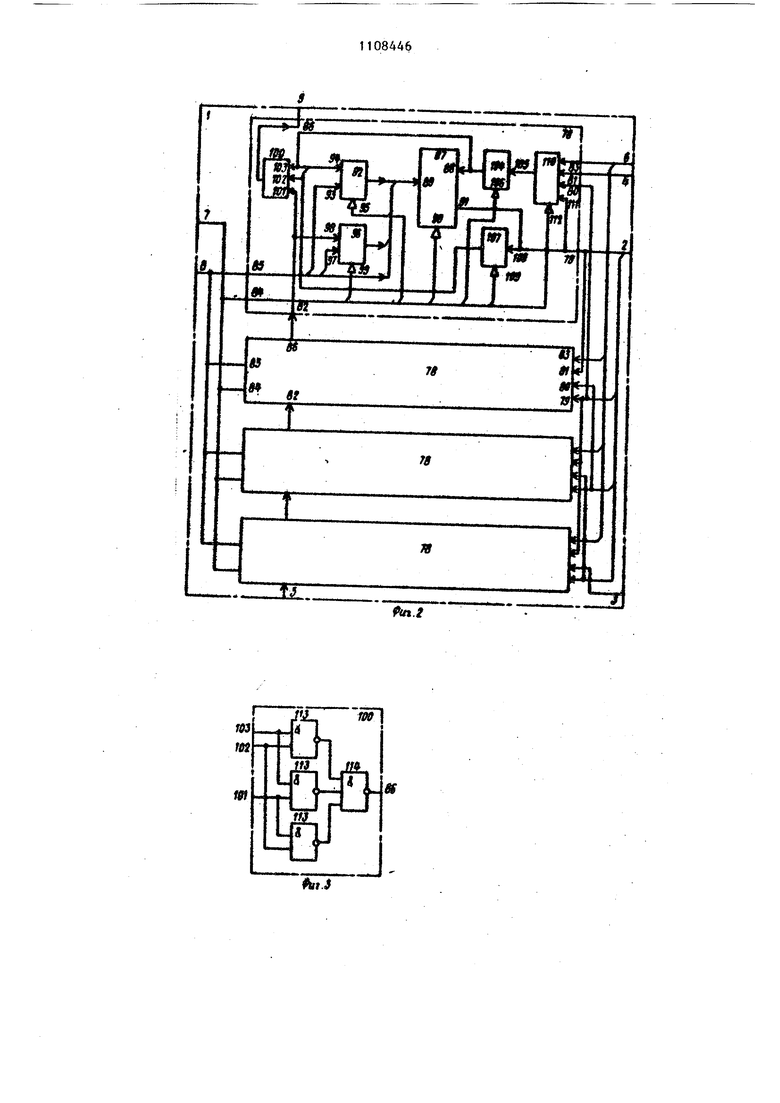

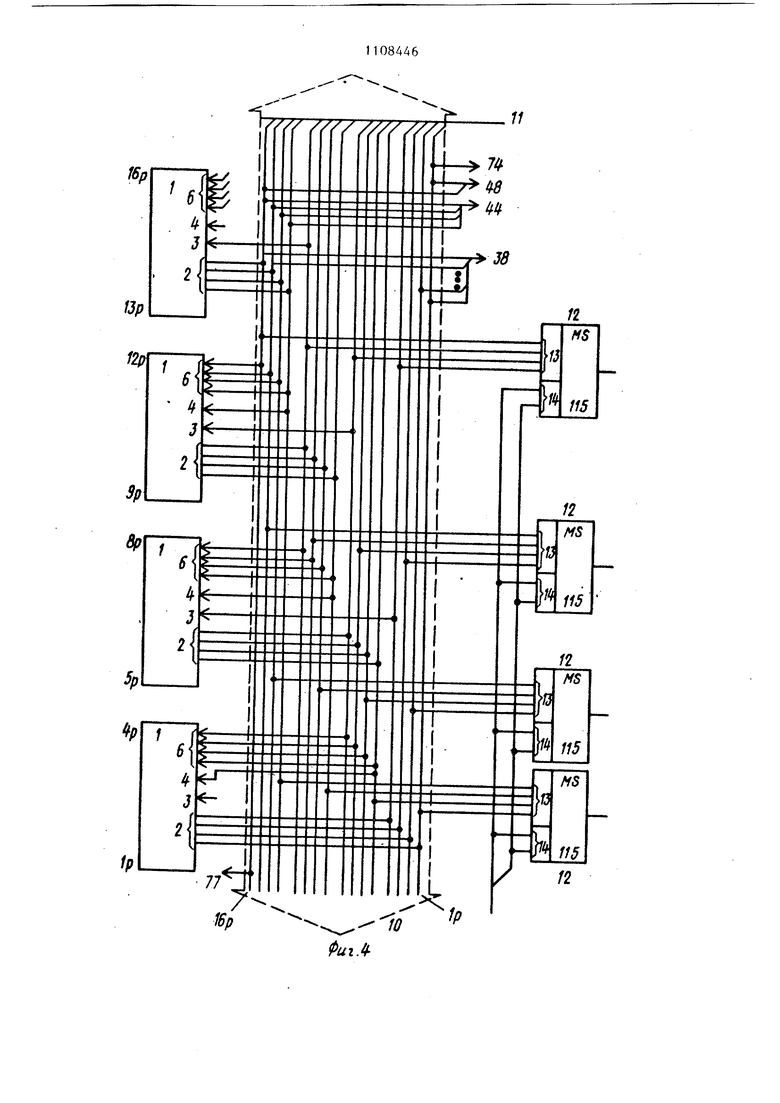

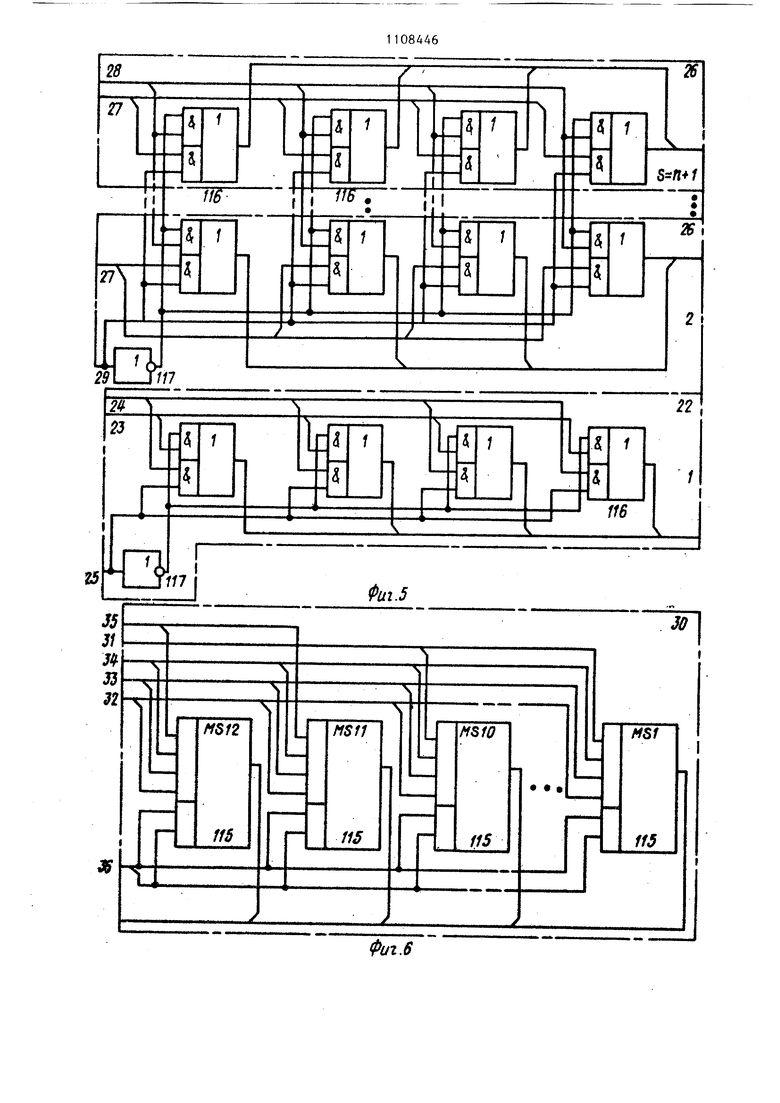

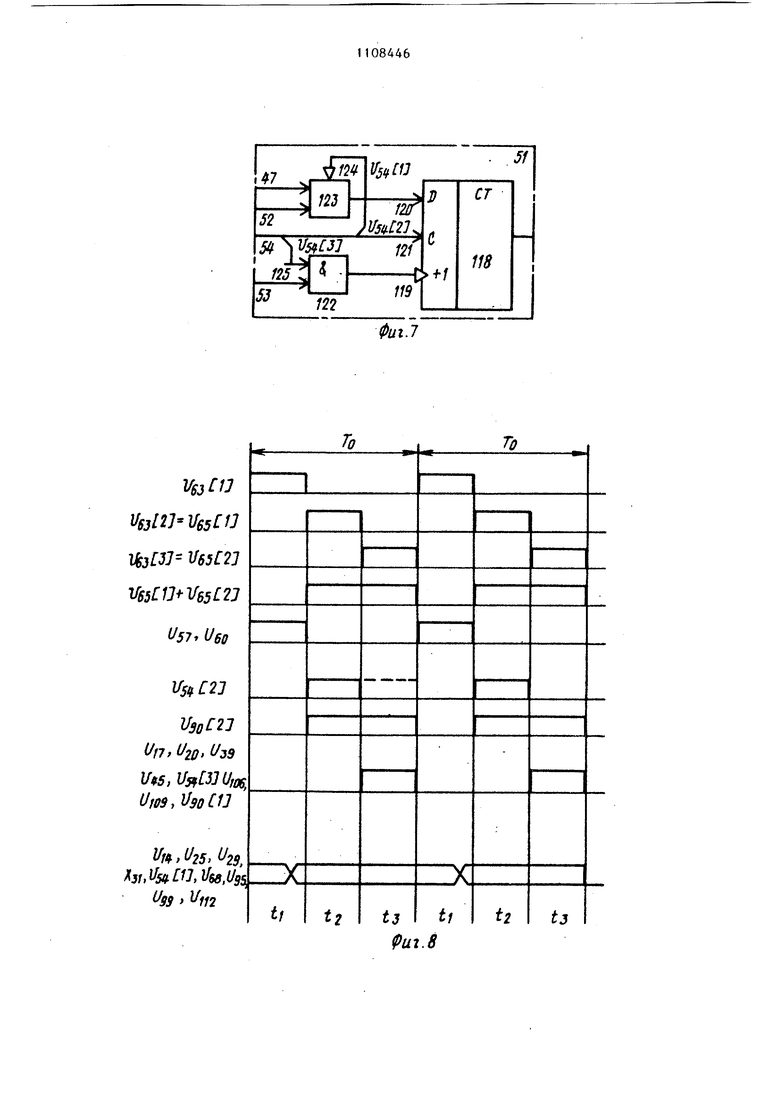

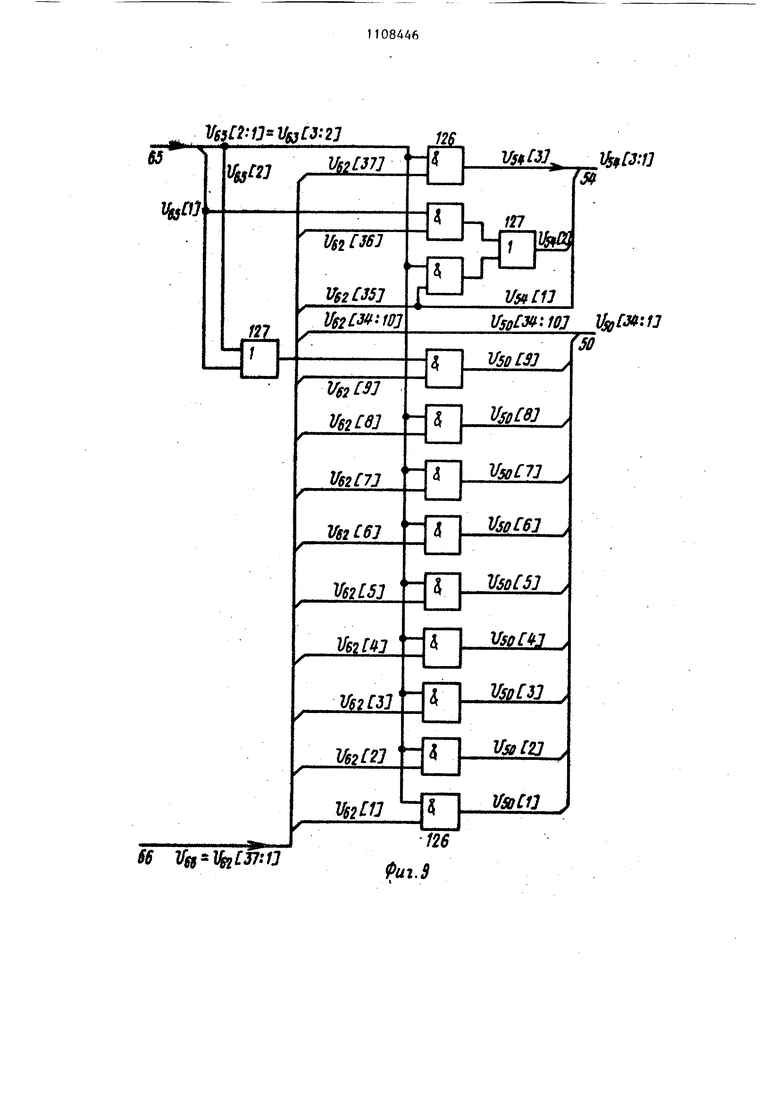

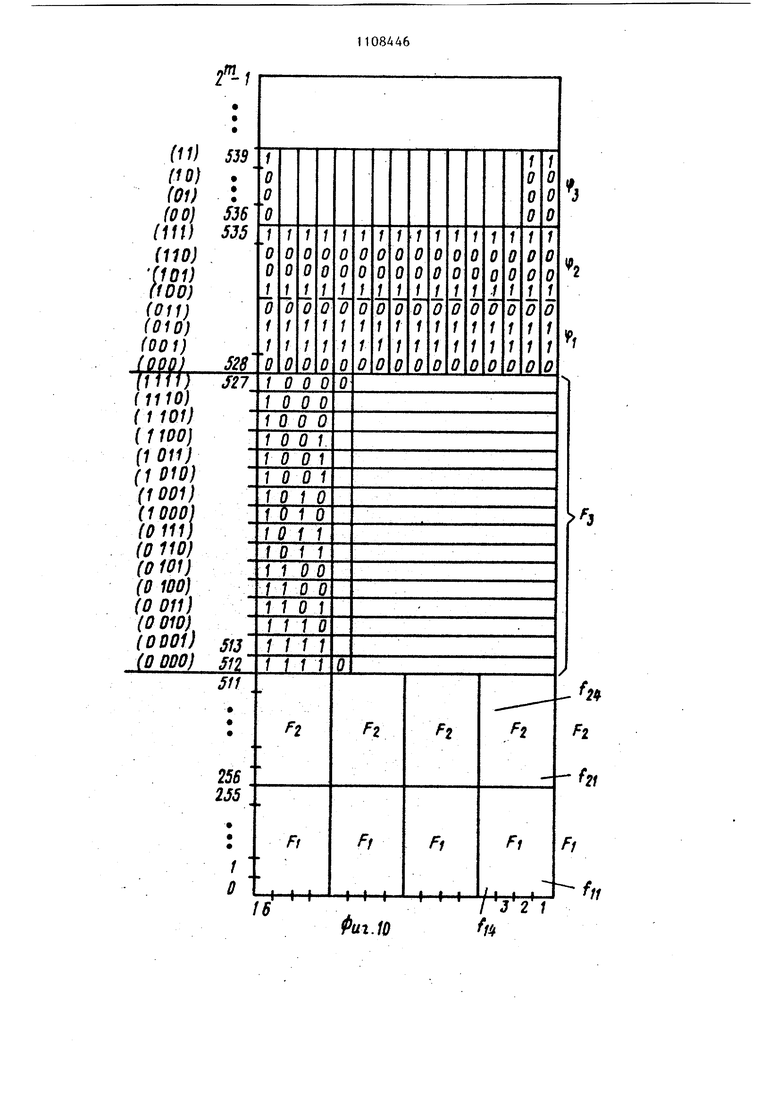

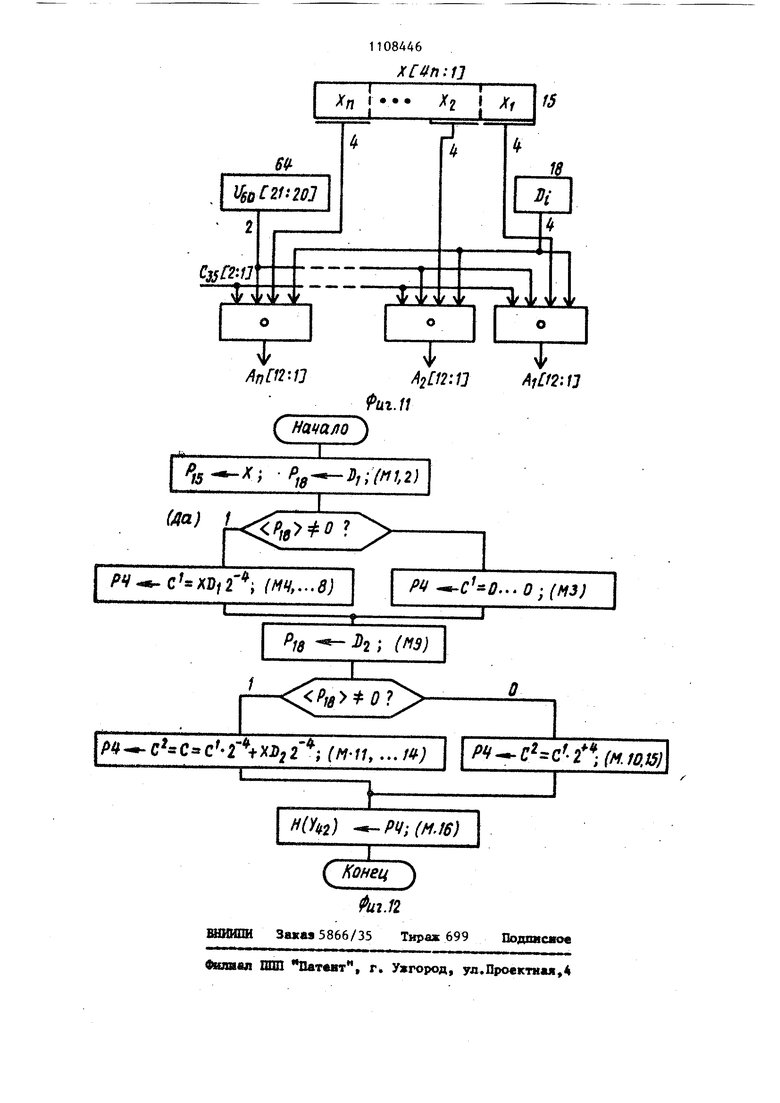

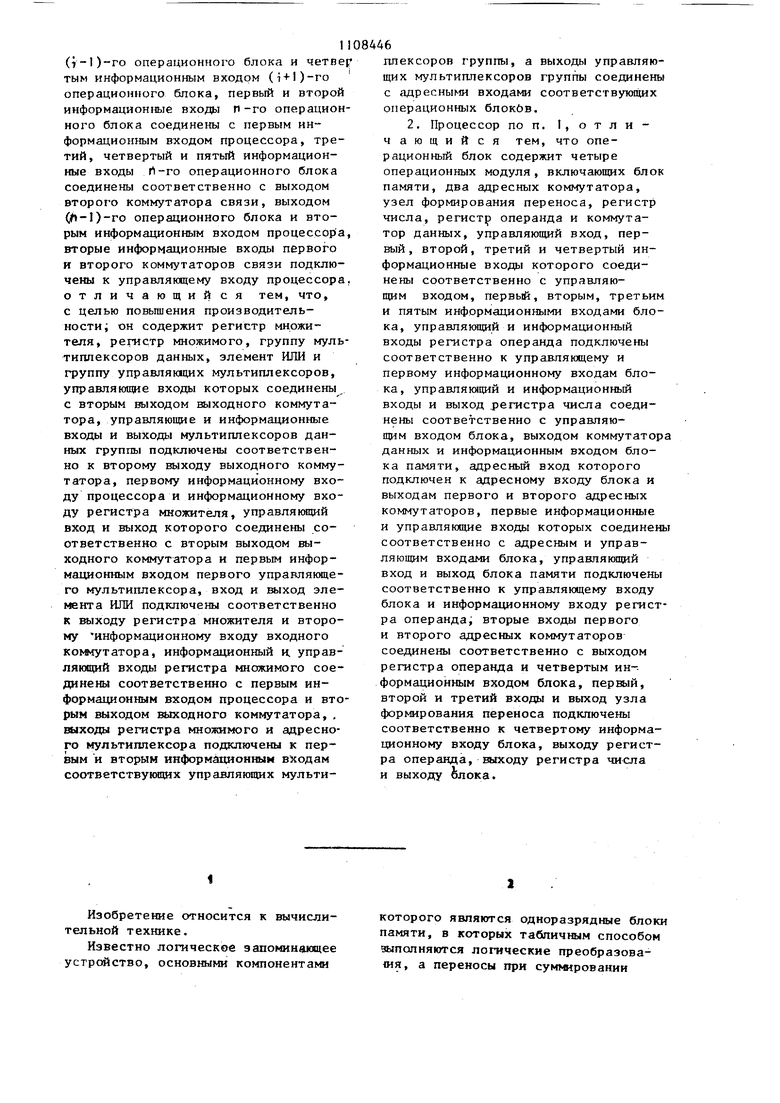

На фиг. I приведена структурная схема предлагаемого табличного процессора; па фиг. 2 - структурная схема операционного блока; на (. 3 - пример реализации узла формирования переноса; на фиг. 4 - пример реализации связей между блоками через шину данных; на фиг. 5 пример реализации группы управляющих мультиплексоров; на фиг. 6 пример реализации адресного мультиплексора; на фиг. 7 - пример реализации счетчика микрокоманд; на фиг. 8 - временная диаграмма работы процессора; на фиг. 9 - пример, реализации выходного коммутатора; на фиг. 10 - размещение таблиц в памяти; на фиг. 11 - схема преобразований для формирования адреса при обращении к таблицам умножения; на фиг. 12 - схема алгоритма умножения.

Устройство содержит операционньй блок 1,первый-пятый информационные входы 2-6, управляющий и адресньш входы 7 и 8, выход 9 операционного блока 1, шину 10 данных, первый информационный вход iI процессора, мультиплексоры 12 данных с информационными и управляющими входами 13 и 1Л, регистр 15 множимого с информационным и управляющим входами 16 и 17, регистр 18 множителя с информационным 19 и упраляющим 20 входами, элемент ИЛИ 21, первый управляющий мультиплексор 22 группы с первым и вторым информационными входами 23 и 24 и управляющим входом 25, второй - (п+1)-й управляющие мультиплексоры 26 группы с первым и вторым информационными входами 27 и 28 и управляюдим входом 29, адресный мультиплексор 30 с первым - пятым информационными входами 31-35 и управляющим входом 36, вход 35 является адресным входом процессора, регистр 37 команд с информационным и управляющим входами 3 и 39, первым, вторым и третьим выходами 40, 41 и 42, счетчик 43 команд с информационным и управляющим входами 44 и 45, блок 46 микро- программного управления с первым, вторым и третьим входами 47, 48 и 49 и выходом 50, счетчик 51 микрокоманд с первым и вторым информационными входами 47 и 52, счетным и управляю щим входами 53 и 54, блок 55 памяти микропрограмм с адресным и управлягацим входами 56 и 57, регистр 58 микрокоманд с информационным и управляющим входами 59 и 60, первым и вторым выходами 61 и 62,генератор 63 тактовых импульсов, выходной коммутатор 64 с первым и вторым вхо ми 65 и 66 , первым и вторым выходами 54 и 50, выход 50 коммутатора 64 является выходом блока 46 микропрограммного управления, входной комму.татор 67 с информационными входами 48, 49 и управляющим входом 68, первый коммутатор 69 связи с первым и вторым информационными входами 70 и 71 и управляющим входом 72, второй коммутатор 73 свя зи с первым и вторым информационными входами 74 и 75 и управляющими входами 76,. выход 77 процессора, операционный модуль 78 (фиг. 2), первый - пятый информационные входы 79-83, управляюощй и адресный входы 84 и 85, выход 86 модуля 78, блок 87 памяти (одноразрядный) с информационным, адресным и управляющим входами 88, 89 и 90 и выходом 91, первый адресный .коммутатор 92 с первым и вторым информационными входами 93 и 94 и управляю щим входом 95, второй адресный комм татор 96 с первым и -вторым информационными входами 97 и 98 и управляю щим входом 99, узел 100 формирования переноса с первым, вторым и третьим входами 101, 102 и 103, регистр 104 числа с информационным и управляющим входами 105 и 106, регистр 107 операнда с информационным и управляющим входами 108 и 109 коммутатор 1 10 данных с первым, вто рым, третьим и четвертым информацио ными входами 111, 80, 81 и 83и управляющим входом П2, элемент 2И-НЕ ИЗ (фиг.З), элемент ЗИ-НЕП4 селектор-мультиплексор I15 на четыре канала (фиг, 4 и 6), элемент 2И-2И-2ИЛИ 116 (фиг.5), элемент НЕ 117, счетчик 118 (фиг.7) со счет ным и информационным входами 119 и 120 и входом 121 синхронизации, элемент 2И 122 с входами 53 и 125, мультиплексор 123 на два канала с информационными входами 47 и 52 и управляющим входом 124, элемент И 126 (фиг. 9), элемент ИЛИ 127. Рассмотрим работу блоков операционного модуля 78 (фиг.2). Одноразрядный блок 87 памяти работает в трех режимах в зависимости от кода VjP t2 : 1 на управляющем входе 90} при Vgo 00 - режим хранения информации, при этом Уд R; при V 10 - режим чтения, при этом (A), А Xgj; при И режим записи, при этом Н(А): А Xgg, где Н(А) - содержимое ячейки накопителя с адресом А; Xog - переменная на входе 88, X gg - код на входе 89; у - переменная на выходе 91 (может принимать три значения - О, 1 и R, где R - состояние больщого выходного сопротивления). Код адреса X имеет m разрядов и получается из трех кодов XggCm: ХДт:4 еу cY 2:1, где Xo ni:43 - старшие т-3 разряда кода, подаваемого на вход 8; - сигнал на выходе второго адресного коммутатора 96; УМ код на выходе первого адресного коммутатора 92; - знак конкатенации. Первым адресньй коммутатор 92 переключает на выход код либо код Х-л 2:12 в зависимости от сигнала U « на управляющем входе 95:при 0,5 О - ,2Г2:1 Хдз 2:1 2:0, при Ug, 1 - Уэ,,, где y«gi 107 сигналы на выходах регистра 104 числа и регистра (07 операнда. Работой второго адресного комммутатора 96 управляет сигнал на управляющем входе 99: Ь ) 3. 99 - УЭ где Хд2 сигнал переноса из соседнего младшего разряда, поступающий на вход 82. Адресные коммутаторы 92 и 96 поз воляют осуществлять независимую адресацию ячеек накопителя в различных разрядах в пределах сегмента из четырех либо из восьми ячеек, что используется при табличной реализации поразрядных двухместных и трехместных логических функций. Узел 100 формирования переноса р ализует логическую функцию 1ог 403 юг юо сигнал переноса, подаваем где у с выхода узла 100 на выход 86 модуля 78; перено.с из предьодущего разряда; переменная на выходе реги loj ior ра 107 операнда (первое слагаемое); уJ - переменная на выходе реги Чо 104 ра 104 числа (второе ел гаемое), Пример реализации блока 100 прив ден на фиг. 3. Регистр 104 числа работает в дву режимах: при , О - режим хранения; при и ot режим записи при этом у : X10F°У 1 Аналогично для регистра 107 операнда: при и р5 О - режим хранения; при режим записи, при этом : х ов;У91 Коммутатор 110 данных работает следующим образом: Vii2 00 - УЦо при 10- у.. при --f-jo при - Через коммутатор ПОданных осуществляется связь информационного входа 105 регистра 104 числа с шиной 10 данных (фиг.). Шина 10 данных представляет собой 4п (соот ветственно числу разрядов процессора) проводников, иcпoльзye ыx дпя реапизац1ш связей между блоками. Для иллюстрации способа подключения шины данных к блокам 1 и 12 на фиг приведен пример при числе разрядов , Шина 10 данных подключена к первому информационному входу I1 процессора. Первый информационный вход 2 оп рацибнного блока 1 используется для ввода данных из шины 10 без сдвига второй информационный вход 3 - /щя ввода со сдвигом влево на один раз ряд, третий вход 4 - дпя ввода со сдвигом вправо на один разряд, чет вертый вход 5 - для сигнала переноса, пятый вход 6 - дпя ввода дан ных со сдвигом вправо на четыре разряда. Первый 2, второй 3, третий 4, четвертый 5 и пятый 6 информационные входы и выход 9 первого операционного блока I (фиг.1) под,ключены соответственно к первому информационному входу II процессора, выходу первого коммутатора 69 связи, первому информационному входу II процессора, выходу 9 п-го операционного блока I, первому 2 и четвертому 5 информационным входам второго операционного блока 1. Первый 2, второй 3, третий 4 и пятый 6 информационные входы i-ro операционного блока (I i п) подключены к первому информационному входу 11 процессора, четвертый информационный вход 5 и выход 9 i-ro операционного блока соединены соответственно с выходом 9 (i-l)-ro операционного блока и четвертым информационным входом 5 (i+l)-ro блока 1. Первьй-2 и второй 3 информационные входы п-го операционного блока 1 соединены с первым информационным входом 1I процессора. Третий 4, четвертый 5 и пятый 6 информационные входы п-го операционного блока 1 соединены соответственно с выходом второго коммутатора 73 связи, выходом 9 (n-l)-ro операционного блока 1 и вторым информационным входом процессора, на который подается фиксированный код 0. Рассмотрим работу блоков табличного процессора (фиг.1). Мультиплексоры12 данных предназначены дпя выделения четырех разрядов из 4п-разрядного кода на шине 10 данных и передачи вьщеленных разрядов на информационный вход 19 регистра 18. При этом выход первого мультиплексора 12 соответствует первому (младшему) разряду выделенного кода, а выход четвертого мультиплексора 12 - четвертому (старшему) разряду. В соответствии с этим i-й разряд информационного входа 13 j-ro мультиплексора 12 (X ,з : i) подключен к 1-му разряду шины 10 данных () в соответствии с выражением l 4H-j; , 1. ... (п-I); ,4. Каждый j-й из мультиплексоров 12 переключает на выход один (i-й) из разрядов кода , подаваемого а информацнонмлй вход 13, при этом номер i переключаемого разряда соответствует двоичноьту коду V. на у гфавляющем входе 14 : i V, , На фиг, 4 приведен пример реализации мультиплексоров 12 данных для (4п - число разрядов в шине 10 данных). 01Ш работают следуюпщм образом: .при V 00 - при V 01 - Х,5 : 8:5 при V 10 - Х, : 12:97, при V 11 - Х,5 : , Регистры множимого 15 и множителя 18 работают в двух режимах: хранения информации - при нулевых значениях управляющих сигналов и записи - при единичных значениях управляющих сигналов. Первый управляющий мультиплексор группы предназначен для формирования .четырех младших разрядов кода ад реса , подаваемых на все п операционных блоков 1 и в них на вхо ды 85 всех 4п операционных модулей Мультиплексором 22 управляет сигнал на управляющем входе 25: при Ujj 0 на выход переключается код, подаваемый на,первый информационный вход 23, ему соответствует код на вы ходе регистра 18 на выход переключается код подаваемзш на второй информационный вход 24, ему соответствуют четыре младших разряда на выходе мультиплек сора 30 адресных кодов . где У 22 , УЗР , - коды на выходах мультиплексоров 22, 30 и регистра 18. Второй - (п+1)-й управляющие муль типлексоры 26 группы предназначены для формирования пятого-восьмого разрядов кода адреса независимо в п операционных блоках. Для этого четырехразрядные выходы мультиплексоров 26 подключены к пятому-восьмому разрядам т-разрядных входов 8 соответствующих операционных блоков Выход регистра 15 множимого, содер жашкй 4п разрядов (по четыре разряда соответственно) подключен к входам 27 мультиплексоров 26, а входы 28 у всех мультитшексоров 26 объединен и подключены к пятому-восьмому разрядам выхода адресного мультиплексора 30. Работой мультиплексоров 26 управляет сигнал 11, на объединенных управляющих входах 29: при U.g О - 4:1 при этом на пятый-восьмой разряду входов 8 во все п операционных блоков I подаются коды, соответствующие 1, 2, ..., п-й четверкам разрядов кода на выходе регистра 15 множимого 15; при 1 У. 8:53, на пятый-восьмой разряды входов 8 во всё п операционных блоков 1 подается одинаковый код У, 8:5 с выхода адресного мультиплексора 30. На фиг. 5 приведен пример реализа/ции управляющих мультиплексоров 22 и 26. Адресный мультиплексор 30 пред-. назначен для формирования т-разрядных адресных кодов с использованием информации от различных источников: регистра 37 команд, счетчика 43 команд и блока 46 микропрограммного управления. Мультиппексор 30 имеет четыре т-разрядных информационных канала. Первому информационному каналу соответствует второй информационный вход 32, второму каналу Bj- вход 33, третьему В, вход 34, четвертому - два входа 31 и 35. При этом В, т. и У4Дт: |, вДт: Xjm:l , , Cjjfm:. -Xj, lOrlj, где У:,, « 43 коды на выходах 41 и 42 регистра 37 команд и на выходе счетчика 43 команд; Cjj m:llJ-(m-IO) - разрядный фиксированный код 0...0 на входе 35; - Ш - разрядный код, поаваемый на вход 31 из блока 46 микропрограммного управления. Код Cjj О...О соответствует адесу начального сегмента накопителя, одержащего 1024 ячейки, к которым возможна адресация от блока 46 микопрограммного управления. Работой адресного мультиплексоа 30 управляет код V на управлящем входе 36: -y,Jm:lJ:«B, Х,,, при V-, 00 при - УЗ„ -У,„ : В. Х„. 35 при V5t IO - У„ Bj Xj,

при -

Д

B4-Cj,«X,, при V,,-ll -УЗЙ

На фиг, 6 приведен пример реализации адресного мультиплексора 30 при .

Регистр 37 команд работает в двух режимах: хранения (при Ujj 0) и записи (при ). На информационный вход 38 поступает п-разрядный код из шины 10 данных

Счетчик 43 команд работает в трех режимах: при 00 - хранение информации; при 01 - запись, т-разрядиого кода, поступающего на информационный вход 44; при Uj Ю модификация кода в счетчике 43 прибавлением единицы. Информационный вход подключен к m разрядам шины 10 данных соответствукящм положению адреса перехода в командах безусловного перехода.

Первый коммутатор 69 связи предйазначен для управления передачей информации в первый (младший) разряд при сдвиге на один разряд:

при . О - у : - ху(,- , при U.,jj I - yjd : X Yy .

Вход 7tf подключен к 4п-му разряДУ шины 10 данных, выходной сигнал УХ через вход 3 первого операционного блока 1 поступает на вход 80 коммутатора 110 в первом операционном модуле 78 и далее на вход 105 регистра 104 числа. С использованием этих связей в регистр числа передается с циклическим сдвигом на один разряд влево число, считанное из памяти в шину 10 данных.

Вход 71 коммутатора 69 является управлякпщм входом процессора, на который подается 0. Сигнал х. 0 используется при арифметическом сдви ге влево и записывается по описанным связям в первый разряд регистра 104 числа.

Второй коммутатор 73 связи предназначен для управления передачей информации в старший разряд при сдви ге вправо на один разряд:

и в 0. - - х,

« I - у

is

1

тз

Вход 74 подключен к первому раз- 55 ряду шины 10 данных, входной сигнал yjj через вход 4п-го операционного блока 1 поступает на вход 81

коммутатора 110 данных в 4п-м операционяом модуле 78 и далее на вход 10 регистра 104 числа. С использованием этих связей,в регистр числа передается с циклическим сдвигом на один разряд вправо число, считанное из памяти в щийу 10 данных. Сигнал X уу «О используется при арифметическом сдвиге вправо и записывается по описанным связям в 4п-й разряд регистра числа.

Счетчик 51 микрокоманд работает

спедуюпщм образом:

I

при У-/3:1 «000 -режим хранения ии формации;

при - Запись в счетчик 5Т кода, подаваемого на вход 47;

при V. 00 - запись в счетчик 51 кода, подаваемого на вход 52;

при V,. MO - запись в счетчик кода, подаваемого на вход 52 из регистра микрокоманд, и послдующее прибавление к содержимому счетчика 51 одноразрядного кода U,e|0,lj

На фиг. 7 приведен пример реализации счетчика 51. При этом - Vs,ri, U,j, , и,„ V5-4.133. Мультиплексор 123 работает следующим образом:

при Ui24 - У«Э Х« при U;,24 ° «4 52Блок 55 памяти микропрограмм при осуществляет чтение содержимого ячейки накопителя по адресу А Ху. Считанный код микрокоманды поступает на вход 59.

Регистр 58 микрокоманд работает в двух режимах: при U gg О - режим хранения информации; при 1 режим записи кода микрокоманды, подаваемого на вход 59.

Входной коммутатор 67 предназначен для выбора одного из осведомительных сигналов, в зависимости от значения которого выполняется модификация содержимого счетчика 5I микрокоманд при реализации условных переходов в микропрограммах. Коммутатор 67 имеет четыре информационных канала. Первому каналу соответствует сигнал на входе 49, пост гпающий с выхода элемента ИЛИ 2 I 15 второму, третьему и четвертому каналам соответствуют сигналы поступающие с выхода 9 старшего п-го операционного блока, а также из 4п-го и первого разрядов шины 10 Данных. Коммутатор 67 работает следующим образом: при 00 - у , при 01 - у . при «О - У 67 при V 11 - у . Микрокоманда имеет два поля: ад реса перехода к следующей микрокоманде и управляющих сигналов. Код адреса следующей микрокоманды с первого выхода 61 регистра 58 микрокоманд поступает на второй ин формационный вход 52 счетчика 5I микрокоманд. Код управляющих сигна лов с второго выхода 62 поступает на второй вход 66 выходного коммут тора 64, в котором осуществляется синхронизация управляющих сигналов тактовыми импульсами в соответ ствии с требуемой временной мой. Тактовые импульсы вырабатываются генератором 63 и подаются на первый вход 65 выходного коммутатора 64. , В процессоре используется синхр ная организд ия работы, при которой выборке и выполнению каждой ми рокоманды соответствует один цикл разбитый на такты. Требования к временной диаграмме внутри цикла определяются в основном особенност ми элементов, иcпoльзye ыx в качестве блоков 87 памяти (фиг. 2), а также элементов, используеьых в блоке 55 памяти микропрограмм. На фиг. 8 приведен пример временной диаграм работы процессора. Кажды цикп Тр разбит на три такта t..,t, tj . Первый такт t используется для считывания очередной ми рокоманды из блока 55 по адресу, поступающему на вход 56 из счетчика 51 микрокоманд. Считанная микро комаида в первом же такте записыва ется в регистр 58 микрокоманд. Дли тельность такта t должна превышать время переходных процессов в блоках 55 и 58. Второй и третий та ты (tj и t) используются для обра щения к блокам 87 памяти. Сигнал п«С21 разрещения обращения к блоку 87 памяти имеет длительность 16 6 двух тактов t и t, ; он иницнирует работу встроенных в блоки 87 узлов управления. Длительность второго такта t- должна превьШ1ать время переходных процессов в узлах управления, дешифраторах адреса н коммутирующих ключах, встроеннык в блоки 87 памяти (БИС, ОЗУ). В третькода на выходах регистра 104 числа в блоки 87 памяти, в этом же такте осуществляется модификация содержимого счетчиков команд и микрокоманд. На фиг. 8 показана Диаграмма сигналов, используемых для синхронизации различных управляющих сигналов в табличном процессоре. Часть сигналов (V, Uj , , Х , из. Ugs W ) -не требует синхронизации. Эти сигналы изменяются в момент записи из блока 55 информации в регистр 5Й микрокоманд, что отмечено на временной диаграмме. Расгфеделим положение управляющих сигналов в формате микрокоманды () и в коде управляющих сигналов на выходе выходного коммутатора 64. Для кода V на управляющем входе 7 операционного блока (фиг. 2) примем V7 ,,,oU,,oU,j. 5о1 12: п. V,,2 Для кода Vf на выходе 50 выход-ного коммутатора 64 Vgo 34: П V5j34:10 oVyoC9 lJ (yj °U23- 4: HO UTS 072° 2:13оХзЛ10:1 Vfee 2:13) o(v 8:5 cUi7e Ujo -UjgOV y 2:1). В коде выделены две части: старшие двадцать пять разрядов соответствуют иесинхроиизированным сигналам, а девять младших - синхронизированным. Сигнал соот ветствует сигналу Переполнение поступает на выход 77 процессора. становим соответствие между кодом на выходе регистра 58, кодами Vg. и . Vj. на выходах 54 и 50 и актовыми импульсами на выходе генератора 63 тактовых импульсов. Согласно временной диаграмме (фиг.8) на управляющие входы 57 60 подается первый тактовый ни 17 пульс С, второй и третий так товые импульсы подаются на вход 65 и используются в выходном коммутаторе 64 дпя синхронизации. При этом реализуются следующие логичес кие функции. V54t3:i- ). У54Г2: -Vt2 36JVt5tl 35) V Cl 135J, Vpp 34:loJ - : 10, Vsof9J-V r9J( 2), VggU . где i-1,8; r3iJ- третий такто вый импульс; . 1.2 J - второй такто вый импульс. Асинхронные управляющие сигналы ,, Vj{j 34:10 берутся непос редственно с соответствующих выходов 62 регистра 58 и в выходном коммутаторе 64 с этиш сигналами никаких преобразований не выполняНа фиг. 9 приведен пример реали зации выходного коммутатора 64. В табличном процессоре, структу ная схема которого приведена на фиг. J, все операции преобр зования информации выполняются с помощью таблиц, специальным образом расположенных в блоках 87 памяти (БИС, ОЗУ). В этих же блоках памят известным o6ga3OM хранятся операнды, константы и программ вычислений. Рассмотрим таблично-алгоритмический способ умножения, реализованный в процессоре. Будем рассмат ривать операции с 4п-разрядными числами в двоичной системе счисления с 4 1ксированной запятой при числе разрядов перед запятой О 4п4п ..Z,.,f--w ..-, n-SОсобенности выполнения операции пр (с целыми и смешанными числам сводятся к случаю и требуют выполнения нескольких дополнительных сдвигов результата. Рассмотрим операцию , где С - произведение; X - множимое:, D - множитель.. 46.18 Объединяя по четыре разряда, представим шспл ; X в 2 -ичной системе счисления с фиксированной запятой { 1 - 4- 4Х:г2 Х.2 -VS/Z N, . Ггде х , xjy , х. , X,,. - двоичные разряды, вошедшие в j-ю группу, соответствующую j-му разряду числа в шестнадцатеричной системе счисления, Диалогичным образом получим ),,с-±с. it J Тогда произведение можно представитьC--;(D XD,)2-V...XD,2- (...(()z-nXD22-)4...-fXB.,2) D,2- , . В соответствии с полученным представлением для вычисления произведений С можно использовать п-шаговую процедуру с - 2 + X а 2 , где i - номер шага, ,n; с - произведение на i-м шаге выполнения процедуры, С 0, с С. Эта процедура аналогична широко распространенному в ЭВМ способу умножения двоичных чисел с мпадаих разрядов множителя, но отличается тем, что каждый шаг соответствует умножению на четыре, а не на один двоичный разряд множителя. Поэтому число шагов уменьшена в четыре раза, за счет чего уменьшается время умножения. Рассмотрим преобразования, связанные с умножением 4п-разрядного множимого X на четыре разряда множителя (D): xv..tx.(,. r- где X: и DJ - четырехразрядные , целые двоичные числа. Щзоизведение Х.- D| есть 8-разрядное целое двсжчное число. Представим его в виде П «4 „i X. 4-..f4;i3 n: f:i o5 4;i3 n; 2%s; .

где П: - старшие четыре разряда; S - младшие четыре разряда

произведения.

Используя полученное представление получим

ЛС.(п2 5М2 2

,-4„-(п+)+Я

,-(4h.+)

Z

i 2-(

г- J

П 52

Отдельные (j-e) .шестнадцатиричные разряды чисел П и S полностью определяются значением четырехразрядного кода DJ и соответствующего, четырехразрядного кода Х- и могут быть представлены как систем 1 логических функций

Г,(ОД4:П, ); F2(, ),

где ,n;

F, F- - системы из четырех восминестьых логических функций

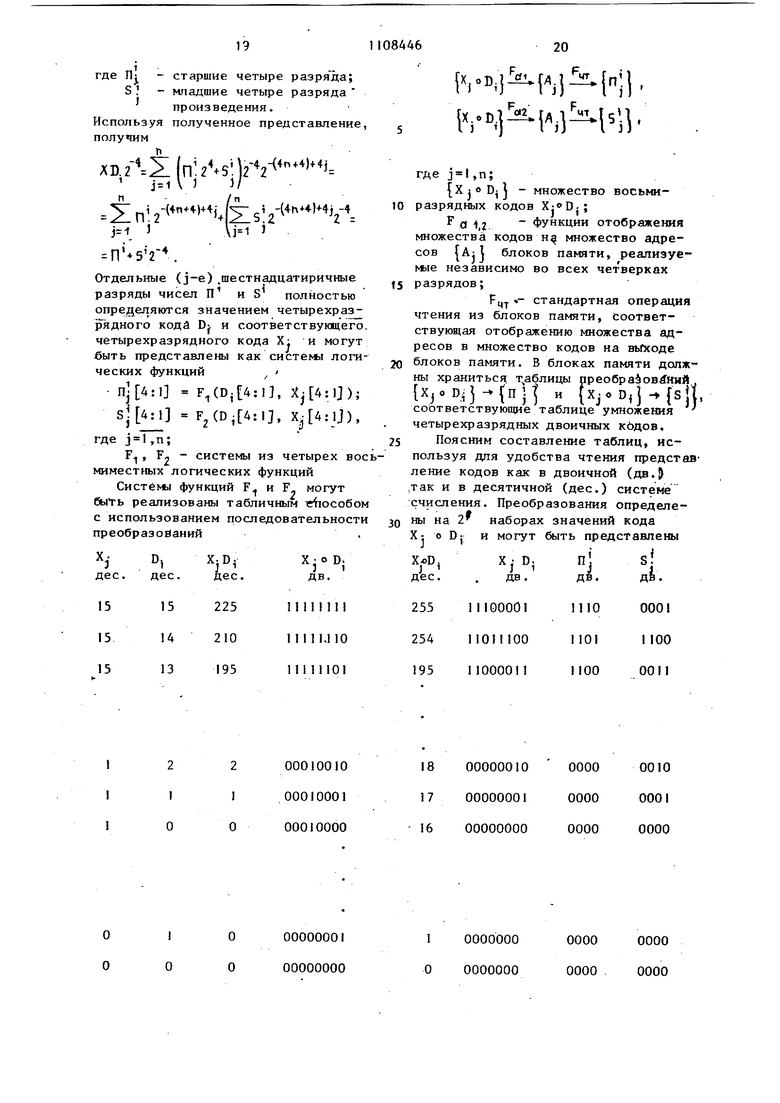

СистеМ) функций F и F- могут быть реализованы табличным Teiioco6oM с использованием последовательности преобразований

X . о DJ

D

XjDf

дв. дес. дес.

11111 III

225

15

15

210

14 13 111 11101 195

о о

1 О

0000000I 00000000

(.

t«i°.-lM-liV

где ,n;

{XjoDjJ - множество восьми0 разрядных кодов X-oD-;

Д 1,2 функции отображения множества кодов н множество адресов А; блоков памяти, реализуемые независимо во всех четверках

5 разрядов;

Fq-f - стандартная операция чтения из блоков памяти, соответствующая отображению множества адресов в множество кодов на вьГходе

0 блоков памяти. В блоках памяти должны храниться т,аблицы преобразований XjoD j-fnjI и (, соответствующие таблице умножения четырехразрядных двоичных кодов.

5Поясним составление таблиц, используя для удобства чтения представление кодов как в двоичной (дв.) .так и в десятичной (дес.) системе счисления. Преобразования определены на 2 наборах значений кода Х-, о D: и могут быть представлены

J X.D

1

XJ.D.

дв.

дв.

дв. дес.

11100001

0001

то

255

1100

I 101

11011100 ООП 1100 I1000011

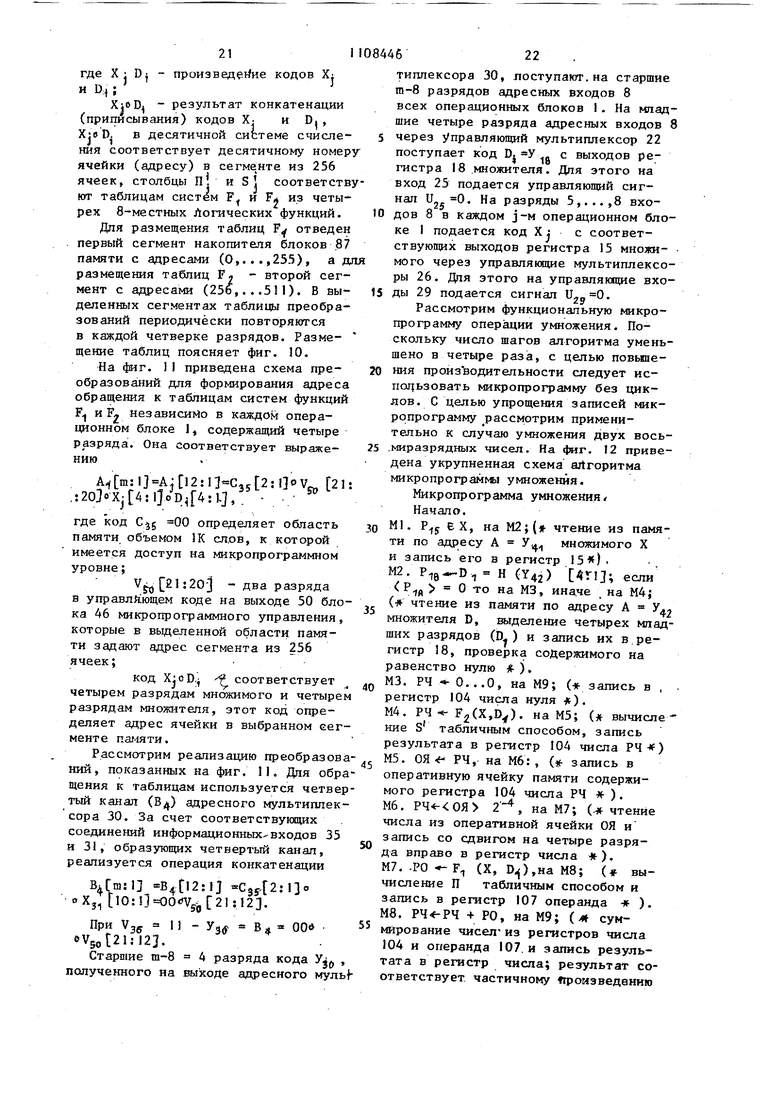

I 0000000 0000 0000 о 0000000 0000 0000 где X; D: - проиэведе ие кодов X - результат конкатенации Xj-Di и DI (приписывания) кодов X X:eD. в десятичной системе счисления соответствует десятичному номер ячейки (адресу) в сегме,Нте из 256 ячеек, столбцы п и Sj соответств ют таблицам систем F и Fj из четырех 8-местных Логических функций. Для размещения таблиц F отведен . первый сегмент накопителя блоков .87 памяти с адресами (О,...,255), а д размещения таблиц F, второй сегмент с адресами (256,...5П). В выделенных сегментах таблицы преобразований периодически повторяются в каждой четверке разрядов. Размещение таблиц поясняет фиг. 10. На фиг. 11 приведена схема преобразовавши для формирования адреса обращения к таблицам систем функций F и F независимо в каждом операционном блоке 11 содержащий четыре разряда. Она соответствует выражениюA m:lJ Ajri2 l C35t2:a«V 21 .J, - . где код Cjg 00 определяет область памяти объемом К слов, к которой имеется доступ на микропрограммном уровне; Vg 21;20j - два разряда в управляющем коде на выходе 50 бло ка 46 микропрограммного управления, которые в выделенной области памяти задают адрес сегмента из 256 ячеек; код XjoD. f соответствует четырем разрядам множимого и четыре разрядам множителя, этот код определяет адрес ячейки в выбранном cei- менте паг4яти. Рассмотрим реализацию преобразов ний, показанных на фиг. II. Для обр щения к таблицам используется четве тый канал (В) адресного мультиплек сора 30. За счет соответствующих соединений информационных-входов 35 и 31, образующих четвертый канал, реализуется операция конкатенации BiCmsU B4tl25lJ «Сзу, оХ, 10: ЮО«ПГ5,. При Уз5 И - cV5ot2l:123. Старшие т-8 4 разряда кода У полученного на выходе адресного мyл 1 6 типлексора 30, лоступакгг. на старшие га-8 разрядов адресных входов 8 всех операционных блоков I. На младшие четыре разряда адресных входов 8 через Управляющий мультиплексор 22 поступает код D, У., с выходов ре. - г, гистра 18 .множителя. Дпя этого на вход 25 подается управляющий . На разряды 5,...,8 вхо8 в каждом J-M операционном блоке I подается код Xj с соответствующих выходов регистра 15 множимого через управляющие мультиплексоры 26. Дпя этого на управляющие входы 29 подается сигнал . Рассмотрим функциональную микропрограмму операции умножения. Поскольку число шагов алгоритма уменьшено в четыре раза, с целью повьшения производительности следует испох ьзовать микропрограмму без циклов. С целью упрощения записей микропрограмму рассмотрим применительно к случаю умножения двух вось.миразрядных чисел. На 4мг. 12 приведена укрупненная схема алгоритма микропрограммы умножения. Микропрограмма умножения Начало. В X, на М2;(# чтение из памяА У множимого X ти по адресу в регистр 15) . и запись его Н (Y42) если М2. Pl8-Dl Р д О то на МЗ, иначе на M4j ( чтение из памяти по адресу А У, множителя D, выделение четырех младших разрядов (D ) и запись их в регистр 18, проверка содержимого на равенство нулю 4). МЗ. РЧ 0...0, на М9; ( запись в , регистр 104 числа нуля ). М4. РЧ F2(X,Dy). на М5; ( вычисление S табличным способом, запись результата в регистр 104 числа РЧ) М5. ОЯ- РЧ, на Мб:, (,(- запись в оперативную ячейку памяти содержимого регистра 104 числа РЧ ). Мб. 2-, на М7; (- чтение числа из оперативной ячейки ОЯ и запись со сдвигом на четыре разряда вправо в регистр числа ). М7. ., (X, 0),на MB; ( вычисление П табличным способом и запись в регистр 107 операнда ). М8. + РО, на М9; ( суммирование чисел из регистров числа 104 и операнда 107. и запись результата в регистр числа; результат соответствует частичному fфoизвeдвнию

с П + S ).

М9. 42 8:5J; если О на М10, иначе на МП; ( чтение из памяти множителя D, выделение четырех разрядов 5,...,8 (Dj) и запись их в регистр 18, .проверка содержимого на равенство нулю f) МЮ. , на MI5; ( запись числа из регистра числа в оперативную ячейку памяти ). МП. PO-«-F (XjD), на MI2; ( вычисление S табличным способом, запись результата в регистр операнда 107 t ).

М12 РЧ (РЧ + РО) 2 , на М13; ( сложение чисел из регистров числа и операнда и запись результата со сдвигом на четыре разряда вправо в регистр числа ). М13. (X, D.J), на MI4; ( вычиление П табличным способом и запис в регистр 107 операнда ). MI4. РЧч-РО + РЧ, на М16; ( сум№ рование чисел из регистров операнда 107 и числа 104 с записью резуль.тата в регистр числа; результат соответствует произведению С Сг П + (с зЪ 2 ). М15. , на М16;-/( чтение ОЯ памяти и запись считанного числа со сдвигом на четыре разряда вправо в регистр числа, записанное число соответствует.произведени С С ).

М16. Н (42) ««-РЧ; СК43 : СК43 +1; ( запись результата в накопитель памяти по адресу А У 42 модификация содержимого счетчика 43 команд прибавлением единицы -X ). Конец.

Для иллюстрации алгоритма рассмотрим пример умножения двух чсел X (О), 1 П 11 1 11 и D (0) 1 1010001: М2, В ОГ4:1 000, ,наМ4. М4. 11010001, на М5. М5, Мб. РЧ-«-52 ООООП01 , на М7. М7. 00000000; ла М8. М8. РЧ-еРЧ + РО 00001101 + + 00000000 00001 ГО 1, на М9. М9. D2 1101 О, на МП. МП. PO«S2 ООПООП, на М12. MI2. + РО) 2 (00001101 + ООПООП) 2 00000100, на М13. М13. ПООПОО, на MI4. М14. РО + РЧ ПООПОО + + 00000100 11010000,

Конец.

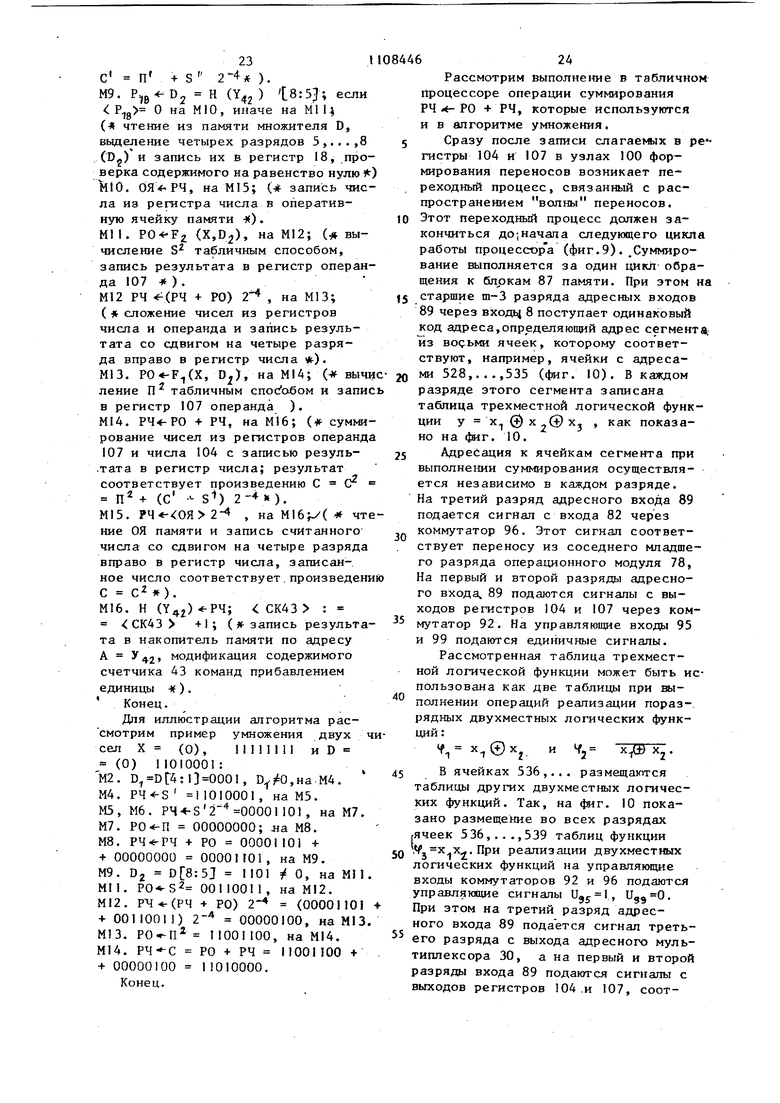

Рассмотрим выполнение в табличном процессоре операции суммирования РЧ-«-РО + РЧ, которые используются и в алгоритме умножения.

Сразу после записи слагаемых в регистры 104 и 107 в узлах 100 формирования переносов возникает переходный процесс, связанный с распространением волны переносов.

Этот переходный процесс должен закончиться до;начала следующего цикла работы процессора (фиг.9) . Суммирование выполняется за один цикл обращения к блркам 87 памяти. При этом на старшие т-3 разряда адресных входов 89 через входц 8 поступает одинаковый код адреса,определяющий адрес сегмента из ворьми ячеек, которому соответствуют, например, ячейки с адресами 528,...,535 (фиг. 10). В каждом разряде этого сегмента записана таблица трехместной логической функ т (4)

как показации у X, но на фиг. 10.

к ячейкам сегмента при выполнении суммирования осуществляется независимо в каждом разряде. На третий разряд адресного входа 89 подается сигнал с входа 82 через коммутатор 96. Этот сигнал соответствует переносу из соседнего младшего разряда операционного модуля 78, На первый и второй разряды адресного входа 89 подаются сигналы с выходов регистров 104 и 107 через коммутатор 92. На управляющие входы 95 и 99 подаются единичные сигналы.

Рассмотренная таблица трехместной логической функции может быть использована как две таблицы при выполнении операций реализации пораз-. рядных двухместных логических функций:

J .

ё

f,

X, 2

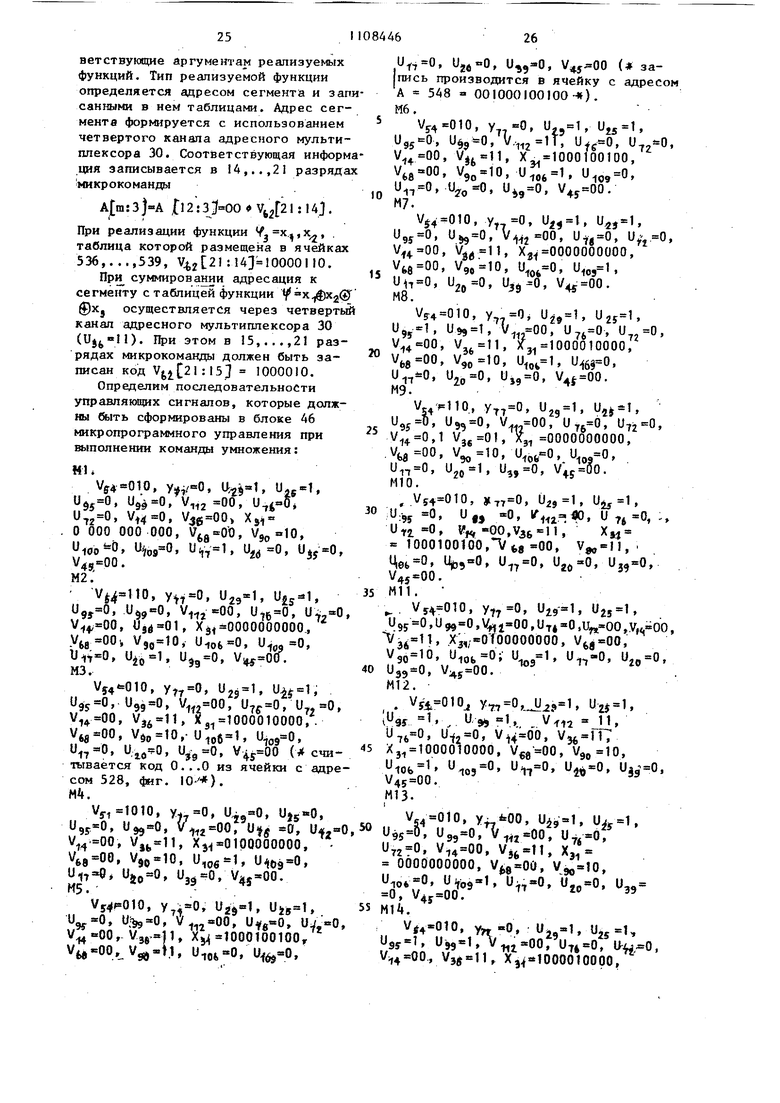

2В ячейках 536,... размещаются таблицы других двухместных логических функций. Так, на фиг. 10 показано размещение во всех разрядах гячеек 536,...,539 таблиц функции х.При реализации двухместных логических функций на управляющие входы коммутаторов 92 и 96 подаются управляющие сигналы 035 , U,, 0. При этом на третий разряд адресного входа 89 подается сигнал третьего разряда с выхода адресного мультиплексора 30, а на первый и второй разряды входа 89 подаются сигналы с выходов регистров 104 ,и 107, соответствующие аргументам реализуемых функций. Тип реализуемой функции определяется адресом сегмента и за санными в нем таблицами. Адрес сег менте формируется с использованием четвертого канала адресного мульти плексора 30. Соответствующая инфор ция записывается в 14,..,21 разряд микрокоманды А{т 3)А {12:3 Ц-ОО « Vj2f21:14j . При реализации функции .,х-, . таблица которой размещена в ячейка 536,...,539, :14} 10000110. При суммировании адресация к сегменту с таблицей функции .,фх2 фх, осуществляется через четверт канал адресного мультиплексора 30 (). Щ)и этом в 15,...,21 раз рядах микрокоманды должен быть записан код V j 21:l5J 1000010. Определим последовательности управляющих сигналов, которые долж ны сформированы в блоке 46 микропрограммного управления при выполнении команды умножения: Vff4«010, , , , , 00, . . , Xsi . 0 000 000 000, Vfcfl OO, , и 100-0 V45(00 . , , , Ugj:-, , , , и 72 ,00, X 3 0000000000, . , U,, 0, , . , , U23 1, , , , , V,00, , Хд 1000010000, 00 . tO,; и „6 1, U,, ,0, , Uc4H ываётся код 0...0 из ячейки с адр тывается COM 528, фиг. lO-- }. , y,0, , U)5«0, y , , , u 0, V/ nn l 1 1 V .-ninnnnnnnn V,, , Xj -OlpOOOOOOO, , . 17-9 , , . K5. , у , , . V , , Xj 1000100100, , Vgj«ii, . U,0, , U,,0, ( запись производится в ячейку с адресом А 548 001000100100-). Мб. У., у 0, и, 1. , Ugs-o. , (/.., , , V.00, Vj.11, X. 1000100100, Vfce-OO, , . U,o,0, ,., и,о, . V 4-010, y., 0, , U, 1, , , V-,, U7,0, , .00, Xj 0000000000, V,, V,, U,,,0, ,1. , , , . М8. , у Q, U2j 1, , , V, 00, , и 0, , V,,,n, X,. 1000010000, v,, v,, и,„,1, . , U,.0, U,, . M9. Vs4FllO, , U2g 1. , , U5,0, V.00, U,0, U72-0, ,l , )Сз, 0000000000, , , и,,.и -. , , и,,.и,„,о, 3, u,. , . , . , M10. , , ,, , , u: 0, и„ -0, ), и , :, Utl 0 00,,Х„ 1000100100,V fee 00, V n, . , , U3,o; . Mil. . , , Ui9 1, , ,,,,,V,,00, , Хз,; ОТОООООООО, , . U, и 1, , и,. , . M12. . Vy4,010j yr,0,, U2j l, « b . ,. v,2 n, , , , V3 n X,, 1000010000, , , , . V °°Jt7.00Ji .b Vg.aUlO, , UAg l, Uu , Ug,o,, U7.-o: 11л t, .. . .. . V,, , Хз 0000000000, Vjj,, Удд 10, . «Ybs-. U,0, , U35 0, . M14. . U -1, , , и„ 1, , , .O, V;,, Уэ 11, Xj -IOOOOIOOpO,

, . , ,

, Uj,, . V,00. M15.

. , 1, и,и

. ik 0 , , . X5 .

1000100100, , ,

. ,

,. . M16.

, у,00, U, l, , Ujg-O, V,. , U72

,. , УЗ,

ii OdOOpOOOOO, Vfce 00, , Uioe 0, U,, U,,0, , , .

После выполнения последней микркоманды в микропрограмме (в данном случае М16) осуществляется переход к микрокоманде, например № 17, при выполнении которой производитс чтение из памяти новой команды по адресу, код которого берется из счетчика команд, запись команды в регистр 37 команд и запись кода опрации в счетчик 51 микрокоманд по входу 47. При этом формируются следукяцие управляющие сигналы: Ml7. V 001, у 0, U2,1, и 1. , , V,,00, U,, V, . X 31 000000000, . 90 10. U,, U,, U,,

u,,o, , v,oo.

W

20

При 4n 8 в схеме алгоритма на фиг. 12 следует увеличить число фрагментов, соответствующих умножению на четыре разряда множителя (М9,...М15). В общем случае при умножении 4п-разрядных чисел для времени умножения 1уполучим следующую среднюю оценку, полагая, что О и I в каждом разряде равновероятны:

1

5 + -L :ь (п-1)х

-II

1

TO

(2,875 + 4,88 n) Тд.

Составив соответствующую микропрограмму, можно показать, что при использовании известного наиболее распространенного в ЭВМ мето-да умножения двоичных чисел-с младших разрядов потребуется в среднем время

t (26п + 6) Тр.

Определим относительное уменьшение времени умножения при использовании таблично-алгоритмического метода:

4п ,(t -tvp/ti, ,

8 58 12,6 0,78 4,5 16 110 22,4 0,80 4,9 32 214 41,9 0,805 5,1

0,81

422

81

5,2

Таким образом, в1/емя умножения уменьшается в средней в 5 раз. Это достигается как за счет уменьшения

числа тиагов в алгоритме (в 4 раза), так и за счет исключения циклов.

Рассмотрим способ деления в табпич ном процессоре Т X : Р, где X делимое, Р - делитель, Т - частное. Представим операцию деления последовательностью двух операций - обращения и умножения

Т (1/Р) X

Для операции обращения У 1/Р воспользуемся итерационной процедурой

2У1 - у;р,

где У - i-e приближение результата, Процедура имеет квадратичную сходимость j т.е. при очередном (i-м) 5 шаге число верных разрядов в результате У удваивается.

Рассмотрим способ определения начального приближения Ур 1/Р.

В общем случае 4п-разрядное число -Р, представленное в форме с фиксированной запятой, может содержать S нулей в старших разрядах, п. Будем рассматривать число Р 2 , в старшем разряде которого единица. 5 Приближенно представим его числом R, пять старших разрядов которого совпадают со старшими разрядами числа Р 2 , а остальные равны нулк . R Р 2 . Числа R расположены в интервале (, 1-2).

Рассмотрим число- Z , пропорцио-нальное обратному значению R;

о - - 2е(1, 2-), Поскольку старший разряд числа R

всегда равен единице ,может быть всегда шестнадцать различных значений R. Х оставим таблицу преобразования Z Pj (R) и разместим ее в ячейка памяти с адресами 512,...,527. (фиг. 10) таким образе, чтобы четыре младших двоичных разряда адреса совпадали с 4п-1, 4п-2, , 4п-4 разрядами соответствующих значений R. Для выделения требуемых разрядов число R сдвигается влево иа один разряд, из сдвинутого числа мульtиnлeкcopaми 12выделяются четыре старших разряда и записываются в регистр 18. Для обращения к таблицам F адре требуемого сегмента памяти поступае из блока 46 микропрограммного управ ления через адресный мультиплексор 30, а адрес требуемой ячейки в сегменте (четыре мпадщих разряда кода адреса на входах 8) - с выхода PI8 через управляющий мультиплексор 22. Цри этом , , U.l. Таким образом, для определения Z табличным способом используются те же технические средства, которые были введены для ускорения уьтожения. Оценим погрешность представления чисел;Р2 числами R 1JL2. ,2- R- 2При этом погрешность определения начального приближения .составит ,.ц;;-:11ш.р.-.,. .р„г.,.,,з-. Таким образам, в Z((6(,) можно считать достоверными четыре старших разряда, остальные разряды в числах, являющихся элементами таблицы преобразования Z « F«(R), следует принять равными нулю (фиг. 10). Для определения Z Y 2« (1/Р) 2 будём использовать итерационную процедуру Z - (Z,-(P.Z)Z.Z,)2, где ,1 ...... В этой процедуре используется число Р, сдвинутое на S разрядов влево при вычислении R, и число Z, полученное с использованием таблицы. После вычисления Z с требуемой точностью для определения частного Т следует выполнить операцию Т . Анализ соответствующей микропрограммы показывает, что время деления указанным способом в сравнении с распространенным методом деления многократным вычитанием делителя и сдвигов уменьшено в среднем на 20%. Таким образом, за счет уменьшения времени умножения и деления обеспечивается повышение производительности процессора.

16р

w

Риг л

Фиг.6

иг.8

Vs.

f/ / lfofJ2J

65

VS2i:37

14,ш

Ж.

lKf rj:fJ

5

zfom:

Ш VS2C35J

f27

М

VsiC3f -10

127

1/в2 С31

%Ш

W

У5гШ

tff %-lferJ7r/J

Vspfy itOJ fJ

Л7

VsfffSJ

1/SoCB

VsoCll .

fsoCSl .

4

5

UjF/yZ- J .

4

гбугг;

а

Й87Ш

4

/25 Фиг.9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логическое запоминающее устройство | 1977 |

|

SU691926A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ОДНОРАЗРЯДНЫЙ БЛОК ЛогаЧЕСКОЙ ПАМЯТИ | 1979 |

|

SU826422A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1982-06-24—Подача