(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297116A1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

| Устройство для сдвига с контролем | 1984 |

|

SU1238058A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных сие - тем обработки информации. Цель изобрете- ния - повышение быстродействия устройства. Устройство содержит формирователь кода маски, группу блоков элементов И, группу блоков элементов ИЛИ, группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу коммутаторов, блок сдвига контрольных разрядов, коммутатор, элементы И. Повышение быстродействия осуществляется за счет сокращения числа входов в элементах ИСКЛЮЧАЮЩЕЕ ИЛИ. 2 ил.. 3 табл.

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных систем обработки информации.

Цель изобретения - повышение быстродействия устройства.

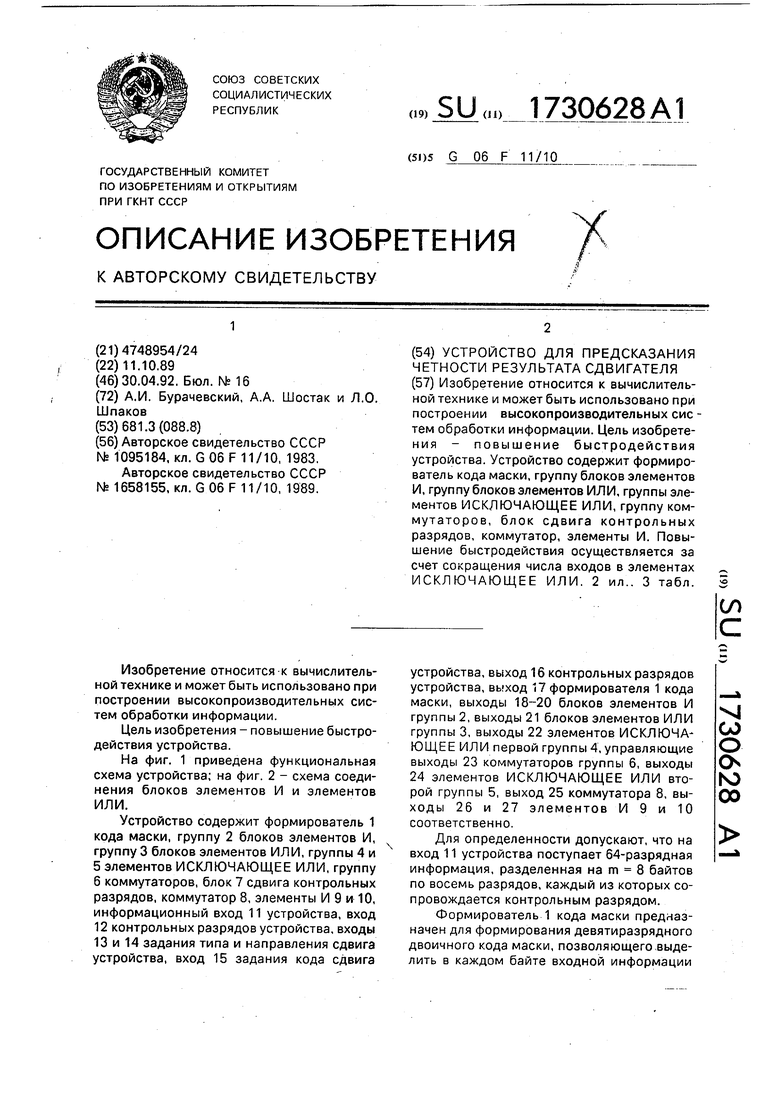

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема соединения блоков элементов И и элементов ИЛИ.

Устройство содержит формирователь 1 кода маски, группу 2 блоков элементов И, группу 3 блоков элементов ИЛИ, группы 4 и

5элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу

6коммутаторов, блок 7 сдвига контрольных разрядов, коммутатор 8, элементы И 9 и 10, информационный вход 11 устройства, вход

12контрольных разрядов устройства, входы

13и 14 задания типа и направления сдвига устройства, вход 15 задания кода сдвига

устройства, выход 16 контрольных разрядов устройства, выход 17 формирователя 1 кода маски, выходы 18-20 блоков элементов И группы 2, выходы 21 блоков элементов ИЛИ группы 3, выходы 22 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 4, управляющие выходы 23 коммутаторов группы 6, выходы 24 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 5, выход 25 коммутатора 8, выходы 26 и 27 элементов И 9 и 10 соответственно.

Для определенности допускают, что на вход 11 устройства поступает 64-разрядная информация, разделенная на m 8 байтов по восемь разрядов, каждый из которых сопровождается контрольным разрядом.

Формирователь 1 кода маски предназначен для формирования девятиразрядного двоичного кода маски, позволяющего выделить в каждом байте входной информации

VJ

GJ О

Os

Ю 00

устройства разряды, которые при выполнении сдвига под управлением младших трех разрядов кода сдвига, поступающего на вход 15 устройства, либо пересекают границу байта, т. е. переходят в соседний байт (при значении трех младших разрядов, меньшем пяти), либо остаются в данном байте (при значении трех младших разрядов, большем или равном пяти), при этом во втором случае также выделяется контрольный разряд байта.

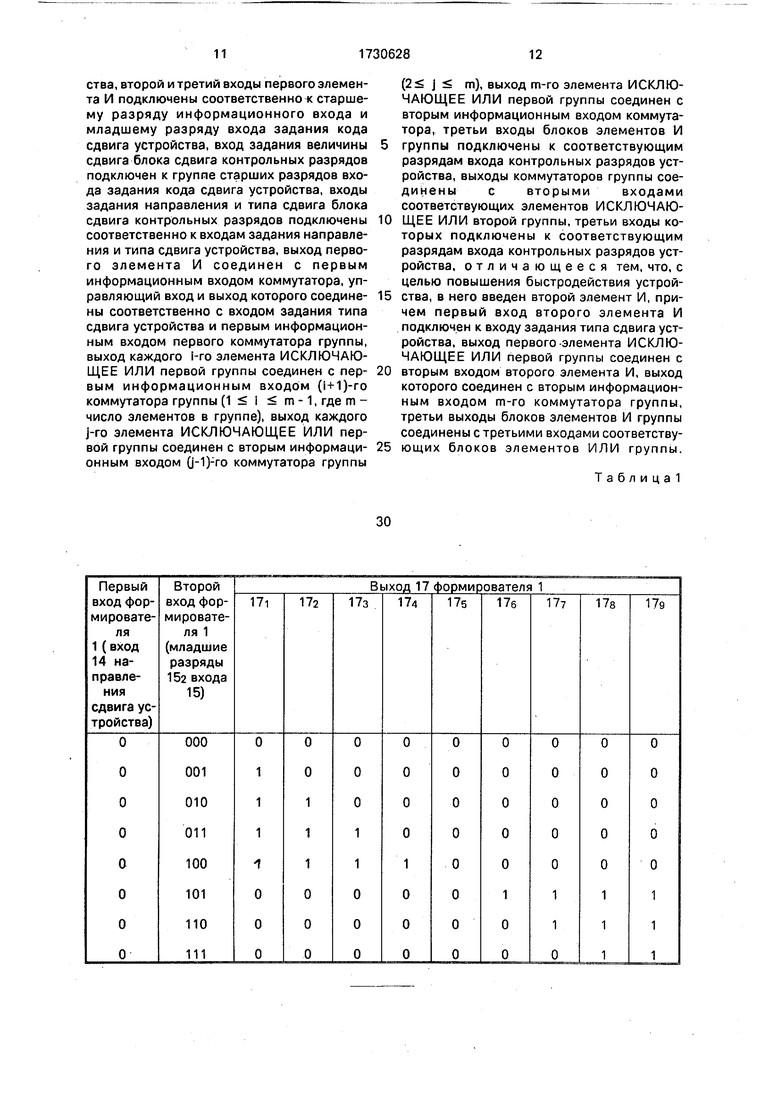

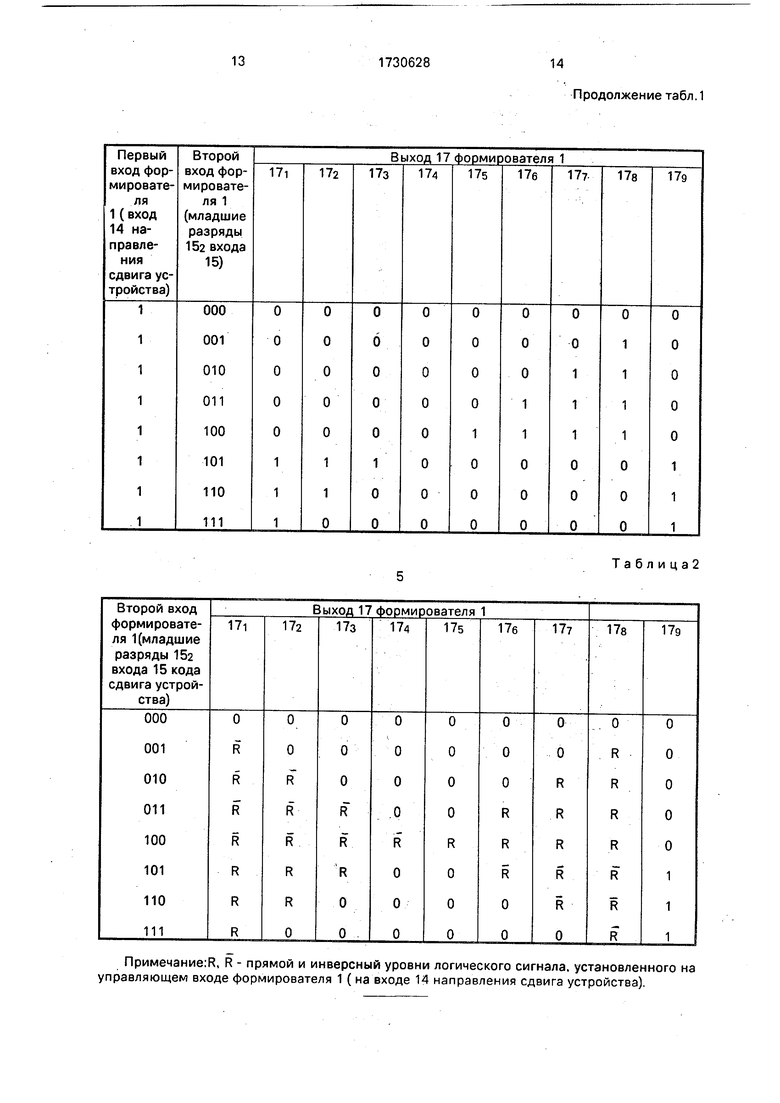

В табл. 1 описано функционирование формирователя 1 кода маски, на управляющий вход которого поступает управляющий сигнал с входа 14 задания направления сдвига устройства, а на информационный вход - младшие три разряда 152 входа 15 задания сдвига устройства.

Допустим, при выполнении сдвига вправо на входе 14 задания направления сдвига устройства устанавливается уровень 1, а при выполнении сдвига влево - уровень О. Независимо от направления сдвига код сдвига на вход 15 устройства поступает в прямом коде.

Формирователь 1 кода маски можно выполнить различными способами: на ППЗУ 500 РЕ 149 (входы формирователя 1 в этом случае являются адресными входами ППЗУ); на элементах И, ИЛИ, НЕ, выполнив синтез по таблице истинности работы формирователя 1; на 8-входовых мультиплексорах 500ИД164 (в этом случае пользуются табл. 2).

В табл. 2 представлено функционирование формирователя 1, учитывающее реализацию его на восьмивходовых мультиплексорах.

Группа 2 блоков элементов И, группа 3 блоков элементов ИЛИ и первая группа 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ совместно формируют для каждого байта входной информации четность выдвигаемых за границу байта разрядов при выполнении сдвигов под управлением младших трех разрядов кода сдвига.

На фиг. 2 показано взаимодействие блока 2i элементов И, блока 3i элементов ИЛИ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4| при формировании четности выдвигаемых разрядов 1-го байта (i 1, 2, 38),

Каждый блок элементов И можно выполнить на девяти двухвходовых элементах И, на первый вход которых поступает соответствующий разряд кода маски, а на второй вход - соответствующий разряд соответствующего байта с входа 11 устройства, либо контрольный разряд соответствующего байта с входа 12 контрольных разрядов устройства.

Каждый из блоков 3i-3a элементов ИЛИ может быть реализован на трех двухвходовых и одном трехвходовом элементах ИЛИ, Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4i-48

первой группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются четырехвходовыми и для их реализации требуется по три двухвходовых элемента 500 ЛП 107.

Вторая группа 5 элементов ИСКЛЮЧА0 ЮЩЕЕ ИЛИ предназначена для формирования контрольных разрядов байтов при выполнении сдвигов под управлением младших разрядов кода сдвига. Она может быть реализована на микросхемах 500 ЛП

5 107.

Блок 7 сдвига контрольных разрядов предназначен для формирования предсказанных значений контрольных разрядов байтов при выполнении сдвигов под управ0 лением старших разрядов кода сдвига. Сформированные на выходах блока 7 контрольные разряды 16i-16s байтов с первого по восьмой соответственно являются предсказанными контрольными разрядами четно5 стирезультатасдвигателя.

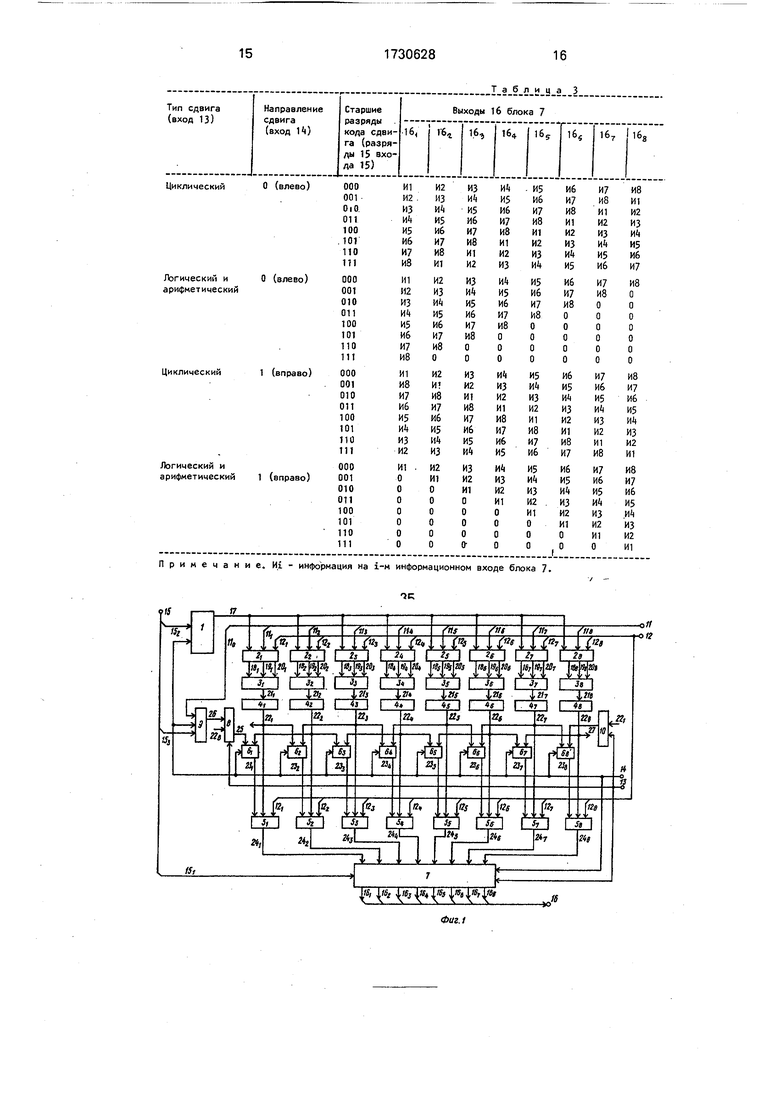

Функционирование блока 7 сдвига контрольных разрядов поясняется с помощью табл. 3. Коммутатор 8 формирует для крайнего левого байта сигнал четности вдвигаемых

0 разрядов при выполнении сдвига вправо под управлением младших разрядов кода сдвига, при этом на выход 25 коммутатора 8 поступает значение с выхода 22в элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 48 группы, если вы5 полняется циклический сдвиг, и значение с выхода 26 первого элемента И 9 - если выполняется арифметический сдвиг. Коммутатор 8 может быть реализован на элементах 500 ЛС 118 или 500 ЛС 119.

0 Первый элемент И 9 предназначен для формирования сигнала четности вдвигаемых единиц при выполнении арифметического сдвига вправо. Этот сигнал равен единице только в том случае, когда в устрой5 стве выполняется арифметический сдвиг вправо на нечетное число разрядов отрицательного числа.

Второй элемент И 10 формирует для крайнего правого байта сигнал четности

0 вдвигаемых разрядов при выполнении сдвига влево под управлением младших разрядов кода сдвига, при этом на выход 27 второго элемента И 10 поступает значение с выхода 22i элемента ИСКЛЮЧАЮЩЕЕ

5 ИЛИ 4i группы (при выполнении циклического сдвига) или уровень О (при выполнении логического или арифметического сдвига). В случае реализации в устройстве только циклического сдвига вправо (циклический сдвиг влево заменяется в этом случае циклическим сдвигом вправо на дополнительный код величины сдвига) необходимость в использовании второго элемента И

10отпадает. В этом случае на второй вход коммутатора 6s необходимо постоянно по- давать уровень О.

Работа устройства рассматривается в различных режимах на примере сдвига в нем восьми байтов входной информации ai 32 аз ...364 на 19 двоичных разрядов (на вход 15 устройства подается прямой двоичный код величины сдвига 010011).

Пусть первый байт ai 32 аз ... ае является самым старшим и сопровождается контрольным разрядом четности Ki, а восьмой байт 357358359...364 является самым младшим и сопровождается контрольным разрядом четности Кв.

Режим Сдвиг вправо логический.

На управляющий вход формирователя 1 кода маски поступает уровень 1 с входа 14 напрэвления сдвига устройства, соответствующий выполнению сдвига вправо, а на информационный вход формирователя 1 подается значение младших трех разрядов 152 входа 15 кода сдвига устройства (в рассматриваемом примере 011). В соответствии с рэботой формирователя 1 (см. табл. 1) на его выходе 17 в этом случае формируется код маски 000001110, который далее поступает на первые входы блоков 2i-2e элементов И, на вторые входы которых подаются значения соответствующих байтов 11i-11e входной информации с информационного входа

11устройства, а на третьи входы - контроль- ные разряды 12i-12e соответствующих байтов с входа 12 контрольных разрядов устройства. Для рассматриваемого случая

на выходах 18i, 19i и 20i блока 2i формируется результат маскирования в виде сово- купности значений 0000, 0 аеатав и О соответственно, на выходах 182, 192 и 202 блока 22 - 0000, 0 ai4aisaie и О соответственно и т. д., на выходах 18в, 19еи 20s блока 2в результат маскирования в виде совокуп- ности значений 0000, 0 362363364 и О.

Далее на блоках 3i-3e элементов ИЛИ и элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4i-4e первой группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ формируются четности выдвига- емых в каждом байте разрядов. Так, на выходе 22i элемента 4i формируется четность р-|ВЬ1А ае ч- а as 0, на выходе 222 элемента 42-P2BblA . д., на выходе 22а элемента 48-Р8ВЫА биаб4€ 0.

Коммутатор 8 формирует четность разрядов, выдвигаемых в старший байт (при выполнении логического сдвига вправо четность вдвигаемых разрядов равна нулю),

подключая выход 26 первого элемента И 9 к выходу 25 под управлением сигналов с входа 13 типа сдвига устройства (на выходе 26 сформирован О).

Поскольку выполняется сдвиг вправо, на управляющие входы коммутаторов поступает уровень 1, под действием которого на выходы 232-238 коммутаторов поступают значения четностей выдвигаемых разрядов с выходов 22i-22 соответственно (на выход 23i коммутатора 6i поступает значение четности вдвигаемых в старший байт разрядов с выхода 25 коммутатора 8).

Таким образом, на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5i-5e поступаюттри составляющие: контрольные разряды 12i-12s соответствующих байтов с входа 12 контрольных разрядов устройства; четности выдвигаемых из данных байтов разрядов с выходов 221-22в элементов 4i-4s соответственно; четности выдвигаемых разрядов из соседних левых байтов с выходов 23i-23s коммутаторов 6i-6e соответственно, которые являются четностями вдвигаемых в соответствующие байты разрядов. На выходах 24i-24e элементов формируются предсказанные значения контрольных разрядов байтов при выполнении сдвига под управлением младших разрядов кода сдвига. Так, на выходе 24i элемента 5i формируется контрольный разряд Ki Ki PiBbW 0, на выходе 342 элемента 52 - К2П К2вР2ВЫА 6Г и т. д., нз выходе-248 элементэ 5а - контрольный разряд Квп Ка С PeBblA С Р7ВЫА.

В блоке 7 сдвига контрольных разрядов под действием управляющих сигналов, поступающих с входа 13 задания типа сдвига устройства и уровня 1, поступающей с входа 14 задания направления сдвига устройства, а также под управлением старших разрядов 15i входа 15 кода сдвига устройства (в данном примере значение трех старших разрядов равноОЮ) выполняется сдвиг контрольных разрядов, сформированных на выходах 24i-24s и поступивших на соответствующие информационные входы блока 7, в соответствии с его работой (табл. 3).

На выходах блока 7 в рассматриваемом примере формируются следующие контрольные разряды: 0. О, Kin, К2П, Кзп, К4П, Кеп. Эти контрольные разряды, поступающие на выход 16 контрольных разрядов устройства, являются предсказанными четностями результата сдвигателя.

Несовпадение хотя бы одного байтэ результата сдвигателя значений его фактической и предсказанной четностей указывает на наличие либо ошибки во входной информации сдвигателя, либо на неисправности в его аппаратуре.

Режим Сдвиг вправо арифметический.

В этом режиме устройство работает аналогично предыдущему. Отличие состоит только в том, что коммутатор 8, формируя четность вдвигаемых в старший байт разрядов, подключает выход 26 первого элемента И 9 под управлением сигналов с входа 13 задания типа сдвига устройства к выходу 25 коммутатора, при этом на выходе 26 первого элемента И 9 формируется признак П, учитывающий четность вдвигаемых единиц при сдвиге отрицательного,числа (в данном примере признак П ai, поскольку выполняется сдвиг вправо и уровень Г поступает на второй вход элемента И 9, а младший разряд 15з входа 15 кода сдвига устройства, подключенный к третьему входу элемента И 9, установлен в 1).

В соответствии с указанным, на выходе 24i элементаб ИСКЛЮЧАЮЩЕЕ ИЛИ формируется контрольный разряд Kin Ki + +Р1ВЬ|Д + п.

Режим Сдвиг вправо циклический.

В этом режиме работа устройства аналогична работе в режиме Сдвиг вправо логический. Отличие состоит в том, что коммутатор 8, формируя четность вдвигаемых в старший байт разрядов, подключает выход 228 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4s под управлением сигналов с входа 13 задания типа сдвига устройства к выходу 25 коммутатора 8, так как выдвигаемые из младшего байта разряды являются вдвигаемыми в старший байт разрядами при выполнении циклического сдвига вправо под управлением младших разрядов кода сдвига. В соответствии с указанным на выходе 241 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5i формируется контрольный разряд Kin Ki + +Р1выд+Р8выд

Кроме того, в блоке 7 сдвига контрольных разрядов под управлением сигналов, поступающих с входа 13 задания типа сдвига устройства, и уровня 1, поступающего с входа 14 направления сдвига устройства, а также под управлением старших разрядов 15i входа 15 кода сдвига устройства (в данном примере значение трех старших разрядов равно 010) выполняется циклический сдвиг контрольных разрядов, сформированных на выходах 24i-24a и поступивших на соответствующие информационные входы блока 7, в соответствии с его работой (см. табл. 3).

В данном примере на выходах блока 7 формируются следующие контрольные разряды: К7П, К8П, Kin, К2П, Кз, К4П, К5П, Кб. Эти

контрольные разряды, являющиеся предсказанными четностями результата сдвигателя, поступают на выход 16 контрольных разрядов устройства.

Режим Сдвиг влево логический.

На управляющий вход формирователя 1 кода маски поступает уровень О с входа 14 задания направления сдвига устройства, соответствующий выполнению сдвига влево, а

0 на информационный вход формирователя 1 подается значение младших трех разрядов 152 входа 15 кода сдвига устройства (в данном примере 011). В соответствии с работой формирователя 1 (см. табл. 1), на его выходе

5 17 в этом случае формируется код маски 111000000, который далее поступает на первые входы блоков 2i-2s, на вторые входы которых подаются значения соответствующих байтов 111-11в входной информации с

0 входа 11 устройства, а на третьи входы - контрольные разряды 12i-12e соответствующих байтов с входа 12 контрольных разрядов устройства. Для данного случая на выходах 18i, 19т и 20i блока 2i формируется

5 результат маскирования в виде совокупности значений aiaaaaO, 0000 и О соответственно, на выходах 182, 192 и 202 - аэаюапО, 0000 и О и т. д., на выходах 18в, 19з и 20е - результат маскирования в виде совокупно0 сти значений asyassasgO, 0000 и О.

Далее в блоках & -3jj элементов ИЛИ и элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4i-48 первой группы формируются четности выдвигаемых в каждом байте разрядов. Так, на

5 выходе 22i элемента 4i формируется четность ai фа2Фаз 90, на выходе 222 элемента 42 - Р2ВЫА ад Ф аюФ аи ФО и т. д., на выходе 22в элемента 4в - четность Р8ВЫД

358 ©359ФО.

0 Второй элемент И 10 формирует четность разрядов, вдвигаемых в младший байт (при выполнении логического и арифметического сдвигов влево четность вдвигаемых разрядов равна нулю).

5 Поскольку выполняется сдвиг влево, то на управляющие входы коммутаторов 6i-6s поступает уровень О, под действием которого на выходы 23i-23 коммутаторов поступают значения четностей выдвигае0 мых разрядов с выходов соответственно, а на выход 23в коммутатора 6s значение четности вдвигаемых в младший байт разрядов с выхода 27 второго элемента И 10.

5 Таким образом, на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5i-5s поступаюттри составляющие: контрольные разряды 12i-12s соответствующих байтов с входа 12 устройства; четности выдвигаемых из данных байтов разрядов с выходов 22i-22g

соответственно и четности выдвигаемых разрядов из соседних правых байтов с выходов 23i-23e соответственно. На выходах 24i-24a элементов 5i-5e формируются предсказанные значения контрольных раз- рядов байтов при выполнении сдвига под управлением младших разрядов кода сдвига. Так, на выходе 24i элемента 5i формируется контрольный разряд Kin KiЈPiBWA ± ЈР2ВЫА, на выходе 242 элемента 52 - Кап Кг+ ( Р2ВЫАЈ РЗВЬ|А и т. д., на выходе 24е элемента 5в - Квп КаЈ Р8ВЬ|Д 0.

В блоке 7 сдвига контрольных разрядов под действием сигналов, поступающих с входа 13 задания типа сдвига устройства, и уровня О, поступающего с входа 14 направления сдвига устройства, а также под управлением разрядов 15/г входа 15 кода сдвига устройства (в данном примере значение старших разрядов равно 010) выполня- ется логический сдвиг влево контрольных разрядов, сформированных на выходах 24i- 24а и поступивших на соответствующие ин- формационные входы блока 7, в соответствии с его работой (см. табл. 3). В данном примере на выходах блока 7 формируются следующие контрольные разряды: Кз, К4П, КБ, Кеп , Кап, 0, 0. Эти контрольные разряды, являющиеся предсказанными четностями результата сдвигателя, поступа- ют на выход 16 контрольных разрядов устройства.

Режим Сдвиг влево арифметический.

В этом режиме устройство работает точно так же, как и в предыдущем режиме, и для тех же данных формируются те же значения предсказанных четностей результата сдвигателя.

Режим Сдвиг влево циклический.

В этом режиме работа устройства ана- логична работе в режиме Сдвиг влево логический. Отличие состоит в том, что второй элемент И 10, формируя четность вдвигаемых в младший байт разрядов, подключает выход 221 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4i под управлением сигналов с входа 13 задания типа сдвига устройства к выходу 27 элемента И 10, так как выдвигаемые из старшего байта разряды являются вдвигаемыми в младший байт разрядами при выполнении циклического сдвига влево под управлением младших разрядов кода сдвига. В соответствии с указанным на выходе 24s элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5е формируется контрольный разряд Кап Кз$ Ф Р1ВЬ|Д.

Кроме того, в блоке 7 сдвига контрольных разрядов под управлением сигналов, поступающих с входа 13 типа сдвига устройства, и уровня О, поступающего с входа 14

направления сдвига устройства, а также под управлением старших разрядов 15/г входа 15 кода сдвига устройства (в данном примере значение трех старших разрядов равно 010) выполняется циклический сдвиг влево контрольных разрядов, сформированных на выходах и поступивших на соответствующие информационные входы блока 7 в соответствии с его работой (см. табл. 3). В данном примере на выходах блока 7 формируются следующие контрольные разряды: Кзп, К4П, Кб. Кб, К7П, Квп, КЛ К2П. Эти контрольные разряды, являющиеся предсказанными четностями результата сдвигателя, поступают на выход 16 контрольных разрядов устройства.

В предлагаемом устройстве, как и в известном, организован автономный контроль по четности, не требующий введения дополнительных связей со сдвигателем и не ограничивающий варианты его реализации, при этом обеспечивается возможность предсказания четности для каждой группы разрядов результата сдвигателя, сопровождаемой своим контрольным разрядом. Формула изобретения Устройство для предсказания четности результата сдвигателя, содержащее формирователь кода маски, группу блоков элементов И, группу блоков элементов ИЛИ, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу коммутаторов, блок сдвига контрольных разрядов, коммутатор и первый элемент И, причем первые входы блоков элементов И группы соединены с соответствующими разрядами выхода формирователя кода маски, вторые входы блоков элементов И группы подключены к соответствующим разрядам информационного входа устройства, первый и второй выходы каждого блока элементов И группы соединены соответственно с первым и вторым входами соответствующего блока элементов ИЛИ группы, выходы которых соединены с входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выходы которых соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы которых соединены с соответствующими разрядами информационного входа блока сдвига контрольных разрядов, выход которого является выходом контрольных разрядов устройства, вход задания направления сдвига устройства подключен к управляющим входам всех коммутаторов группы, первому входу первого элемента И и управляющему входу формирователя кода маски, информационный вход которого подключен к группе младших разрядов входа задания кода сдвига устройства, второй и третий входы первого элемента И подключены соответствен но ж старшему разряду информационного входа и младшему разряду входа задания кода сдвига устройства, вход задания величины сдвига блока сдвига контрольных разрядов подключен к группе старших разрядов входа задания кода сдвига устройства, входы задания направления и типа сдвига блока сдвига контрольных разрядов подключены соответственно к входам задания направления и типа сдвига устройства, выход первого элемента И соединен с первым информационным входом коммутатора, управляющий вход и выход которого соедине- ны соответственно с входом задания типа сдвига устройства и первым информационным входом первого коммутатора группы, выход каждого i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с пер- вым информационным входом (i+1)-ro коммутатора группы (1 i m - 1, где m - число элементов в группе), выход каждого j-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с вторым информаци- онным входом (j-1)-ro коммутатора группы

(2 j m), выход m-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с вторым информационным входом коммутатора, третьи входы блоков элементов И группы подключены к соответствующим разрядам входа контрольных разрядов устройства, выходы коммутаторов группы соединены с вторыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, третьи входы которых подключены к соответствующим разрядам входа контрольных разрядов устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введен второй элемент И, причем первый вход второго элемента И подключен к входу задания типа сдвига устройства, выход первого-элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с вторым входом второго элемента И, выход которого соединен с вторым информационным входом m-го коммутатора группы, третьи выходы блоков элементов И группы соединены с третьими входами соответствующих блоков элементов ИЛИ группы.

Т а б л и ц а 1

Примечание., R - прямой и инверсный уровни логического сигнала, установленного на управляющем входе формирователя 1 ( на входе 14 направления сдвига устройства).

Продолжение табл. 1

Таблица2

Примечание. Hi- информация на i-м информационном входе блока 7.

Ц % Ц«ЦйГ

CXI

eu

3

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-10-11—Подача