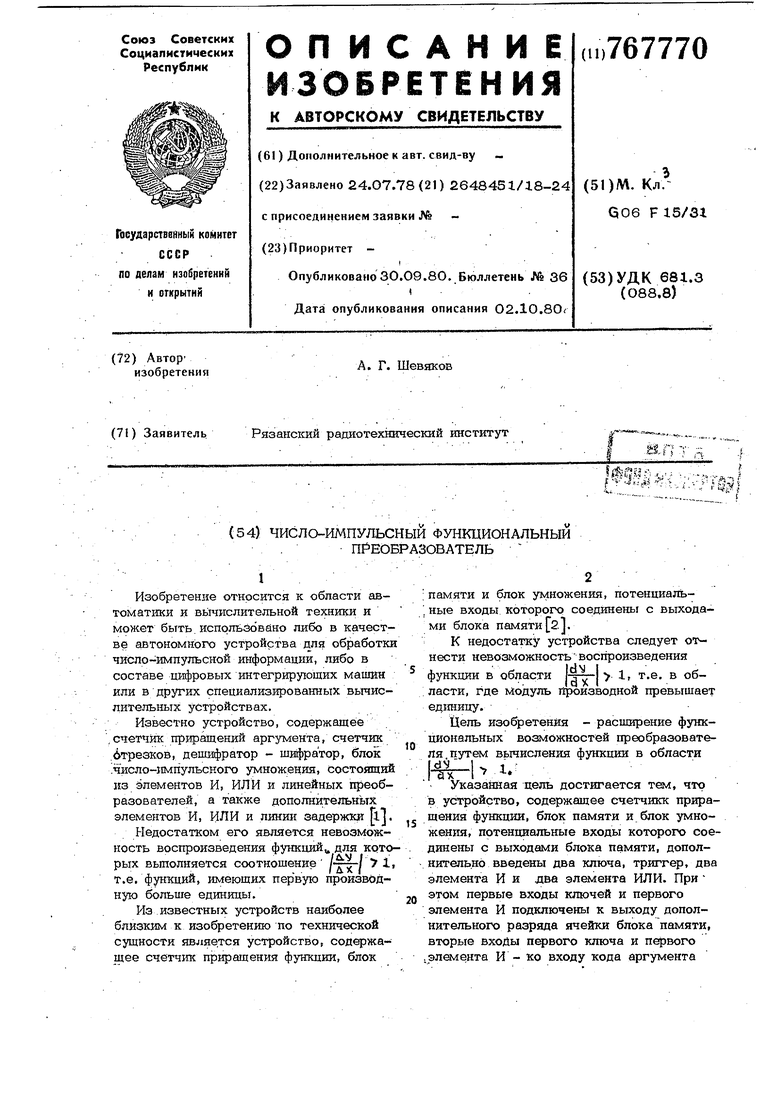

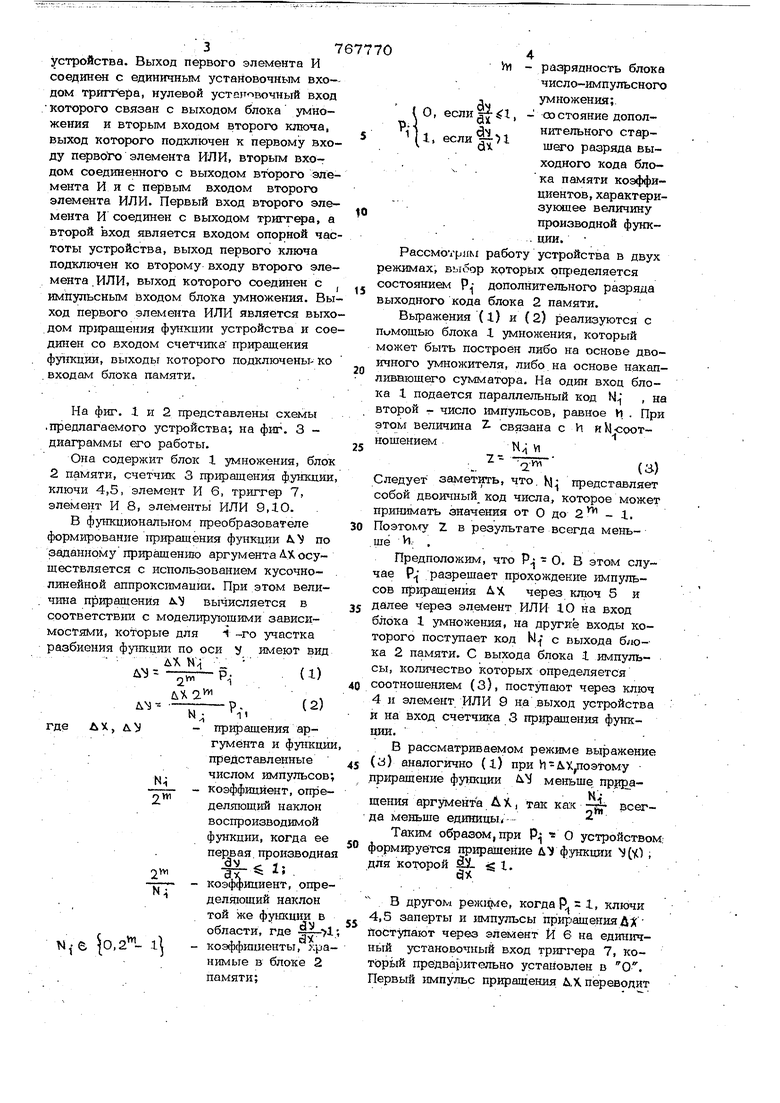

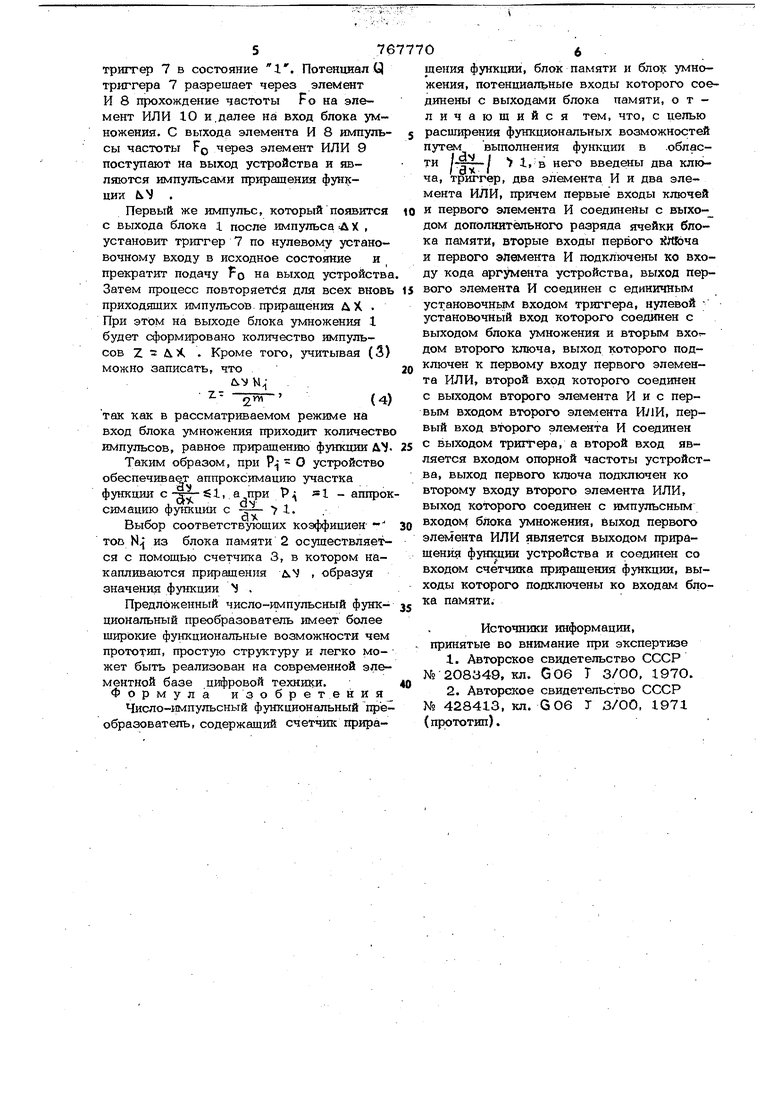

: 37 устройства. Выход первого элемента И соедини с единичным установочным входом триггера, нулевой уста товочный вход которого связан с выходом блока умножения и вторым входом второго ключа, выход которого подключен к первому входу первого элемента ИЛИ, вторым входом соединенного с выходом второго элемента И и с первым входом второго элемента ИЛИ. Первый вход второго элемента И соединен с выходом триггера, а второй вход является входом опорной час тоты устройства, выход первого ключа подключен ко второму входу второго элемента. ИЛИ, выход которого соединен с импульсным входом блока умножения. Вы ход первого элемента ИЛИ является выхо дом пр1фа1цения футжции устройства и сое динен со входом счетчика приращения функции, выходы которого подключены- ко входам блока памяти. На фиг. 1 и 2 представлены схемы .предлагаемого устройства; на фиг. 3 диаграммы его работы. Она содержит блок 1 умножения, блок 2 памяти, счетчик 3 приращения ф ункции ключи 4,5, элемент И б, триггер 7, элемент И 8, элементы ИЛИ 9ДО. В фу псциональном преобразователе формирование Приращения функции ДМ по заданномуприращению аргумента ДХ осуществляется с использованием кусочнолинейной аппроксимации. При этом величина приращения Д. вычисляется в соответствии с моделируюшими зависимостями, которые для 4 -го участка разбиения фуисции по оси у имеют вид АХ К| л ---г™-Р. Д.) где АХ, д. -приращения аргумента и функци представленные числом импульсов -коэффициент, определяющий наклон воспроизводимой функции, когда ее первая производна -коэффициент, опре деляющий наклон той же фушшии в области, где , l -коэффициенты, хра нимые в блоке 2 памяти; /M - разрядность блока число-импульсного умножения;. О, , - состояние дополесли Пнитепьного старшего разряда выходного кода блока памяти коэффициентов, характеризукнцее величину производной функ. ции. Рассмотрим работу устройства в двух режимах, выбор которых оп1:)еделяется состояниекч дополнительного разряда выходного кода блока 2 памяти. Выражения (l) и (2) реализуются с помощью блока Л. умножения, который может быть построен либо на основе двоичного умножителя, либо на основе накапливающего сумматора. На один вход блока 1 подается параллельный код , на второй - число импульсов, равное И . При этом величина Т- связана с И и М соотнощениемN Vi :.. (а) Следует заметить, что. KI.J представляет собой двоичный код числа, которое может принимать значения от о до 2 - 1. Поэтокгу 7. в результате всегда меньще . Предположим, что Р - О. В этом случае разрешает прохождение импульсов приращения ЛХ через ключ 5 и далее через элемент ИЛИ 10 на вход блока 1 умножения, на другие входы которого поступает код с выхода блока 2 памяти. С выхода блока i импульсы, количество которых определяется соотнощением (З), поступают через ключ 4 и элемент ИЛИ 9 на .выход устройства и на вход счетчика 3 приращения функции. В рассматриваемом режиме выражение (з) аналогично (i) при И ЛХ оэТому пр1.гращение функции Л меньще приращения аргумента Л X, так как - всегда меньще единицы, - Таким образом, при Р О устройством, формируется приращение Л ф;ункш1И V(4) , для которой Ш1 1. (дХ В другом peжиjvte, когда Р 1, ключи 4,5 заперты и импульсы приращения ДХ йоСтупают через элемент И 6 на едишгчнь1Й установочный вход триггера 7, который прейварительно установлен в О, Первый импульс приращения Д,Х, переводит триггер 7 в состояние . Потенциал Сэ| триггера 7 разрешает через элемент И 8 прохождение частоты Fo на элемент ИЛИ 10 и,далее на вход блока умножения. С выхода элемента И 8 импульсы частоты FO через элемент ИЛИ 9 поступают на выход устройства н являцотся импульсами приращения функции М . Первый же импульс, который появится с выхода блока 1 после импульса ДХ , установит триггер 7 по нулевому установочному входу в исходное состояние и прекратит подачу f о на выход устройства Затем процесс повторяется для всех вновь приходящих импульсов, приращения ДХ . При этом на выходе блока умножения 1 будет сформировано количество импульсов Z Л), . Кроме того, учитывая (3) можно записать, что (4) так как в рассматриваемом режиме на вход блока умножения приходит количество импульсов, равное приращению функции ДЧТаким образом, при Р - О устройство обеспечивает аппроксимацию участка функции , а при Рд 1 - аппрок симацию ф псции с 1. . Выбор соответствутощих коэффициен ТОО Щ из блока памяти 2 осуществляется с помощью счетчика 3, в котором накапливаются приращения л. , образуя значения функции . Предложенный число-импульсный функциоНальный преобразователь имеет более широкие функциональные возможности чем прототип, простую структуру и легко мо жет быть реализован на современной элементной базе цифровой техники. Формула изобретения Число-1 мпульсный функциональный преобразователь, содержащий счетчик приращения функции, блок памяти и бло умножения, потенциальные входы которого соединены с выходами блока памяти, отличающийся тем, что, с целью расширения фушсциональных возможностей путем выполнения функции в .области i в него введены два ключа, триггер, два элемента И и два элемента ИЛИ, причем первые входы ключей и первого элемента И соединены с выхо- Дом дополнительного разряда ячейки блока памяти, вторые входы первого йД1Ьча и первого элемента И подключены ко вхоДУ кода аргумента устройства, выход первого элемента И соединен с единичным установочнь1м входом триггера, нулевой ; установочный вход которого соединен с выходом блока умножения и вторым вхотдом второго ключа, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен выходом второго элемента И и с входом второго элемента ИЛИ, вход второго элемента И соединен выходом тригг а, а второй вход является входом опорной частоты устройст выход первого кдюча подключен ко второму входу второго элемента ИЛИ, выход которого соединен с импульсным вводом блока умножения, выход первого элемента ИЛИ является выходом прира ния функции устройства и соединен со входом счетчика приращения функции, выходы которого подключены ко входам бло памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №208349, кл. G06 Т 3/00, 1970. 2.Авторское свидетельство СССР № 428413, кл. G06 Т 3/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Число-импульсный функциональный преобразователь | 1979 |

|

SU860071A1 |

| Число-импульсный функциональный преобразователь | 1980 |

|

SU924715A2 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Цифровое устройство для воспроизведения кусочно-линейных функций | 1978 |

|

SU771671A1 |

| Устройство для воспроизведенияфуНКций | 1979 |

|

SU809200A1 |

| Конвейерное устройство для вычисления элементарных функций | 1980 |

|

SU888132A1 |

| Устройство для вычисления функций вида у=ах @ и у= @ | 1980 |

|

SU885998A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Цифровое устройство для формирования круговых разверток | 1978 |

|

SU746541A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

У

у

ИНН КПП

t t

Авторы

Даты

1980-09-30—Публикация

1978-07-24—Подача