1

Устройство относится к автоматике и вычислительной технике и может быть использовано либо в качестве автономного устройства для обработки числоимпульсной информации, либо в составе цифровых интегрирующих машин,раэвертывакхцих измерительных систем или других специализированных вычислительных устройств.

Известен функциональный преобразователь, предназначенный для формирования приращения функции йу по заданному приращению аргумента лх и содержащий блок памяти коэффициентов,подк.шоченный к 6.ПОКУ число-импульсного умножения, и счетчики приращений flj.

К недостаткам его следует отнести невозможность воспроизведения функций, имеющих первую производную бдльше единицы и низкую точность, обусловленную кусочно-линейной аппроксимацией.

Из известных устройств наиболее близок по технической сущности к предлагаемому преобразователь, содержащий счетчик приращения функции, блок памяти, блок число-импульсного умножения, два ключа, два элемента И, первый триггер, два элемента ИЛИ, причем выход дополнительного разряда

блока памяти подключен к упраалшощьм входам ключей, внфосмационные входы котоЕялх подключены соответственно к выходу б.пока число-шлпульсного ум- : ножения и входу преобразователя,выходы ключей подключены соответственно к первым входам первого и второго элементов ШШ, вторЕ вхоХ1Ы которых подключены к выходу первого элемента

10 И, первый вход которого соединен с входом опорной частоты преобразователя, а второй - с выходом первого триггера, первый вход которого соединен с выходом второго элемента И,пер15вь и второй входам которого соединены соответственно с входом преобразователя и зы оясйА дополнительного разряда блока памяти, второй вход первого триггера соединен с выходом блока

20 число-импульсного умножения, выход первого элемента ИЛИ соединен с первым входом счетчика приращения функции и выходом преобразователя, выход второго элемента ИЛИ соединен с

25 mmyytbcwoM входом блока число-импульсного умножения 12 J.

Недостаток этого преобразователя низкая точность. ,

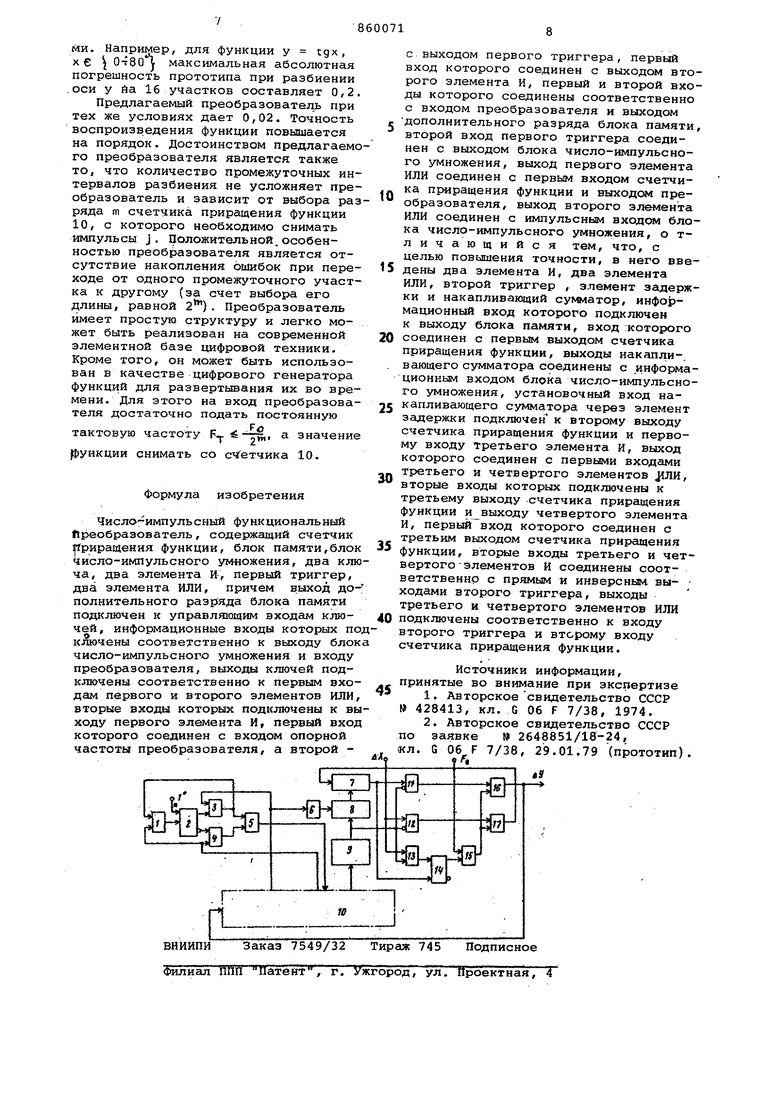

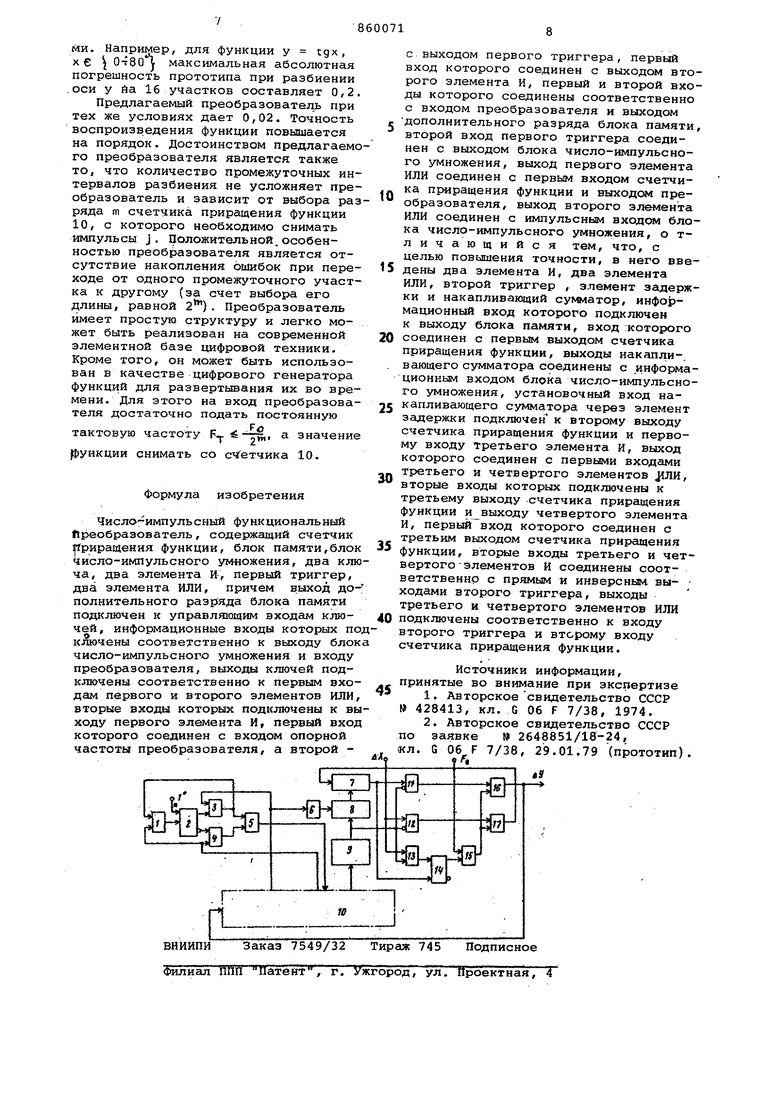

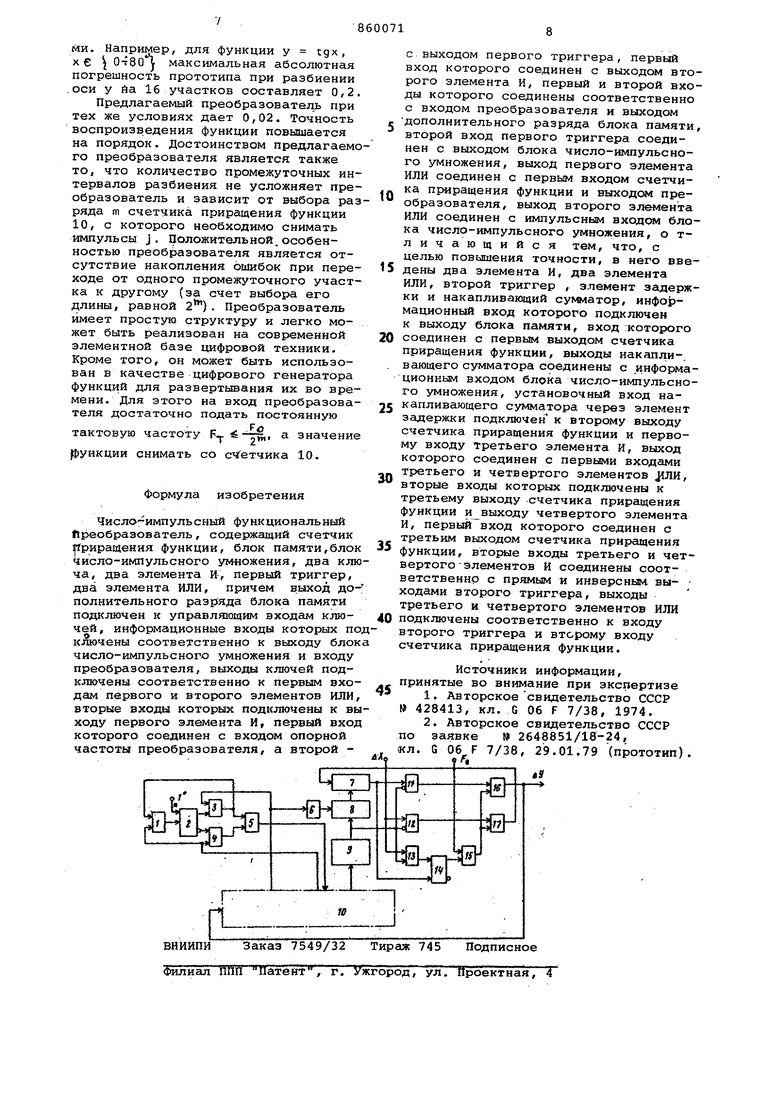

Цель изобретения 7 повышение точ30ности воспроизведения функции. Поставленная цель достигается тем, что в преобразователь дополнительно введены два элемента И, два элемента ИЛИ, второй триггер, элемент задержки и накапливающий сумматор,информационный вход которого подключен к выходу блока памяти, вход которого соединен с первым выходом счетчика гриращения функции, выходы накапливающего сумматора соединены с информационным входом блока число-импульсного умножения, установочный вход накапливающего сумматора через элемент задержки подключен к второму выходу счетчика приращения функции и первому входу третьего элемента И, выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых подключены к третьему выходу счетчика приращения функции и выходу четвертого .элемента И, первый вход которого соединен с третьим выходом счетчика приращения функции, вторые входы третьего и четвертого элементов И соединены соответственно с прямым и инверсным выходами второго триггера, выходы третьего и четвертого элементов ИЛИ подключены соответственно к входу второго триггера и второму входу счетчика приращения функции. Блок-схема преобразователя представлена на чертеже. Преобразователь содержит третий элемент ИЛИ 1, второй триггер 2,третий и четвертый элементы И 3 и 4, четвертый элемент ИЛИ 5, элемент 6 задержки, блок 7 число-импульсного умножения, накапливающий сумматор 8, блок 9 памяти, счетчик 10 приращения функции, ключи 11 и 12, второй элемент И 13, первый триггер 14, пер вый элемент И 15 и первый и второй элементы ИЛИ 16 и 17. Преобразователь работает следующим образом. Формирование прирадения ду функции У по заданному приращению аргумента Дх осуществляется с использованием двух видов кусочной аппроксимации по оси у. На каждом из участков функции заменяется параболой второго порядка N-- a-+fa(x-x)(x-,-). (Н) в свою очередь i-ый участок разбивается на k промежуточных интервалов,, а парабола (1) воспроизводится линейными отрезками )ix, (2) где у - значение функции у в точ ке х;, дх х-х;-приращение apryivieHTa на J-OM промежуточном интерв але; ве по ры ци гд ния ход мят ре вы ра .. С4 ро 1ра55 ус ще щи ра ад ча ци ле ке ft J nd- коэффициенты, постоянные на протяжении всего i-го интервала; l--tMt h - шаг квадратичной аппроксимации, hj- промежуточный шаг. соответствии с выражением (2) ичина приращения ду вычисляется оделирующим зависимостям, котодля j-ro участка разбиения функу имеют вид -Pi, ( ЛХ 2 Л - гР с«- df . j; N. АХ, ду - приращения аргумента и функции, представленные числом импульсов; 1 . IJ коэффициент,определяющий наклон (той же) воспроизводимой функции, когда ее первая производная dy/tjx -f, С + d j 2 /Nj- коэффициент,определяющий наклон той же функции в Области, где dv { 4t. С , d коэффициенты, хранимые в блоке 9 памяти; т - разрядность блока 7 числоимпульсного умножения, 2 1.0,если -f.ecAM IJ - состояние дополнительного старшего разряда блока памяти, характеризуквдее величину производной функции. нач)ение двоичного кода N| + J - d фоЕ ируется путем сложев накапливающем сумматоре 8 выого кода CJ или dj блока 9 папо импульсам j/ приходящим чеэлемент б задержки с выхода перm разрядов (СЧ1) счетчика 10 приния функции. правление выбором коэффициенте d осуществляется схейой форминия адресных импульсов (блоки , которая работает следующим обм. исходном состоянии триггер 2 новлен в 1, счетчик 10 прирая функции обнулен, в накапливаюсумматор 8 занесен код С выбый из блока 9 памяти по нулевому су. Код 0 N о обеспечивает наный наклон функции у. ри завершении развертывания функна первом промежуточном интерват.е. при значении кода в счетчи10 ду 2 импульс переполнения 1 через элемент И 3, а затем элемент ИЛИ 5 увеличивает содержимое старших разрядов счетчика приращения функции 10 на единицу, а через элемент ИЛИ 1 по заднему фронту сбрасывает триггер 2 в О. Из блока 9 памяти выбирается коэф фициент d и тем же импульсом j 1 (через элемент задержки) прибавляется к содержимому (Скапливающего сумматора 8. Так формируется код N1 г 4- н 1-0 оПри дальнейшем поступлении приращения Ду импульсы переполнения J со счетчика 10 суммируют код dj с содер жимьм сумматора 8 при переходе от од ного промежуточного участка аппрокси мации к другому, в результате на выходе сумматора 8 получен ступенчато изменяющийся код Ч( (в известном пре образователе f2j Mj const), что позволяет более точно воспроизводить заданные функции. После окончания воспроизведения функции на квадратичном интервале, т.е. при поступлении на вход счетчика 10 количества импульсов лУ h 2. k, импульс переполнения i выби рает приращение нового наклона С, а затем снова устанавливает триггер 2 в состояние 1. Далее работа схемы формирования адресных импульсов при переходе от i -го участка к -ому пов торяется. Рассмотрим работу предлагаемого функционального преобразователя в двух режимах, выбор которых определя ется состоянием р. дополнительного разряда выходного кода блока 9 памяти. Каждое из выражений (3-) и (4) реа лизуется с помощью блока 7 число-импульсного умножения, который может быть построен либо на основе двоично го умножения, либо на основе накапли вающего сумматора. На один вход блока 7 подается параллельный двоичный :код N-, на второй - число импульсор, равное п. При этом результат умножения Z связан спи NV соотношением 7 NiH Следует заметить, что Ny представ ляет собой двоичный код числа, которое может принимать значения в преде 1. Поэтому .2 всегда лах от О до 2 меньше п. Если предположить, что Р.- О, то в ЭТОМ случае разрешает прохождение импульсов приращения дх через ключ 12 и далее через элемент ИЛИ 17 на вход блока 7 число-импульсного умножения, на другие входы которого поступает NJ с выхода накапливающего сумматора 8. С выхода блока 7 импульсы, количество которых определяется соотношением (5), поступают через ключ 11 и элемент ИЛИ 16 на выход преобразователя и на вход счетчи-. ка 10 приращения функции. В рассматриваемом режиме выражение (5) аналогично (3) при и дх, поэтому приращение функции ду меньше приращения аргумента лх, так как Nv/2 всегда меньше единицы. Таким образом, при О преобразователем формируется приргицение функции у(х), для которой drr/dx 5 1. В другом режиме, когда 1,ключи 11 и 12 заперты и импульсы приращения АХ поступают через элемент И .13 на первый установочный вход триггера 14, который предварительно установлен в О. Первый импульс приращения л х пе-. реводит триггер 14 в 1. Единичный потенциал триггера 14 разрешает прохождетние частоты Гд через элемент И 15 на элемент ИЛИ 17 и далее на вход блока 7 число-импульсного умножения. С выхода элемента И 15 импульсы частоты F, через элемент ИЛИ 16 поступают на выход преобразоВателя и являются импульсами приращения функции ду. Первый же импульс,который появится с выхода блока 7 после импульса лх, установит триггер 14 по второму установочному входу в исходное состояние и прекратит подачу F на выход преобразователя. Описанный процесс повторяется для всех вновь приходящих импульсов приращения дх. При этом на выходе блока 7 число-импульсного умножения будет сформировано количество импульсов Z дх. Учитывая соотношение (5).можно записать , что --,« так как в рассматриваемом режиме на вход блока 7 число-импульсного умножения приходит количество импульсов, равное приращению функции ду. Замеыив в (6) переменную z на их, получают Из выражения (7) которое аналогично (4), видно, что У- 1,поскольку N; всегда меньше 2. Таким образом, при Р О преобразователь обеспечивает аппроксимацию d V участка функции с 1 з при 1 - аппроксимацию функции с У. 1 dx Предлагаемый число-импульсный функциональный преобразователь наряду с возможностью воспроизведения функции с f(x) 1 обладает более высокими точностными характеристика

| название | год | авторы | номер документа |

|---|---|---|---|

| Число-импульсный функциональный преобразователь | 1980 |

|

SU924715A2 |

| Число-импульсный функциональный преобразователь | 1978 |

|

SU767770A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Цифровое устройство для воспроизведения кусочно-линейных функций | 1978 |

|

SU771671A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Генератор функций | 1984 |

|

SU1275411A1 |

| Генератор векторов | 1987 |

|

SU1462403A1 |

Авторы

Даты

1981-08-30—Публикация

1979-09-17—Подача