I

Устройство относится к вычислительной технике и преоназначеио аля использования в высокоскоростных вычислительных устройствах, обрабатьшаюших большие массивы данных.

Известное устройство аля вычиегюния элементарньк функций Cll содержащее семь сумматоров, три регистра числа, регистр аргумента, регистр остатка, два блока округления, тринашать элементов И, два блока умножения, семь элементов ИЛИ, восемь блоков сравнения и четыре счетчика. Работа устройства выполняется в виде последова.тельности итераций, причем в каждой итерации выполняется несколько умножений.

Недостатком устройства, является низкое быстродействие. I Наибоше близок к предлагаемому цифровой генератор функций , содержащий три блока памяти, многоразрядный комбинационный сумматор, блок умножения, два коммутатора, блок управления и четыре регистра

У этого устройство тот же недостаток.

Целью изобретения является повышение быстродействия устройства для вычисления элементарных функций при о&работке массивов данных.

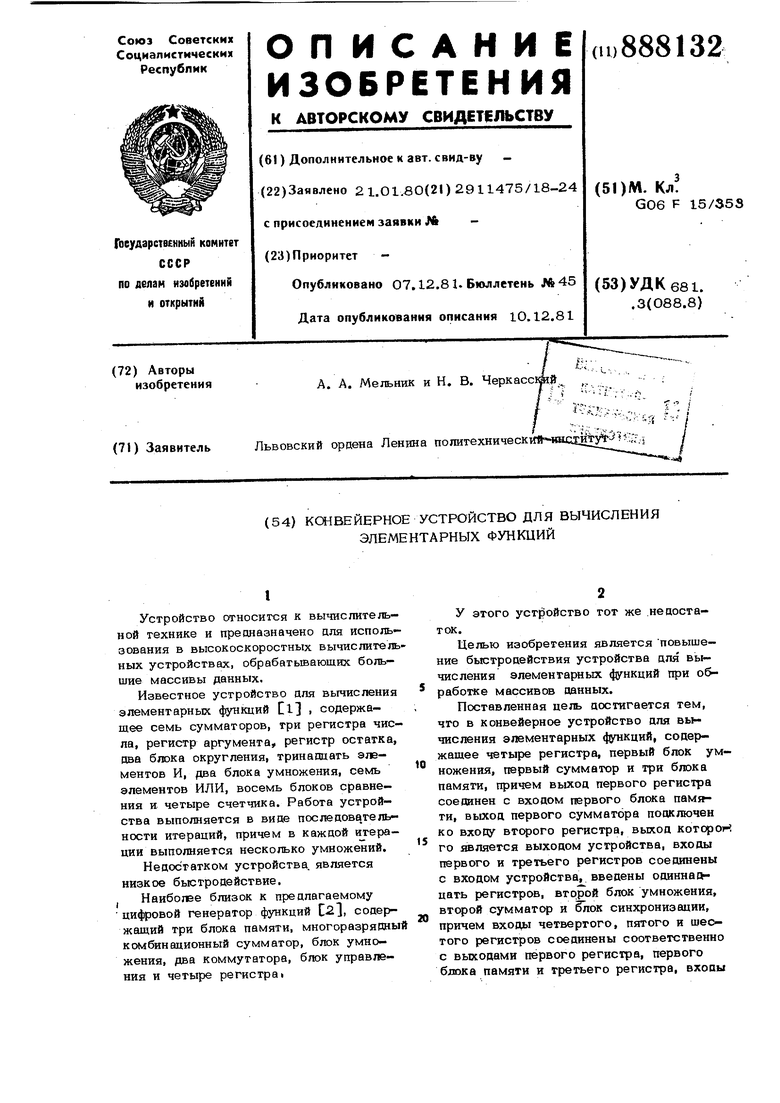

Поставленная цель достигается тем, что в конвейерное устройство для вычисления элементарных функций, содержащее четыре регистра, первый блок ум10ножения, первый сумматор и три блока памяти, причем выход первого регистра соединен с входом первого блока naMsfти, выход первого сумматора подключен ко BXOCV второго регистра, выход которой

15 го является выходом устройства, входы первого и третьего регистров соединены с входом устройства, введены одиннадцать регистров, второй блок умножения, второй сумматор и ёлок синхронизации,

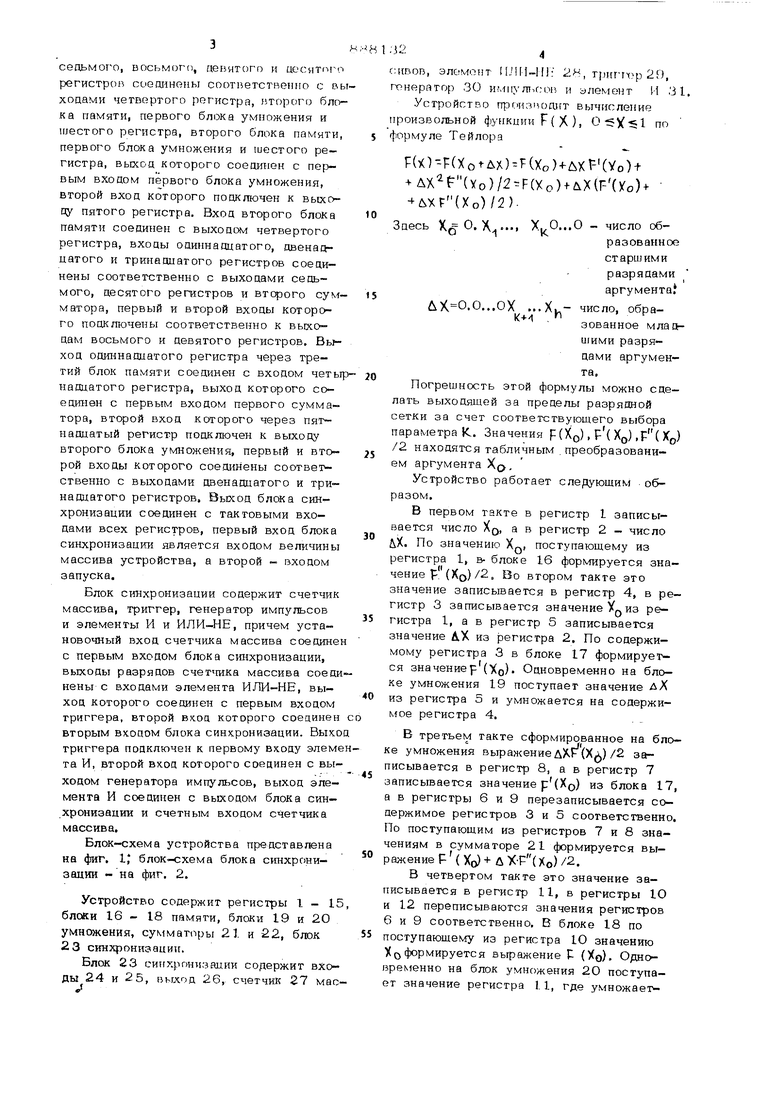

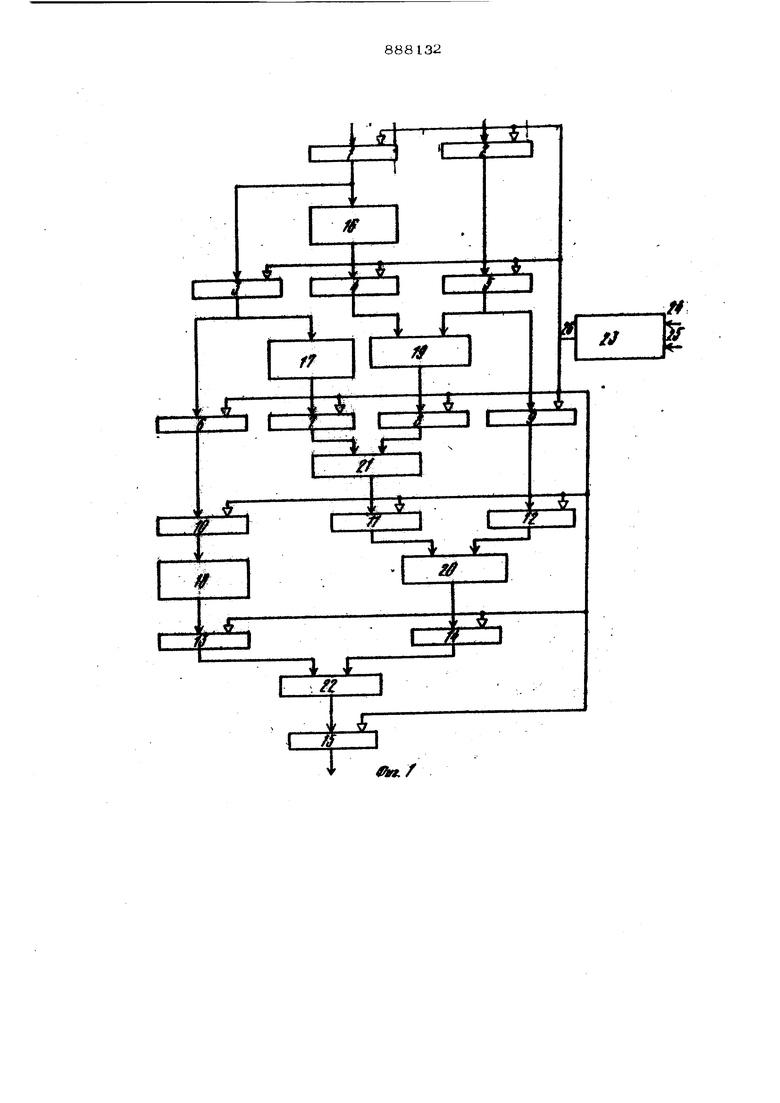

20 причем входы четвертого, пятого и шестого регистров соединены соответственно с выходами первого регистра, первого блока памяти и третьего регистра, входы седьмого, восьмого, цевятого и дасятм р регистров сиешшеиы соогвегсгвеино с вы ходами чегвергого регистра, второго блока памяти, первого блока умножения и ujecToro регистра, второго блока памяти, первого блока умножения и шестого регистра, выход которого соецинен с первым входом первого блока умножения, второй вход которого подключен к выхооу пятого регистра. Вход второго блока памяти соединен с выходом четвертого регистра, входы одиннадцатого, овенадцатого и тринадцатого регистров соединены соответственно с выходами седьмого, десятого регистров и второго сум матора, первый и второй входы которого подключены соответственно к выходам восьмого и девятого регистров. Выход одиннадцатого регистра через третий блок памяти соединен с входом четы наоцатого регистра, выход которого соединен с первым входом первого сумматора, второй вход которого через пятнадцатый регистр подключен к выходу второго блока умножения, первый и второй входы которого соединены соотверственно с выходами двенадцатого и тринадцатого регистров. Выход блока синхронизации соединен с тактовыми входами всех регистров, первый вход блока синхронизации является входом величины массива устройства, а второй - входом запуска. Блок синхронизации содержит счетчик массива, триггер, генератор импульсов и элементы И и ИЛИ-НЕ, причем установочный вход счетчика массива соедине с первым входом блока синхронизации, выходы разрядов счетчика массива соед нены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом триггера, второй вход которого соецинен вторым входом блока синхронизации. Вых триггера подключен к первому вкоду элем та И, второй вкоц которого соединен с вы ходом генератора импул1)Сов, выход элемента И соединен с выходом блока синхронизации и счетным входом счетчика массива. Блок-схема устройства представлена на фиг, IJ блок-схема блока синхронизации - на фиг, 2, Устройство содержит регистры 1-1 блоки 16 - 18 памяти, блоки 19 и 20 умножения, сумматоры 21 и 22, блок 23 синхронизации. Блок 23 си({хрпнт зации содержит вхо ды 24 и 25, выход 26, счетчик 27 ма ивов, элемент (1Л11-1П; 2Н, тригг-ор 29, онервтор 30 импулт г.ов и влемент И 31, Устройство щэг)нзи)шгт вычисление роизвольной функции F(X), по ормуле Тейлора F()()F(XotДx)-F(Xo)- ЛXГ-(Уo)(Уо)(Хо) + лХ(Г-()о)+ -+&XF(Xo)/2). Здесь XjfO, Х.... ,,,0 - число образованноестаршими разрядами аргумента, ,0,,,ОХ ,..Х.- число, обраК+Лзованное младшими разрядами аргумента. Погрешность этой формулы можно сделать выходящей за пределы разрядной сетки за счет соответствующего выбора параметра К, Значения р(Хо), Р ( XQ) ,Р( Хр) /2 находятся табличньп , преобразованием аргумента Хо, Устройство работает следующим образом, В первом такте в регистр 1 записывается число XQ, а в регистр 2 - число &Х, По значению XQ, поступающему из регистра 1, в- блоке 16 формируется значение р, (Хо)/2. Во втором такте это значение записывается в регистр 4, в регистр 3 записывается значение регистра 1, а в регистр 5 записывается значение АХ из эегистра 2, По содержимому регистра 3 в блоке 17 формируется значениеР(ХО) Одновременно на блоке умножения 19 поступает значение ДХ из регистра 5 и умножается на содержимое регистра 4, В третьем такте сформированное на блое умножения выражение дХр(Х)/2 записывается в регистр 8, а в регистр 7 записывается значение р (Хо) из блока 17, а в регистры 6 и 9 перезаписывается содержимое регистров 3 и 5 соответственно. По поступающим из регистров 7 и 8 значениям в сумматоре 21 формируется выражение р (Хо) + Л X-F(XO) /2, В четвертом такте это значение записывается в регистр 11, в регистры Ю и 12 переписываются значения регистров 6 и 9 соответственно, В блоке 18 по поступающему из регистра 10 значению Xо формируется выражение t (Хо). Одноврек)енно на блок умножения 20 поступает значение регистра 11, где умножаетеся нп числг)ЛХ, поступившее из регистра 12. В пятом такте число, сформированное на блоке умножения 20, записывается в регистр 14, в регистр 13 записывается значение с выхода блока 18, Содержимо этих регистров поступает на сумматор 2 в котором формируется выражение F (Хо) + Л)(Р (Хо) + ПХо) /2), т.е. искомое чение фукциир{)(). В шрстом такте это значение записы ется в регистр 15 и из него поступает на выxopVc тройства. Тактовые импульсы, поступающие на регистры устройства, вырабатываются в б ке синхронизации 23, который работает слерукицим образом. Перед началом об- работки массива чисел и в счетчике ма сийа 27 по входу 24 поступает число, равное длине массива. По сигналу Пус поступающему на триггер 29 по входу 25, этот триггер устанавливается в состояние 1, и сигнал с его выхода разрешает прохождение тактовых импуль сов через Э1юмент И 31 с генератора импульсов 30. С выхода элемента И 3 тактовые импульсы поступают на регист . ры устройства с выхода 26, управляя записью информации в эти регистры. С поступлением каждого тактового импуль са в устройстве происходит сдвиг информации на одну ступень вниз. Одновременно тактовые импульсы с элемента И 31 поступают на счетчик массива 27 и с поступлением каждого импульса из содержимого счетчика вычитается единица. Как тогазКо содержимое счетчика станет равным нулю, т.е. массив чисел обработан, на выходе элемента ИЛИ-НЕ 28 появляется сигнал, сбрасывающий триггер 29 в состояние О, а сигнал с выхода триггера запретит прохождение тактовых импульсов через элемент И 31 на регистры устройства. Устройство работает по конвейерному принципу. В каждом такте в него вводится новый операнд и с его выходов снимается новый результат. Бьгстродействие устройства при обработке массивов чисел определяется длительностью такта, которая равна задержке в наиболее медленной ступени устройства. Такой ступенью в данном устройстве- является блок умножения. Поэтому быстро действие устройства равно Т ЬудднБыстродействие же прототипа не превышает Т, 2 (С БЫБ,..) , что при обработке массивов чисел предлагаемоеустройство выгодно, отличается от прототипа. По сравнению с прототипом быстродействие увеличено в Tj 2 (-fc вьш +Ьсу1У - -t-v/HH) Т -Ь, j-Bblg fccyM Если использовать для построения данного устройства элементы 155 серии и обрабатывать на нем 16-разрядные числа, то CVM-- выБ --fooHc.-ty - 2ОО НС и 7 воо НС Т2ООНС изобретения о р м у л а 1. Конвейерное устройство для вычисления элементарных фукций, содержащее четыре регистра, первый блок умножения, первый сумматор и три блока памяти, причем выход первого регистра соединен со входом первого блока памяти, выход первого сумматора подключен ко входу второго регистра, выход которого является выходом ус1 ройства, входы первого и третьего регистров соединены с входом устройства, от личающееся тем, что, с целью повышения быстродействия, в него введены одиннадцать регистров, второй блок умножения, второй сумматор и блок синхронизации, причем входы четвертого, пятого и шестого регистров соединены соответственно с выходами первого регистра, первого блока памяти и третьего регистра, выходы седьмого, восьмого, девятого и десятого регистров соединены соответственно с выходами четвертого регистра, второго блока памяти, первого блока умножения и шестого регистра, выход которого соединен с первым входом первого блока умножения, второй вход которого подключен к ыходу пятого регистра, вход второго блока памяти соединен с выходом чегtертого регистра, входы одиннадцатого, двенадцатого и тринаЪдатого регистров оединены соответственно с выходами едьмого, десятого регистров и-второго умматора, первый и второй входы котоого подключены соответственно к выходам BOCbMdbo и девятого регистров, выод одиннадцатого регистра через третий лок памяти соединен с входом четыр 8надоатого регистра, выход которого соединен :с первым входом первого суммагора, второй вход которого через пятнадцатый регистр подключен к выходу второго блока умножения, первый и второй входы которого соединены соответственно с выходами двенадцатого и тринаршатого регистров, выхор блока синхронизации соединен с тактовыми входами всех регис . ров, первый вход блока синхронизации является входом величины массива устройства, а второй - входом запуска, 2, Устройство по п. I, от л и ч а ю щ е е с я тем, что блок синхронизации содержит счетчик массива, триггер, генератор импульсов и .элементы И и ИЛИ-НЕ причем установочный вход счетчика массива соединен с первым входом блока син 2 хронизации, выходы .разрядов счетчика массива соединены с входами элемента ИЛИ- НЕ, выход которого соединен с первым входом триггера, второй вход Которого соединен со вторым входом блока синхронизации, выход триггера подключен к первому входу элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И соединен с выходом блока синхронизации и счетным входом счетчика массива. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР N 674032, кл. G06F 15/34, 1979. 2.,Заявка N 2415788, кя. G06 F 1/02, 20.О4.77 (прототип).

23

//

i

/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1982 |

|

SU1027732A1 |

| Устройство для вычисления скользящего среднего | 1988 |

|

SU1642478A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Генератор случайного процесса | 1982 |

|

SU1020820A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

15

29

Jff

Фиг. I

//

Авторы

Даты

1981-12-07—Публикация

1980-01-21—Подача