ВЫХОДНЫМ клеммами, вторые выходы--со вторЫМм входами блока управлскля, вторыми сходами адаптивного коммутатора, со входами второго элемента ИЛИ, с первыми входами вторых элементов И, с первыми входами иятых элементов И и с иервыми инверсными входами третьих элементов И, выходы которых соединены со входами пе)едаюи1::х блоков. Вторые вход( третьих элементов И соедииены со вторыми выход-Ми накопителей сообщений и со вторыми входами вторых элементов И, выходы которых соединены с входа.ми третьего элемент: ИЛИ, выход которого соединен со BTOJ);;входом иервого элемента ИЛИ и со втор: -v входом буферного коммутатора, второй ход которого соединен с нервым входом чс-твертого элемента И, второй вход которо соединен с выходом второго элемента . Вьход ствертого элемеита И соединен со входом генератора тактовой астоты, которого соединен со вторыми входалги иг;Т1ЛХ элементов И, соедииеиных выходами сгответствеиио со вторыми входами н м-сопитслей сооби1еиий. Адаитивиый ком1 :утатор с;:держит дешифраторы, блоки делеии, ггистрь режимов, формирователь выходных сигналов, бло;-;и у:,;иоже И1Я и элементы И. /iepBbie входы адаитивного коммутатора соединены со входами дешифраторов, выходы которых соединены с первыми входам:; соответствующих блоков деления, втоnbic входы которых соединены с в;;:ходам;: блоков умио}кеиия, выходы - с иерввтми гходами формирователя выходив1х сигналю:;, выход которого соединен е выходом п;;китивиого коммутатора. Выходы регистров iieXvXMOi; ;-;сд:::;:: с .: .:, . ис1) входами эдемеитов PI, вторые Б.ХОдь: кото );:х оедииеиь со вторыми вхо/.ам адаитивного коммутатора и вторылп: вхсда п форлтирователя вв1ходиь х сигиа,ов. Выхо.ты элементов И соединены с соот-етствуС/дилп входами блоков умножения.

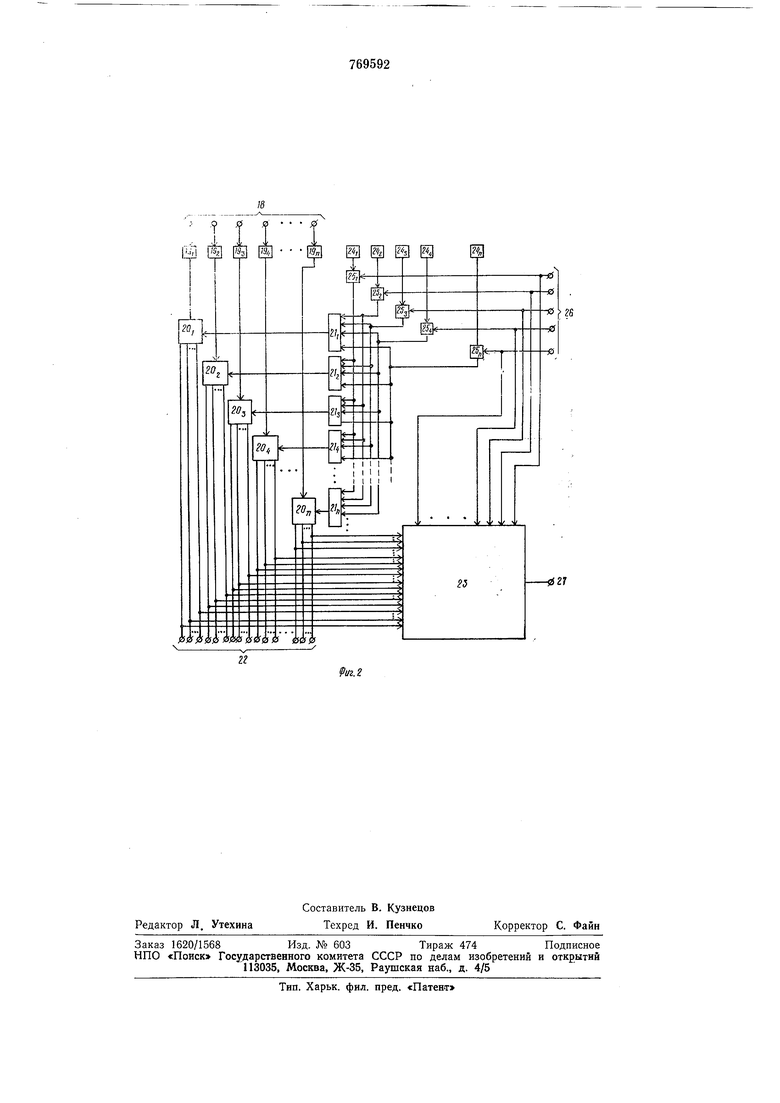

На фиг. I ириведена структурная схема многоканального коммутатора.

Ои содержит информационные блоки /1 - /„, буфериый коммутатор 2, элемеит ИЛР 3, дешифратор 4, блок уиравлеиия 5, элементы И б ,-6,, иакоиители информаи,ин 7|-7;,, элементы И 8i-5„, элементы И 5i-9п, нередаюидие блоки 10 -10,,, выходигге //, .смемт ИЛР 12, гчагТ1 ;;;ЫЙ 1:оммутатор 13, элемент И 14, генератор тактовой частоты /5, элементы И J6,-/6,, и эг:еме гг ИЛИ 17.

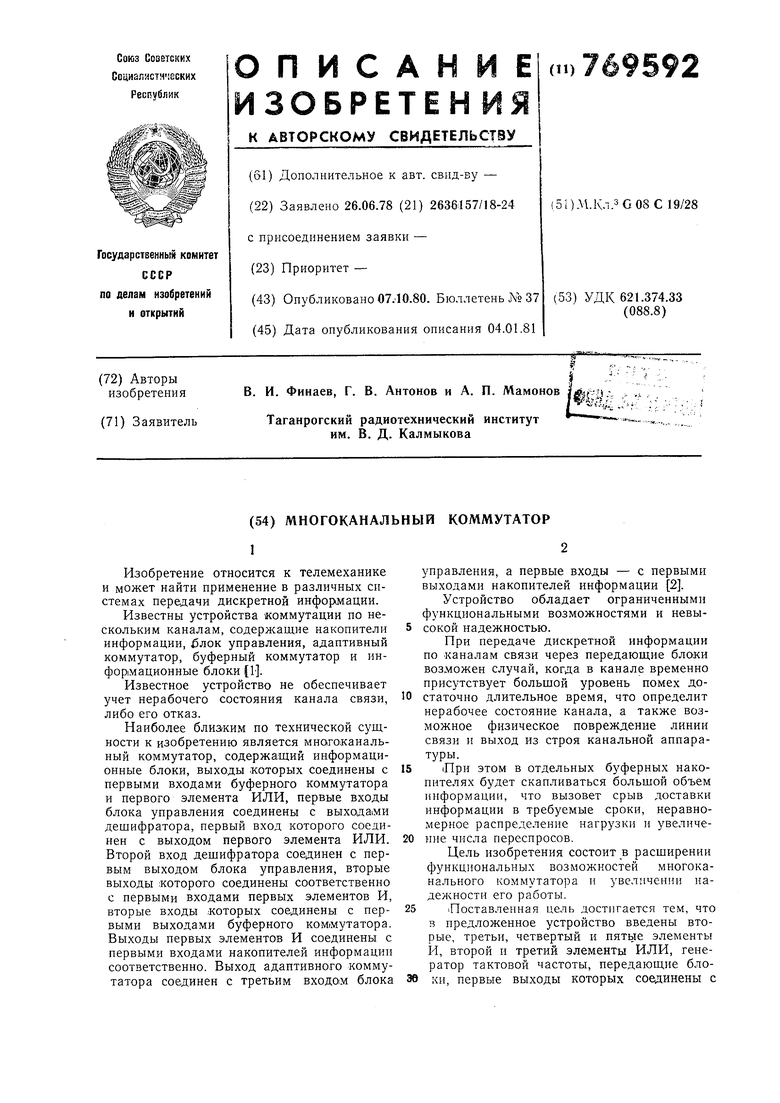

иервые входы 18, дешифраторы /5 - /5„, блоки деления ,,, бло:кн умножения 21,-21„, выходы блоков деления 22, формирователь выходных сигналов 23, региетры режимов ,;, элемеиты И .25,-

25„, вторые входы 26 и выход 27 адаитивного коммутатора.

Многоканальный коммутатор работает следующим образом.

От информационных блоков /, число которых в общем случае может быть п, еообщеиия иостунают на буферный коммутатор 2 и через элемент ИЛИ 3 на дешифратор 4, в котором деш фрируетея адрес

наз1ачения сообщения и в соответствии е иим выставляется сигнал входного уиравЛгиО:1 пе действия . иа первые вхо;;; олока уиравления 5 в соответствии с некоторой априорно заданной функцией х f(a), где

а 6 Л -- множество входящих а.чресов. Ч1сло выходов буферного коммутатора т равно чнслу иаиравлещ к{)мм таи;;1:, соотношение между т и п возможно ирактически любое, в зависг мости от

, входя:1;их (п; п выходящих (//г; каналов с.язи и те ;мии:::лОБ ис;тс;и:1;ч,оз и ир;к-мииков, иодключениых к узлу коммуглц. ::. Блок П;эавлс 1ИЯ :1с;;гет i;a второй вход дешифратора 4 запрет иа ирием иосдсду;ои1их сооби;,е;п:й иа время, разиое riU.MCHH ко лмутаа;п; раисе гюстуиивие-и сообил:1;:я ;: мно1ак; чаль:ллй КОММУТЙТО:). U) io: 42i:::ii холиого }:pas;: :,oi;-ero вэз;:, блок уиравлеиия 5 выдает оити:,:ал:-.и:,1Й спг1ал у1; :апле1::;; (для :;с;л; г;тац н иостуииви1его еообндеппя) в лиде погси ;1:л,:а ;:;; одном из в ор:;;х выхо.Ю,. которым иоетуиает на иервый зход элемеи л 1-1 о. соответствующего выбранному бло--.п

:i;o, которое И;)0лодит в соот:;е ствугопи1й ; кпи;тель сообщений 7,-, вход которого

л;.я.; :: е выходом элемеита И 5;. Из бупсрихгч иакоилтслей иифо 3мади1 ,, со() выбираются на иередачу пе:);;дп:сл;1ми блоками 10.

В даином случае блок уиравлеиия 5

(Ь л1киио1;Д1)ует в ереде стохаст; ческо. о характера, где иараметрами среды являются (-Состояния изкоиителей (.1а11: и 7-7;,. Каждое изменение еоетояний длии очередей иакоиителей информации отенивается

адаитивиым ком-мутатором 13, который выriaer сигиал оценки в виде «Штрафа - сигнала «О либо «Иоошреиия - сигнала «1 на третий вход блока уиравления 5. Псредиогций блок 10 оиределяет состояHiie л аиаля ио еледующей ироиедурс. Посылается сигиал занроса готовности иередаюи-ей аииаратуры к ириемнод етопо е миогоканального коммутатора, ; кото то:Л передается сообп1евие. Если ответного

сигиа.ла готовности иет, то заново ,ествляетея ноеылка еигнала заироеа готов тости (до трех раз). Если ответный сигнал готовности не был иолучеи, то считается, что канал вышел из строя и иередача еообщеиий по нему невозможна, а ;ia

втором выходе соответствующей передающей аппаратуры /О появляется сигнал, который подается на соответствующие входы блока управления 5, изменяя его закон управления в данно.м многоканальном коммутаторе, и на входы адаптивного коммутатора 13, изменяя функцию синтеза оценки управляющих воздействий блока 3, а также на инвертирующий вход соответствующего третьего элемента И 9|-5„, выход которого соединен со входом данного передающего блока 10, запрещая подачу на него сообщений. Одновременно с помощью элементов И 5i-8-.,, 14, и элементов ИЛИ 12, 17 генератор тактовой частоты 15 осуществляет перераспределение сообщений еоответствующего накопителя информации , связанного с установивщим неисправность канала передающим блоком, по остальным буферным накопителям информации следующим образом. Сигнал неисправности чанала через элемент ИЛИ 12 подается на первый вход четвертого элемента И 14. Когда на последпе1М выходе 27 адаптивного коммутатора 2 появится сигнал, то он подается на второй вход элемента И 14, элемент И 14 открывается и разрещает работу генератора 15, который через соответетвующий пятый элемент И 16 -16„ считывает по второму входу сообщения соответствующего накопителя информации ,, через соответствующий второй элемент И и элемент ИЛИ 17 на второй вход буферного коммутатора 2 и через элемент ИЛИ 3 на вход дешифратора 4. Сообщения, перераспределяемые из соответствующего накопителя инфорМации 7,-7,,. рассматриваются блоком управления 5, как вновь поступивщие сообщения и распределяются им по другим накопителям информации, связанным е исправными каналами по направлениям передач (выходным п Т1нам //).

Рассмотрим работу адаптивного коммутатора 13. Синтез сигналов «Штраф (отсутствие импульса -«О) за неверное действие блока управления 5 и «Поощрения (наличие импульса-к 1) за правильное действие блока управления 5 проводится из оценки состояний очередей в накопителях информации 7i-7„ по следующим соображениям. Пусть Г; - длина очереди в г-ном накопителе 7 сообщений

(г 1, т), причем Г .--- где -

загрузка канала г-го направления, а ожидаемая длительность задержки сообщений

ПО (-МУ направлению передач oj/1:-- ,

где pi - длительность передачи сообщений по /-му направлению. Стратегия поведения бло.ка управления 5 состоит в осуществлении одинаковых задержек по всем шинам

11, т. е. cu cu2... cOm, или можнр записать

1 - Р;;,

млн

п - ,„ --- п

В.

1-р/

К

Следовательно, для выполнения условий одинаковых величин длины очередей должны выдерживаться в пропорциях

15

Л П 3;

(1)

if

и адаптивный коммутатор J3 должен проверять выполнение пропорциональных соотношений (1), и если оно нарущается после действий блока управления 5, то выдавать сигнал «Штраф, а в противном

случае - «Поощрение. Это производится следующим образом. Состояние накопителей 7 дещифрируется дещифраторами 19 и подается на блоки деления 20, на входы которых подается произведение

В от блоков умножения 21, на входы которых значения длин передач устанавливаются регистрами режимов 24. На выходах блоков деления 20 получаются величины частных от деления

Г: „ ,

-

П ,

40

Величина Л в идеальном случае должна быть равна /, однако, всегда еуществует некоторая погрешность фпнкционирования, и, Хчитывая точность решения задачи, задается величина отклонения А.4, выход за которую реального значения Л,- должен рассматриваться как неверное действие вероятного автомата блока управления 5, т. е. при Л,-, лежащем в пределах /АЛ/, выдается адаптивным .коммутатором 13 сигнал «Поощрение, а при Л,-, превышающем величину /АЛ/, адаптивный коммутатор /5 выдает сингал «Штраф. На

выходах блоков деления 20 имеется набор величин Л,- (i,tn} в виде двоичных кодов, причем, если Л,- и Л- не превышают АЛ/, то коды чисел А; и Л; равны. Сравнения выполнения условия (1) по величинам-кодов Л; осуществляется формирователем выходных сигналов 23, рсалпзуктЩ 1М функцию логического закона эквиваленсии.

По вторым входам блока управления 5

подается сигнал, согласно Котооому ме7

ияется функция управления блока 5, т. е. на те накопители, которые связаны с неиснравными каналами через передающие блоки 10 сообш,е1Н1я не полаются.

Техннко-экономнческая эффективность изобретения состоит в увеличении коэффициента живучести сети коммутации сообщений, обесиечении доставки сообщений по обходным каналам связи при неисправности нрямых каналов и учете неисппа ных каналов связи в законах управлении .ком1мутацией сообщений на сети.

Формула изобретения

1. Многоканальный коммутатор, содержащий информационные блоки, выходы которых соединены с первыми входами буферного коммутатора и первого элемента ИЛИ, первые входы блока управления соединены с выходами дещифратора, первый вход которого соединен с выходом первого элемента ИЛИ, второй вход дещифратора соединен с иервым выходом блока управления, вторые выходы которого соединены соответственно с первыми входами первых элементов И, вторые входы которых соединены с первыми выходами буферного коммутатора, выходы первых элементов И соединены с первыми входами накопителей информации соответственно, а выход адаптивного коммутатора соединен с третьим входам блО|Ка управления, первые входы адаптивного коммутатора соединены с первыми выходами ,ителей информации, отличающийся тем, что, с целью расщирения функциональных возможностей и повыщения надежности коммутатора, в него введены вторые, третьи, четвертый и пятые элементы И, второй п третий элементы ИЛИ, генератор тактовой частоты, передающие блоки, первые выходы которых соединены с выходными клеммами, вторые выходы - со вторыми входами блока управления, вторыми входами адаптивного коммутатора, с входами второго элемента ИЛИ, с первыми входами вторых элементов И, с первыми входами пятых элементов И и с первыми пн8

версными входами третьих элементов И, выходы которых соединены со входами передающих блоков, вторые входы третьих элементов И соединены со вторылш выходами накопителей сообщений и со вторыми входами вторых элементов И, выходы которых соединены с входами третьего элемента ИЛИ, выход которого соединен со вт.орым входом первого элемента ИЛИ

и со вторым входОМ буферного коммутатора, второй выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, выход четвертого

элемента И соединен с входолч генератора тактовой частоты, выход которого соединен со вторыми входами пятых элементов И, соединенных выходами соответственно со вторыми входами накопителей сообщений.

2. Коммутатор по п. 1, отличающийся тем, что адаптивный коммутатор содержит дешифраторы, блоки деления, регистры режимов, формирователь выходных сигналов, блоки ул1ножения, элементь:

И, первые входы адаптивного коммутатора соединены со входами дешифраторов, выходы которых соединены с первыми входами соответствующих блоков деления, вторые входы которых соединены с выходами

блоков умножения, выходы - с первыми входами формирователя выходных сигналов, выход которого соединен с выходом адаптивного коммутатора, выходы регистров режи1мов соединены соответственно с

первыми входами элементов И, вторые входы которых соединены со вторыми входами адаптивного коммутатора и вторымм входами формирователя выходных сигналов, выходы элементов И соединены с соответствующи.ми входами блоков умножения.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 597704, кл. G 05 В 13/00, 1978.

2 Авторское свидетельство СССР по заявке Al- 2476766-18-24, С 08 С 15/06, 1977 (прототип).

i:--.J i i

:I

2Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1978 |

|

SU765849A1 |

| Устройство для управления коммутацией сообщений по нескольким каналам передачи | 1976 |

|

SU595704A1 |

| Устройство поиска свободных направлений на сети связи | 1989 |

|

SU1688445A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для управления системой контроля цифровых схем | 1975 |

|

SU560226A1 |

| Устройство для контроля информации | 1978 |

|

SU815728A1 |

| Система контроля качества прохождения телеграфных сигналов | 1986 |

|

SU1540023A1 |

| Устройство для адресного управления коммутацией сообщений | 1977 |

|

SU708387A1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

Авторы

Даты

1980-10-07—Публикация

1978-06-26—Подача