(54) УСТРОЙСТВО для КОНТРОЛЯ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информации | 1983 |

|

SU1174928A2 |

| Устройство для контроля информации | 1972 |

|

SU474824A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство с динамическим выбором маршрутов передачи данных | 1987 |

|

SU1587529A1 |

| Устройство фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU658771A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для контроля информации на магнитных носителях или перфолентах.

Известно устройство для контроля считываемой информации, содержащее распределитель, сигналов, дешифратор, распределитель сигналов, элементы НЕ, элементы И, элементы ИЛИ и триггеры (1.

Недостаток известного устройства - невозможность контролировать непосредственно во время рабочего считывания информации.

Наиболее.близким к предлагаемому по технической сущности является устройство для контроля информации, содержащее считывающий блок, подключенный через блок формирователей к регистру и узлу блокировки, и через узел пуска-останова к блоку управления, соединенному с сумматором тактовых сигналов, узлом блокировки, счетчиком синхросигналов, подключенных к дещифратору, блоком индикации и блоком сравнения, соединенными с блоком задания контрольнойсуммы и сумматором, который подключен к дещифратору, генератору тактовых сигналов, блоку индикации, блоку

контроля гибкости и регистру; первый в.ход блока регистрации числа массивов соединен с выходом регистра, второй вход которого соединен с выходом регистра, второй вход - с одним из выходов блока управления, третий вход - с блоком задания контрольной суммы, один выход подключен к блоку индикации, другой - к блоку сравнения и блоку управления, а входы блока контроля синхросигналов соединены с выходами блока формирователей и узла блокировки, а выход подключен к блокам управления и индикации, при этом блок регистрации числа массивов содержит узел фиксации конца теста и узел выделения конца массива, вывод которого соединен с счетчиком массивов и первым входом узла фиксации конца теста, а выход счетчика массивов подключен к его второму входуС2.

Недостатком данного устройства является недостаточная достоверность контроля при определенных операциях контроля.

Цель изобретения - повышение достоверности контроля.

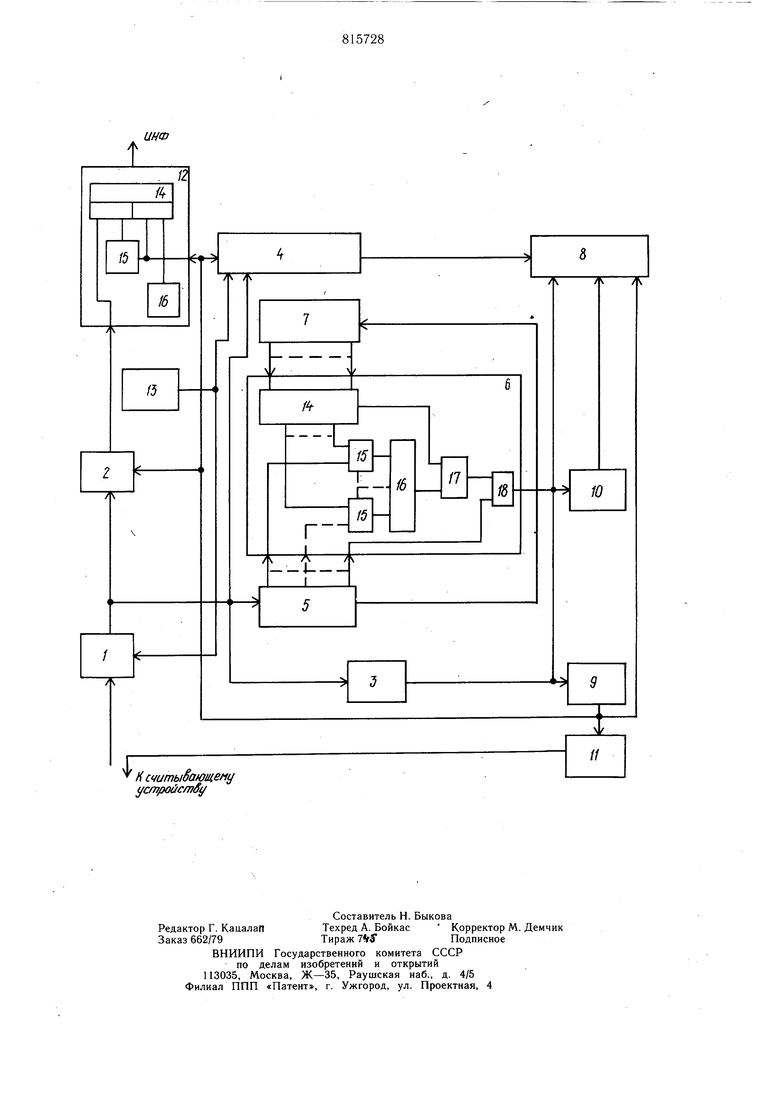

Поставленная цель достигается тем, что в устройство для контроля информации, содержащее счетчик синхросигналов, блок индикации, генератор тактовых сигналов, блок формирователей, сумматор, блок управления, блок пуска-останова, причем выход сумматора соединен с первым входом блока индикации, второй вход которого подключен к входу блока управления и выходу блока сравнения кода, вход которого объединен с первым входом сумматора, второй вход которого подключен к выходу генератора тактовых сигналов и первому входу формирователей, второй вход которого является входом устройства, первый выход устройства является выходом блока пуска-останова, вход которого подключен к третьему входу сумматора, выходу блока управления и третьему входу блока индикации, введены коммутатор, буферный накопитель, блок сравнения форматов, дешифратор и счетчик, причем выход счетчика соединен с четвертым входом блока индикации, вход счетчика соединен с четвертым входом блока индикации, вход счетчика соединен с выходом блока сравнения форматов, первая группа входов которого подключена к группе выходов счетчика синхросигналов, вход которого соединен с выходом дешифратора, группа выходов которого соединена с второй группой входов блока сравнения форматов, первый вход дешифратора подключен к выходу блока формирователей и первому входу буферного накопителя, второй вход которого объединен с первым входом коммутатора и подключен к выходу блока управления, выход буферного накопителя соединен с вторым входом коммутатора, выход которого является информационным выходом устройства. Кроме того, блок сравнения форматов содержит дешифратор теста, элементы И, группу элементов И, элемент ИЛИ и триггер, причем группа входов дешифратора теста является первой группой входов блока сравнения форматов, группа выходов дешифратора теста подключена к первым входам элементов И группы, выходы которых подключены к входам элемента ИЛИ, выход которого соединен с первым входом триггера, второй вход которого соединен с первым выходом, дешифратора теста, выход которого соединен с первым входом элемента И, второй вход которого соединен с первым входом дешифратора, остальные входы которого подключены к вторым входам элементов И группы, причем выходы дешифратора являются второй группой входов блока сравнения форматов, выходы которого являются выходом элемента И. На чертеже представлена блок-схема устройства. Устройство контроля содержит блок 1 формирователей, буферный накопитель 2, блок 3 сравнения, сумматор 4, дешифратор 5, блок 6 сравнения форматов, счетчик 7 синхросигналов, блок 8 индикации, блок 9 управления, счетчик 10, блок 11 пуска-останова, коммутатор 12, выход 13 генератора тактовых сигналов, дешифратор 14 теста, элемент 15 И, элемент 16 ИЛИ, триггер 17 и элемент 18 И. Устройство работает следуюш.им образом. В блоке 9 управления формируется сигнал пуска, поступаюший через блок 11 пуска-останова в считываюшее устройство. Информация от последнего поступает в блок 1 формирователей, где производятся необходимые преобразования входных сигналов и привязка их к частоте генератора 13 тактовых сигналов. С выхода блока 1 формирователей информация поразрядно подается в буферный накопитель 2, дешифратор 5, блок 3 сравнения и сумматор 4. Дешифратор 5 выделяет из поступающей информации служебные символы и синхросигналы. Символы поступают на соответствующие входы блока 6 форматов, а синхросигналы - на счетчик 7, выходы которого поразрядно соединены со входами дешифратора 14 теста, блока 6 сравнения форматов. Сигналы с выходов дешифраторов 5 и 14 поступают в блок 6 сравнения форматов на соответствующие входы, элементов 15 И так, что, в случае прихода символа ШС на определенном ему в контролируемом сообщении месте, на выходе одного из элементов 15 И формируется сигнал. Этот сигнал через элемент 16 ИЛИ устанавливает триггер 17 в положение, разрешающее работу элемента 18 И. Затем в случае, если за время, определяемое форматом контролируемого сообщения, на второй вход элемента 18 И с дешифратора служебных символов приходит сигнал РИ, он появляется на выходе блока и сигнализирует о соответствии формата контролируемого сообщения. В случаях, когда сигнал ШС элемента 16 ИЛИ не поступает (сигнал ШС отсутствует или приходит не на свое место) или когда триггер 17 устанавливается сигналом «Сброс с дешифратора 14 теста в положение, запрещающее работу элемента 18 И (нарушение принятых интервалов между символами РИ), сигнал РИ на выходе блока не появляется, что является признаком нарушения формата сообщения. Таким образом, число выходов дешифраторов 5 и 14, и элемента 15 И определяется числом контролируемых форматов сообщений. Выходной сигнал блока 6 сравнения форматов подается на входы счетчика 10, блока 8 индикации и блока 9 управления. Блок 3 сравнения обеспечивает посимвольную проверку входной информации и формирует сигнал управления, также поступающий в блоки индикации 8 и управления 9 и на счетчик 10. Буферный накопитель 2, емкость которого определяется максимальным числом символов в контролируемом сообщении, осуществляет посимвольное накопление информации. Сумматор 4, управляемый генератором 13 тактовых сигналов, производит посимвольное суммирование информации. Суммирование производится сначала по каждому контролируемому сообщению, а затем по сигналу с блока 9 управления полученный результат прибавляется к общей контрольной сумме. При обнаружении ощибки по сигналу с блока 6 сравнения форматов или блока 3 сравнения блок 9 управления формирует сигнал управления, поступающий в буферный накопитель 2 и коммутатор 12, где информация заменяется служебными символами. например символами «Ожидание. Этот же -сигнал через блок 11 пуска-останова останавливает считывающее устройство и запрещает в сумматоре 4 ввод суммы неправильного сообщения в общую контрольную сумму. Блок 8 индикации служит для отображения состояний счетчика 10, сумматора 4 и сигналов управления с блоков 6 и 3. Контрольная сумма в конце массива выводится из сумматора 4 в блок. 8 индикации, и оператор может сравнить полученный результат с известным. В предлагаемом устройстве может осуществляться контроль и без контрольной суммы, так как обеспечивается обнаружение обоих видов ошибок, приводящих к искажению контрольной суммы - искажение и потеря (появление) символов. Формула изобретения 1 Устройство для контроля информации, содержащее счетчик синхросигналов, блок индикации, генератор тактовых сигналов, блок формирователей, сумматор, блок управления, блок пуска-останова, причем выход сумматора соединен с первым входом блока индикации, второй вход которого подключен к входу блока управления и выходу блока сравнения кода, вход которого объединен с первым входом сумматора, второй вход которого подключен к выходу генератора тактовых сигналов и первому входу блока форми4)ователей, второй вход которого является входом устройства, первый выход устройства является выходом блока пуска-останова, вход которого подключен к третьему входу сумматора, выходу блока управления и третьему входу блока индикации, отличающееся тем, что, с целью повыщения достоверности контроля, оно содержит коммутатор, буферный накопитель, блок сравнения форматов, дешифратор и счетчик, причем выход счетчика соединен с четвертым входом блока индикации, вход счетчика соединен с выходом блока сравнения форматов, первая группа входов которого подключена к группе выходов счетчика синхросигналов, вход которого соединен с выходом дешифратора, группа выходов которого соединена с второй группой входов блока сравнения форматов, первый вход дешифратора подключен к выходу блока формирователей и первому входу буферного накопителя, второй вход которого объединен с первым входом коммутатора и подключен к выходу блока управления, выход буферного накопителя соединен с вторым входом коммутатора, выход которого является информационным выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок сравнения форматов содержит дешифратор теста, элемент И, группу элементов И, элемент ИЛИ и триггер, причем группа входов дешифратора теста является первой группой входов блока сравнения форматов, группа выходов дешифратора теста подключена к первым входам элементов И группы, выходы которых подключены к входам элемента ИЛИ, выход которого соединен с первым входом триггера, второй вход которого соединен с первым выходом дешифратора, выход которого соединен с первым входом элемента И, второй вход которого соединен с первым входом дешифратора, остальные входы которого подключены к вторым входам элементов И группы, причем выходы дешифратора являются второй группой входов блока сравнения форматов, выходы которого являются выходом элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 528571, кл. G 06 F 11/08, 1974. 2.Авторское свидетельство СССР № 474824, кл. G Об К 5/02, 1972 (прототип) .

иНФ

t

ycmpouc/nfy

Авторы

Даты

1981-03-23—Публикация

1978-11-09—Подача