1314344

12

Изобретение относится к электроннойит из следующих команд: «Начало провычислительной технике и может быть ис-верки, «Загрузка, «Тестирование, «Оппользовано в аппаратуре автоматизирован-рос состояния. Таким образом, от наконого контроля и диагностирования цифро-пителя 1 и блока 4 управления перевых узлов.г дается информация двух видов: управляюЦель изобретения - расширение функ-щие данные (команды) и собственно данциональных возможностей за счет обеспе-ные (элементарные тесты). Управляющие

чения возможности контроля цифровыхданные (команды), поступающие из накоблоков с импульсно-потенциальными вход-пителя 1, инициируют определенные дейстными воздействиями.вия устройства, а управляющие данные

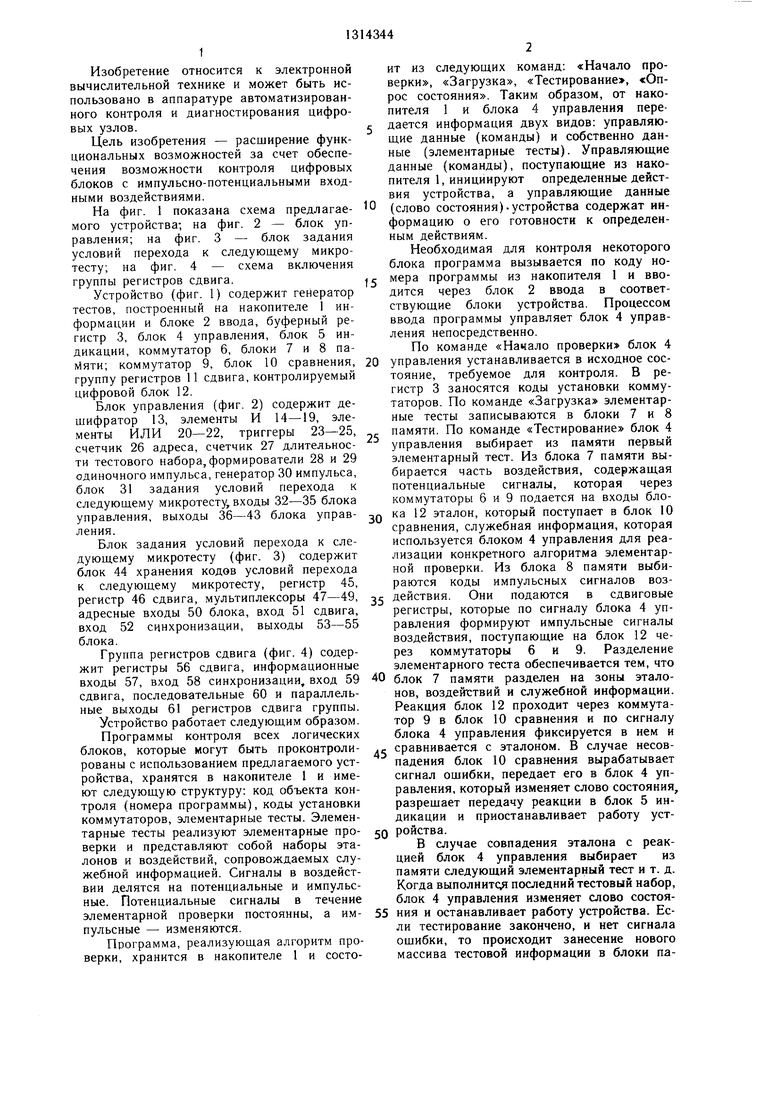

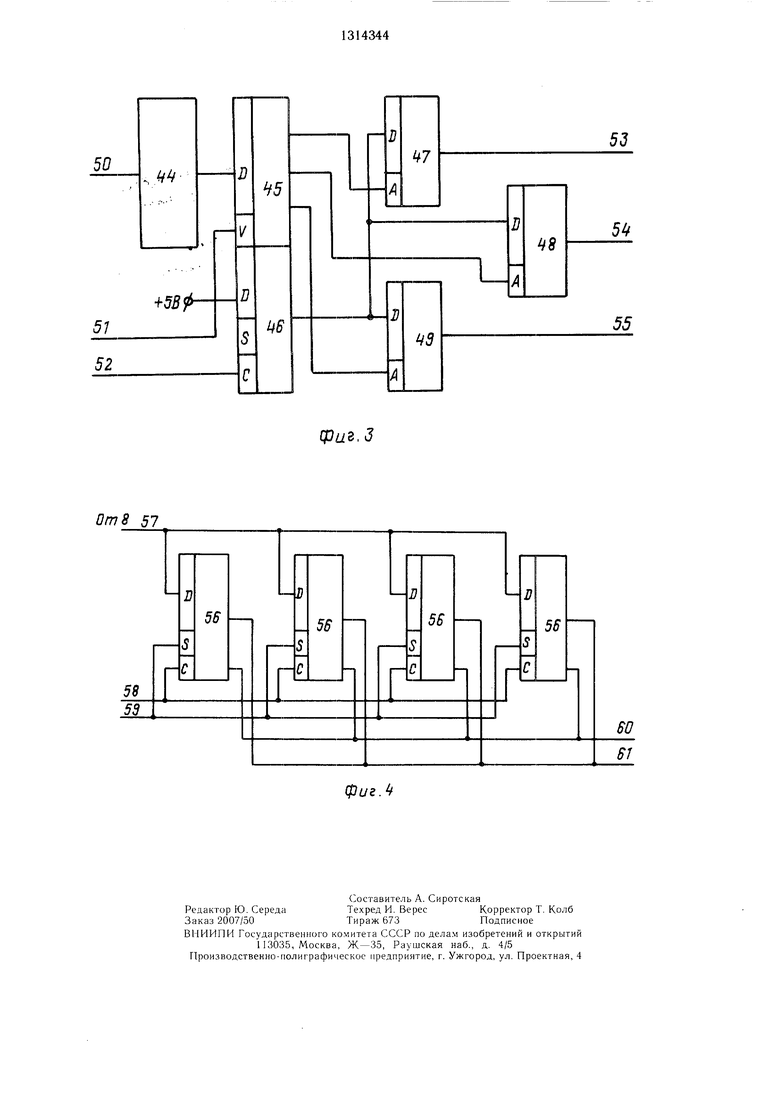

На фиг. 1 показана схема предлагае- (слово состояния).устройства содержат инмого устройства; на фиг. 2 - блок уп-формацию о его готовности к определенравления; на фиг. 3 - блок заданияным действиям.

условий перехода к следующему микро-Необходимая для контроля некоторого

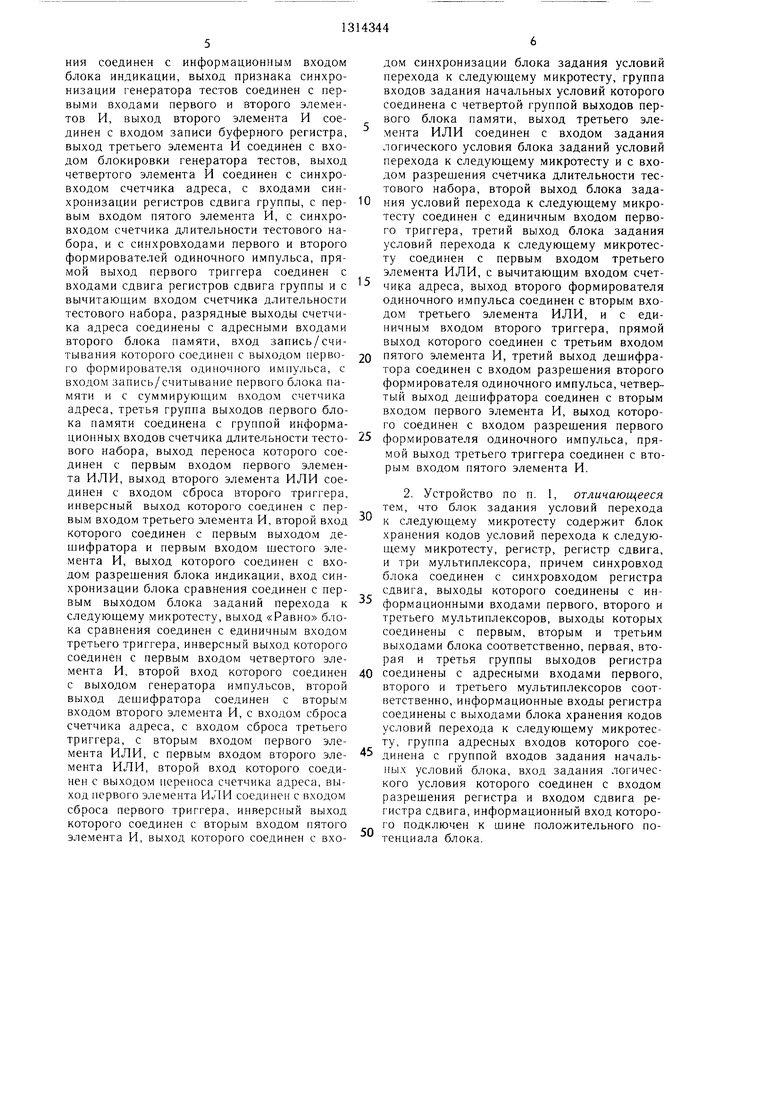

тесту; на фиг. 4 - схема включенияблока программа вызывается по коду ногруппы регистров сдвига. мера программы из накопителя 1 и ввоУстройство (фиг. 1) содержит генератордится через блок 2 ввода в соответтестов, построенный на накопителе 1 ин-ствующие блоки устройства. Процессом

формации и блоке 2 ввода, буферный ре-ввода программы управляет блок 4 управгистр 3, блок 4 управления, блок 5 ин-ления непосредственно.

дикации, коммутатор 6, блоки 7 и 8 па-По команде «Начало проверки блок 4 Мяти; коммутатор 9, блок 10 сравнения,20 управления устанавливается в исходное сос- группу регистров 11 сдвига, контролируемыйтояние, требуемое для контроля. В ре- цифровой блок 12.гистр 3 заносятся коды установки комму- Блок управления (фиг. 2) содержит де-таторов. По команде «Загрузка элементар- шифратор 13, элементы И 14-19, эле-ные тесты записываются в блоки 7 и 8 менты ИЛИ 20-22, триггеры 23-25, памяти. По команде «Тестирование блок 4 счетчик 26 адреса, счетчик 27 длительное-управления выбирает из памяти первый ти тестового набора,формирователи 28 и 29элементарный тест. Из блока 7 памяти вы- адиночного импульса, генератор 30 импулЕ са,бирается часть воздействия, содержащая блок 31 задания условий перехода кпотенциальные сигналы, которая через следующему микротесту, входы 32-35 блокакоммутаторы 6 и 9 подается на входы бло- управления, выходы 36-43 блока управ-- Q ка 12 эталон, который поступает в блок 10 ления.сравнения, служебная информация, которая Блок задания условий перехода к еле-используется блоком 4 управления для реа- дующему микротесту (фиг. 3) содержитлизации конкретного алгоритма элементар- блок 44 хранения кодов условий переходаной проверки. Из блока 8 памяти выби- к следующему микротесту, регистр 45,раются коды импульсных сигналов воз- регистр 46 сдвига, мультиплексоры 47-49, действия. Они подаются в сдвиговые адресные входы 50 блока, вход 51 сдвига,регистры, которые по сигналу блока 4 уп- вход 52 синхронизации, выходы 53-55равления формируют импульсные сигналы блока.воздействия, поступающие на блок 12 че- Группа регистров сдвига (фиг. 4) содер-рез коммутаторы 6 и 9. Разделение жит регистры 56 сдвига, информационныеэлементарного теста обеспечивается тем, что входы 57, вход 58 синхронизации, вход 5940 блок 7 памяти разделен на зоны этало- сдвига, последовательные 60 и параллель-нов, воздействий и служебной информации, ные выходы 61 регистров сдвига группы.Реакция блок 12 проходит через коммута- Устройство работает следующим обра.зом.тор 9 в блок 10 сравнения и по сигналу Программы контроля всех логическихблока 4 управления фиксируется в нем и блоков, которые могут быть проконтроли-дс сравнивается с эталоном. В случае несов- рованы с использованием предлагаемого уст-падения блок 10 сравнения вырабатывает ройства, хранятся в накопителе 1 и име-сигнал ощибки, передает его в блок 4 уп- ют следующую структуру: код объекта кон-равления, который изменяет слово состояния, троля (номера программы), коды установкиразрешает передачу реакции в блок 5 ин- коммутаторов, элементарные тесты. Элемен-дикации и приостанавливает работу уст- тарные тесты реализуют элементарные про-jO РОЙства.

верки и представляют собой наборы эта-В случае совпадения эталона с реаклонов и воздействий, сопровождаемых слу-цией блок 4 управления выбирает из

жебной информацией. Сигналы в воздейст-памяти следующий элементарный тест и т. д.

ВИИ делятся на потенциальные и импульс-Когда выполните последний тестовый набор,

ные. Потенциальные сигналы в течениеблок 4 управления изменяет слово состояэлементарной проверки постоянны, а им-55 ния и останавливает работу устройства. Еспульсные - изменяются.ли тестирование закончено, и нет сигнала

Программа, реализующая алгоритм про-ошибки, то происходит занесение нового

верки, хранится в накопителе 1 и состо-массива тестовой информации в блоки памяти, либо проверка данного объекта контроля заканчивается. При наличии сигнала ошибки тестирование заканчивается. Блок 4 управления работает следующим образом. Команды 33 из блока 2 ввода декодируются дешифратором 13. Командой «Начало проверки обнуляется счетчик 26 адреса и триггеры 23-25. Триггер 24 разрешает прохождение синхросигналов задаюш.его генератора 30 через элемент И 16 на счетчики 26 и 27 и элемент И 17. Прохождение синхросигналов через элемент И 17 запрещено триггером 23. Сигнал 36 записи в регистр 3 формируется элементом И 14 из сигнала 32 сопровождения данных из бло10

станет равным нулю, сбрасывается триггер 23, который запирает элемент И 17 и выдает сигнал о конце тестирования.

Формула изобретения

I. Устройство для контроля цифровых блоков, содержащее генератор тестов, первый и второй коммутаторы, блок сравнения, первый блок памяти, буферный регистр и блок управления, содержащий счетчик адреса, дешифратор, генератор импульсов, пять элементов И, два элемента ИЛИ, причем разрядные выходы счетчика адреса соединены с адресными входами первого

ка 2 ввода. Триггер 25 разрешает запись 5 блока памяти, первая группа выходов пер- в группу регистров сдвига сигналом 41. По команде «Загрузка сигналом 32 сопровождения данных через элемент И 15 запускается формирователь 28 одиночного импульса, который формирует сигнал 37 завого коммутатора является группой выходов устройства для подключения к группе входов контролируемого цифрового блока, первая группа информационных входов первого коммутатора является группой в.хописи в блоки 7 и 8 памяти. Запись произ- 20 доз устройства для подключения к груп- водится по адресу, получаемому на выходепе выходов контролируемого цифрового бло38. Этим же сигналом содержимое счет-ка, отличающееся тем, что, с целью расчика 26 адреса увеличивается на единицу.ширения функциональных возможностей.

Командой «Тестирование запускается фор-за счет обеспечения возможности контроля

мирователь 29 одиночного импульса. Своим 25 цифровых блоков с импульсно-потенциальными входными воздействиями, устройство дополнительно содержит второй блок памяти, группу регистров сдвига, блок индикации, а блок управления содержит три триггера.

сигналом он взводит блок 31, записывает код длительности выполнения микрокоманды в счетчике 27 и устанавливает триггер 23, который разрешает прохождение синхросигналов через элемент И 17. Подаваемый

два формирователя одиночного импульса.

на блок 31 адрес микрокоманды и код ЗО счетчик длительности тестового набора.

шестой элемент И, третий элемент ИЛИ и блок задания условий перехода к следующему микротесту, причем группа выходов признака адреса вектора тестового набора генератора тестов соединена с группой

длительности выполнения микрокоманды представляют собой служебную информацию поступающую из блока 7 памяти на вход 35. В соответствии с выбранной микрокомандой блок 31 вырабатывает определенную

последовательность сигналов, реализующих 35 информационных входов буферного регистра.

процесс тестирования, устанавливает триггер 25, который разрешает сдвиг 41 в регистрах по сигналу 43 с выхода задающего генератора, устанавливает счетчик 27 в режиме вычитания и запрещает

группа выходов признака тестового слова, генератора тестов соединена с группами информационных входов первого и второго блоков памяти, группа выходов признака кода тестового набора генератора тестов

прохождение синхросигналов через элемент40 соединена с группой информационных входов

И 17. Когда содержимое счетчика 27дешифратора, первая и вторая группы выстанет равно нулю, триггер 25 сбрасывается,ходов буферного регистра соединены с групсдвиг 41 в регистре 11 развертки прекра-па.ми управляющих входов первого и второго

щается, а блок 31 продолжает вырабакоммутаторов соответственно, группа выхотывать временную последовательность. Сиг- дов второго коммутатора соединена с второй

налом с выхода 42 блока 31 опрашивается блок 10 сравнения. В случае несравнения сигнал ошибки из блока 10 сравнения приходит на вход 34 и устанавливает триггер 24, который запирает элемент И 16 и выдает сигнал ошибки 40, поступающий в блок 5 индикации. В случае сравнения эталона и реакции триггер 24 сохраняет нулевое состояние, блок 31 вырабатывает сигнал, который у.меньщает содержимое счетчика 26 адреса на единицу и через

группой информационных входов первого коммутатора, вторая группа выходов которого соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого IJQ соединена с первой группой выходов первого блока памяти, вторая группа выходов которого соединена с первой группой ин- формационны.х входов второго коммутатора, вторая группа информационных входов которого соединена с группой последовательэлемент ИЛИ 22 заносит код длительности55 ных и параллельных выходов регистров

следующей микрокоманды в счетчик 27 исдвига группы, информационные входы

взводит блок 31. Далее работа схемы нов-которых соединены с выходами второго блоторяется. Когда содержимое счетчика адресака памяти, выход «Неравно блока сравне0

станет равным нулю, сбрасывается триггер 23, который запирает элемент И 17 и выдает сигнал о конце тестирования.

Формула изобретения

I. Устройство для контроля цифровых блоков, содержащее генератор тестов, первый и второй коммутаторы, блок сравнения, первый блок памяти, буферный регистр и блок управления, содержащий счетчик адреса, дешифратор, генератор импульсов, пять элементов И, два элемента ИЛИ, причем разрядные выходы счетчика адреса соединены с адресными входами первого

5 блока памяти, первая группа выходов пер-

блока памяти, первая группа выходов пер-

вого коммутатора является группой выходов устройства для подключения к группе входов контролируемого цифрового блока, первая группа информационных входов первого коммутатора является группой в.ходоз устройства для подключения к груп- пе выходов контролируемого цифрового блодва формирователя одиночного импульса.

счетчик длительности тестового набора.

счетчик длительности тестового набора.

шестой элемент И, третий элемент ИЛИ и блок задания условий перехода к следующему микротесту, причем группа выходов признака адреса вектора тестового набора генератора тестов соединена с группой

группа выходов признака тестового слова, генератора тестов соединена с группами информационных входов первого и второго блоков памяти, группа выходов признака кода тестового набора генератора тестов

соединена с группой информационных входов

коммутаторов соответственно, группа выходов второго коммутатора соединена с второй

группой информационных входов первого коммутатора, вторая группа выходов которого соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого соединена с первой группой выходов первого блока памяти, вторая группа выходов которого соединена с первой группой ин- формационны.х входов второго коммутатора, вторая группа информационных входов коорого соединена с группой последовательных и параллельных выходов регистров

НИИ соединен с информационным входом блока индикации, выход признака синхронизации генератора тестов соединен с первыми входами первого и второго элементов И, выход второго элемента И соединен с входом записи буферного регистра, выход третьего элемента И соединен с входом блокировки генератора тестов, выход четвертого элемента И соединен с синхро- входом счетчика адреса, с входами синхронизации регистров сдвига группы, с первым входом пятого элемента И, с синхро- входом счетчика длительности тестового набора, и с синхровходами первого и второго формирователей одиночного импульса, прямой выход первого триггера соединен с входами сдвига регистров сдвига группы и с вычитающим входом счетчика длительности тестового набора, разрядные выходы счетчика адреса соединены с адресными входами второго блока памяти, вход запись/считывания которого соединен с выходом первого формирователя одиночного импульса, с входом запись/счить вание первого блока памяти и с суммирующим входом счетчика адреса, третья группа выходов первого блока памяти соединена с группой информационных входов счетчика длительности тестового набора, выход переноса которого соединен с первым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с входом сброса второго триггера, инверсный выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с первьЕм выходом де- щифратора и первым входом щестого элемента И, выход которого соединен с входом разрешения блока индикации, вход синхронизации блока сравнения соединен с первым выходом блока заданий перехода к следуюц ему микротесту, выход «Равно блока сравнения соединен с единичным входом третьего триггера, инверсный выход которого соединен с первьЕм входом четвертого элемента И, второй вход которого соединен с выходом генератора импульсов, второй выход дещифратора соединен с вторым входом второго элемента И, с входом сброса счетчика адреса, с входом сброса третьего триггера, с вторым входом первого элемента ИЛИ, с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом переноса счетчика адреса, выход первого элемента ИЛИ соединен с входом сброса первого триггера, инверсный выход которого соединен с вторым входом пятого элемента И, выход которого соединен с входом синхронизации блока задания условий перехода к следующему микротесту, группа входов задания начальных условий которого соединена с четвертой группой выходов первого блока памяти, выход третьего элемента ИЛИ соединен с входом задания логического условия блока заданий условий перехода к следующему микротесту и с входом разрещения счетчика длительности тестового набора, второй выход блока задания условий перехода к следующему микротесту соединен с единичным входом первого триггера, третий выход блока задания условий перехода к следующему микротесту соединен с первым входом третьего элемента ИЛИ, с вычитающим входом счетчи{са адреса, выход второго формирователя одиночного импульса соединен с вторым входом третьего элемента ИЛИ, и с единичным входом второго триггера, прямой выход которого соединен с третьим входом

пятого элемента И, третий выход дешифратора соединен с входом разрещения второго формирователя одиночного импульса, четвертый выход дещифратора соединен с вторым входом первого элемента И, выход которого соединен с входом разрещения первого

формирователя одиночного импульса, прямой выход третьего триггера соединен с вторым входом пятого элемента И.

2. Устройство по п. 1, отличающееся тем, что блок задания условий перехода

к следующему микротесту содержит блок хранения кодов условий перехода к следующему микротесту, регистр, регистр сдвига, и три мультиплексора, причем синхровход блока соединен с синхровходом регистра сдвига, выходы которого соединены с информационными входами первого, второго и третьего мультиплексоров, выходы которых соединены с первым, вторым и третьим выходами блока соответственно, первая, вторая и третья группы выходов регистра

соединены с адресными входами первого, второго и третьего мультиплексоров соответственно, информационные входы регистра соединены с выходами блока хранения кодов условий перехода к следующему микротесту, группа адресных входов которого сое

динена с группой входов задания начальных условий блока, вход задания логического условия которого соединен с входом разрещения регистра и входом сдвига регистра сдвига, информационный вход которого подключен к шине положительного по- тенциала блока.

сри. 3

От 8 57

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

Изобретение отиосится к области автоматики и вычислительной техники и м. б. использовано для контроля цифровых узлов и блоков. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля цифровых блоков с им- пульсно-потенциальными входными воздействиями. Устройство содержит генератор тестов, два коммутатора, блок сравнения, два блока памяти, буферный регистр, блок -управления, группу регистров сдвига, блок заданий условий перехода к следующему микротесту. В зависимости от типа контролируемого цифрового блока генератор тестов вводит в два блока памяти коды об импульсных и потенциальных воздействиях. В регистрах сдвига происходит непосредственное временное формирование импульсных воздействий. Отклик сравнивается с эталоном, хранящие в блоке, где записываются потенциальные воздействия. 1 з. п. ф-лы, 4 ил. S СО ОО 4 4

| Многоканальное устройство для тестового контроля | 1974 |

|

SU516039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-30—Публикация

1986-03-12—Подача