Изобретение относится к вычислительной технике и предназначено для тестового контроля и диагностики цифровых узлов, приборов, пультов и т.п.

Цель изобретения - расширение области применения за счет обеспечения проверки цифровых узлов с независи -. мой синхронизацией и произвольными начальными состояниями.

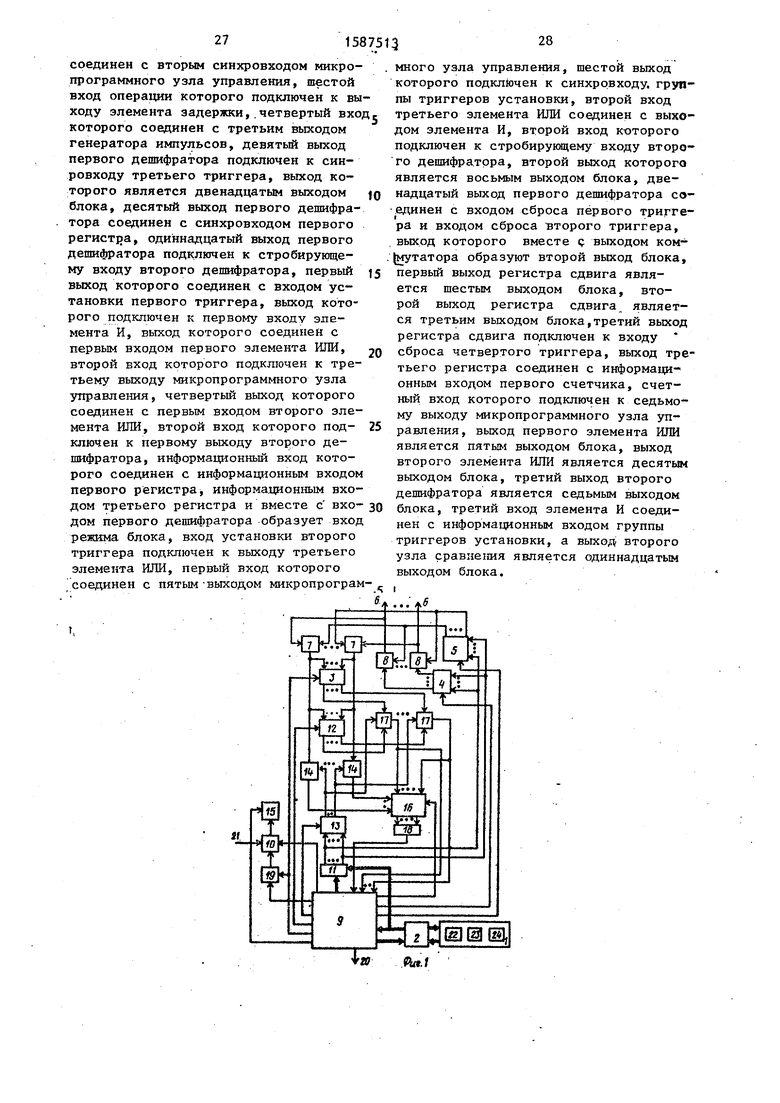

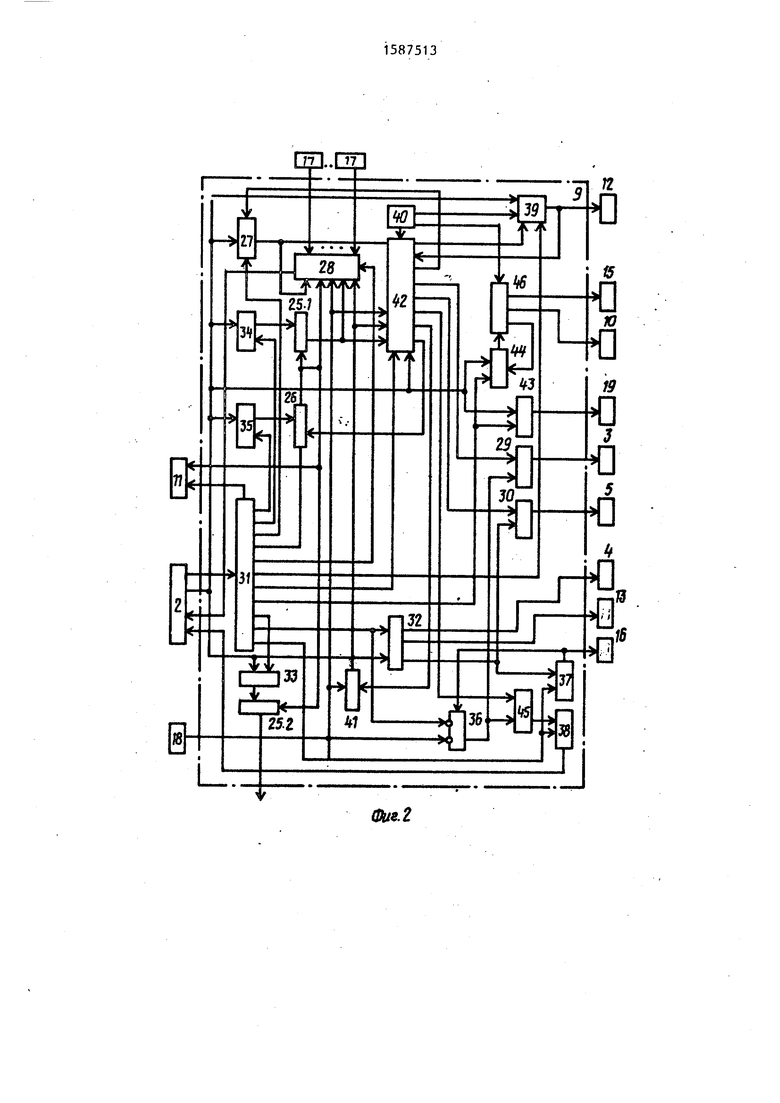

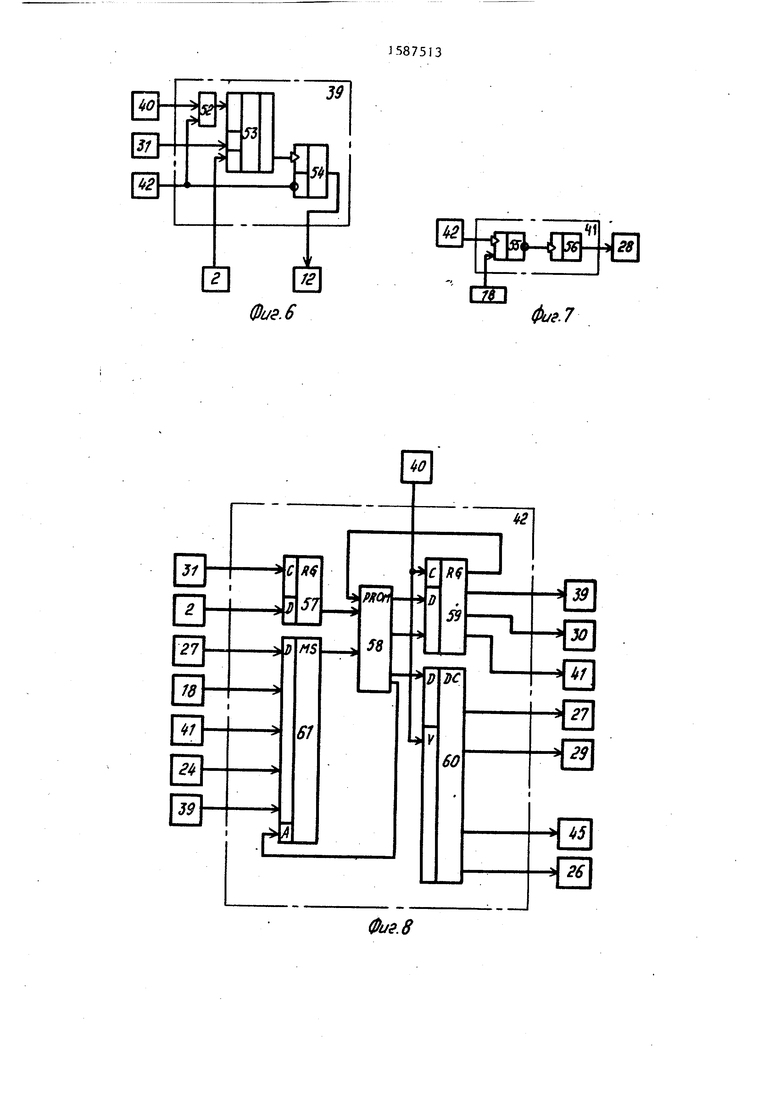

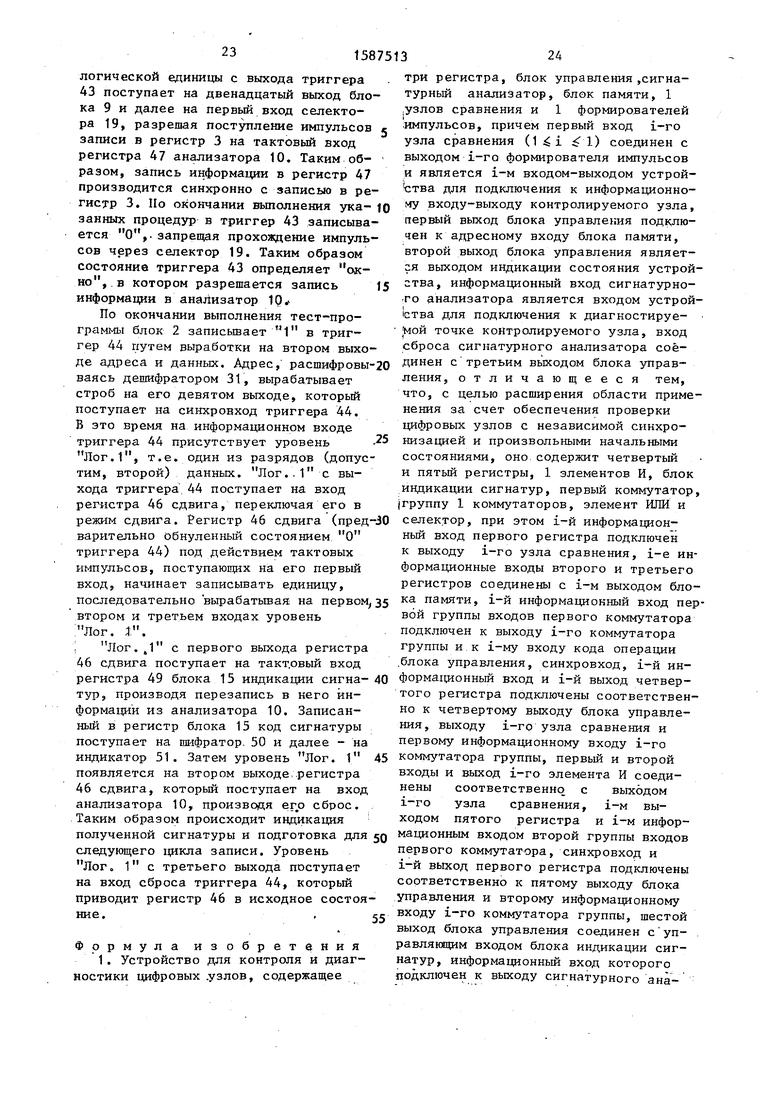

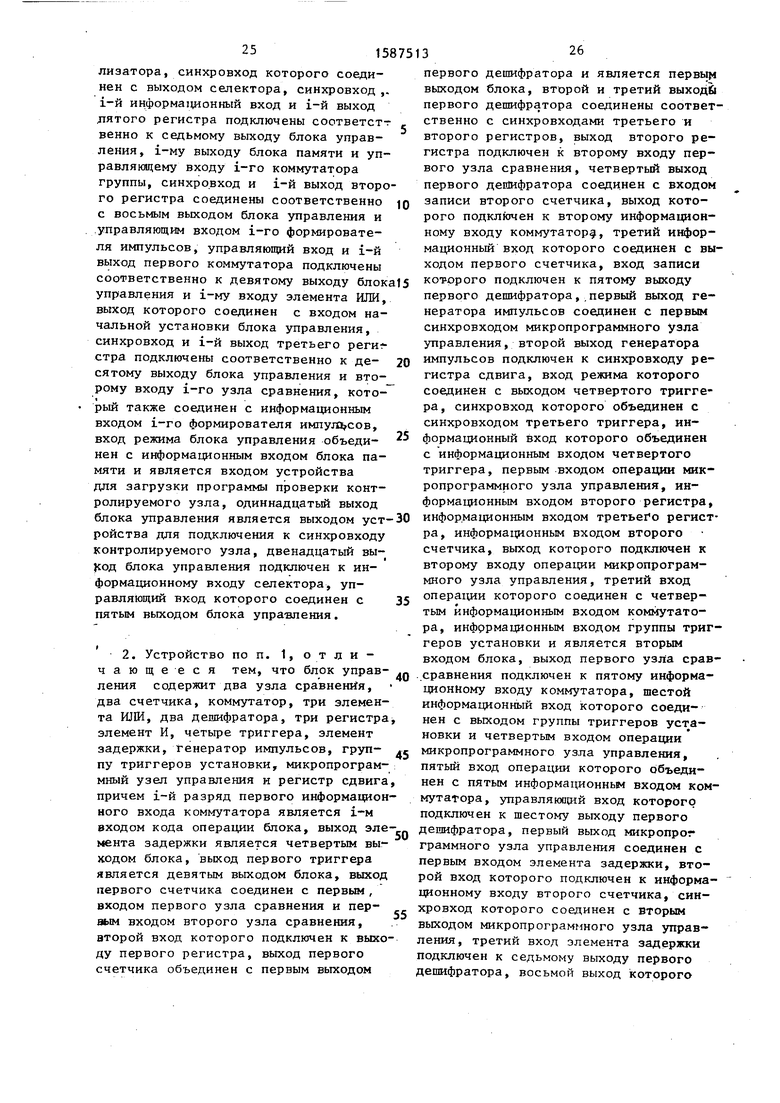

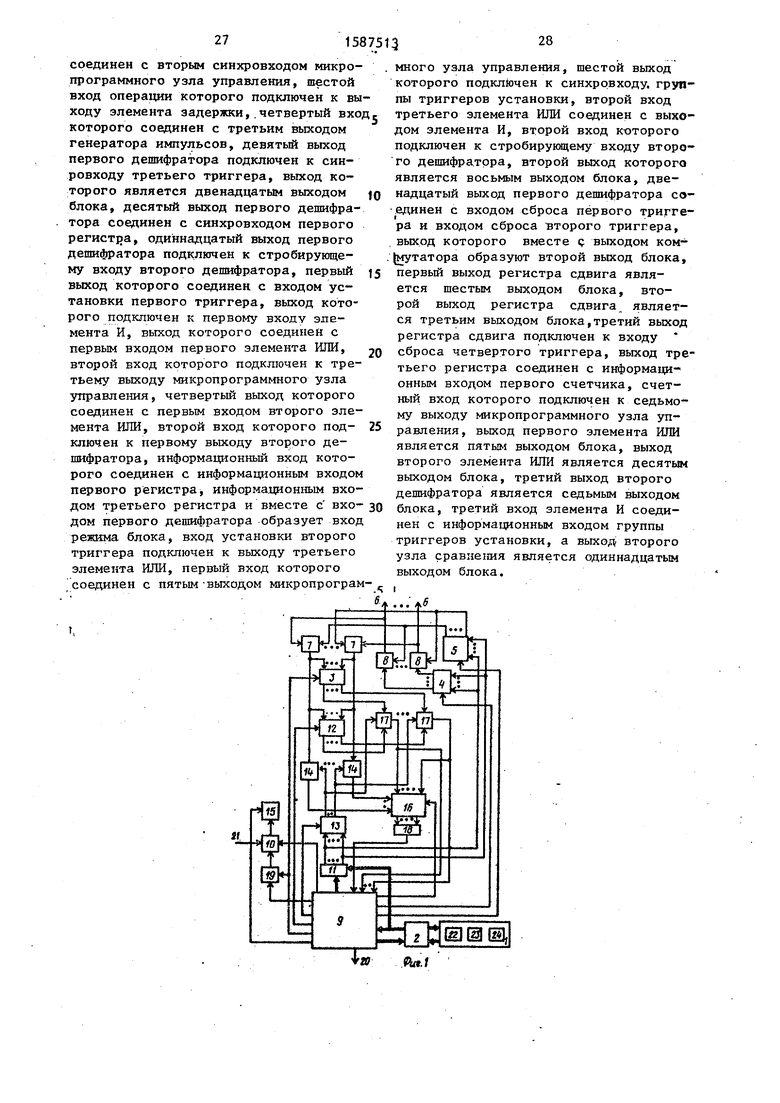

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг, 3 - алгоритм генерации тест-наборов; на фиг. 4 - пример вьтолнения сигнатурного анализатора; на фиг.5 - пример выполнения блока индикации сигнатур ; на фиг. 6 - пример выполнения элемента задержки; на фиг. 7 - пример выполнения группы триггеров устаио

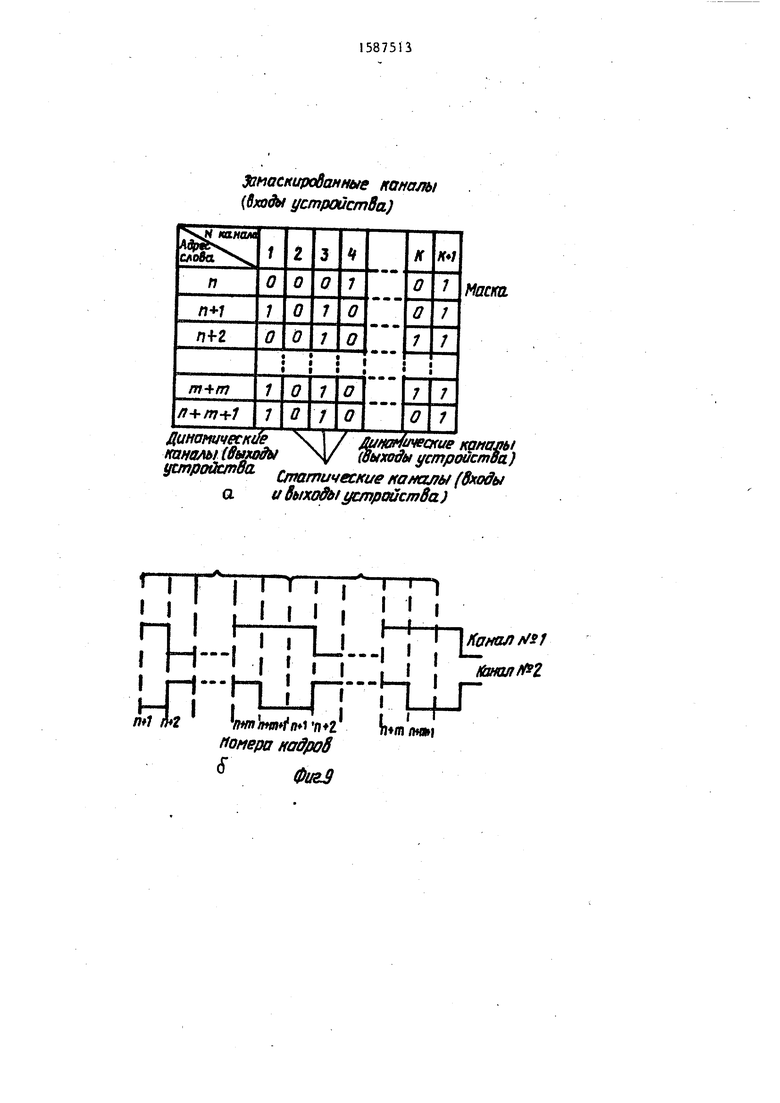

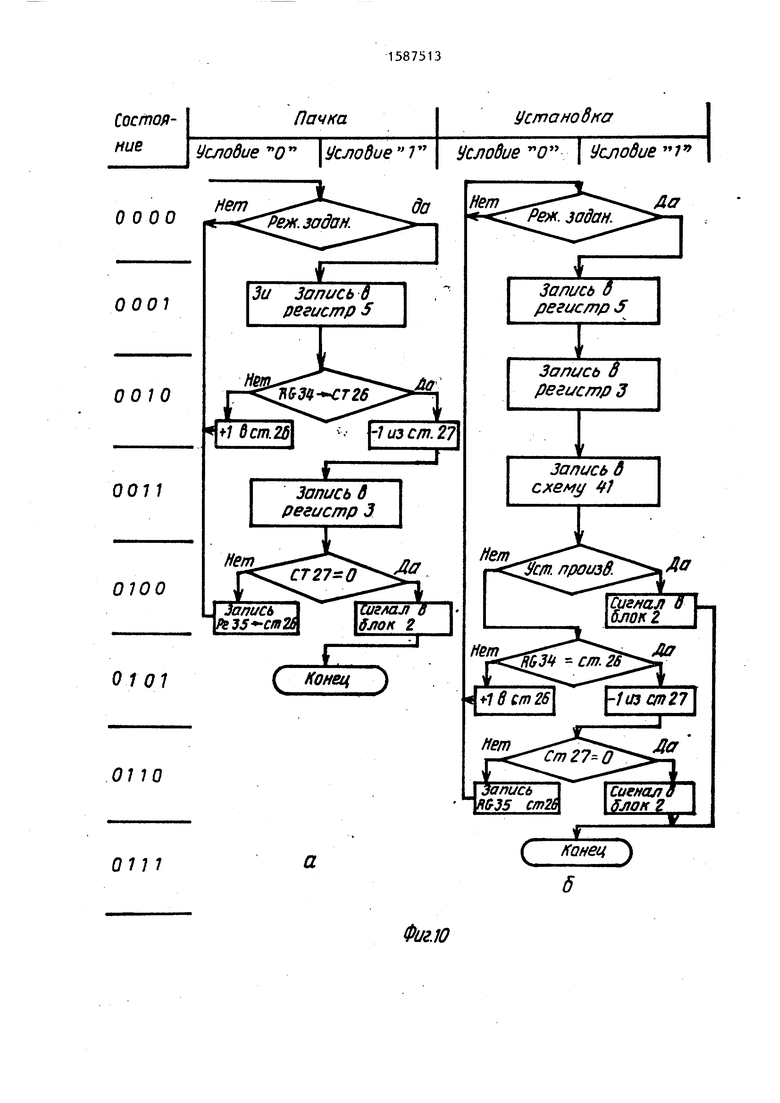

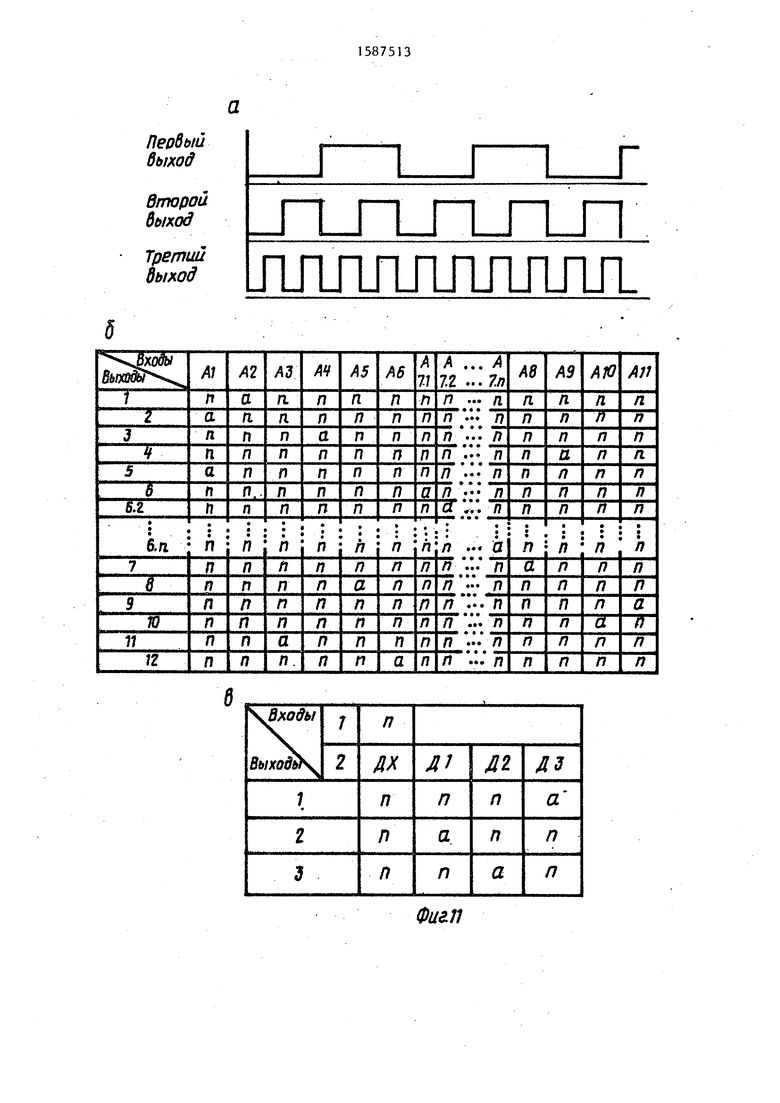

ки блока управления; на фиг. 8 - вариант выполнения микропрограммного узла управления, входящего в состав блока управления; на фиг. 9 - таблица размещения информации в блоке памяти и соответствукмцая ей временная диаграмма;,-на фиг. 10 - алгоритм работы блока управления; на фиг.11- временная диаграмма работы генератора импульсов, таблица преобразования первого депифратора блока управления и таблица преобразования второго дешифратора блока управления; на фиг. 12 - пример выполнения блока терминалов.

Устройство (фиг. 1) содержит блок 1 терминалов, блок 2 ввода-вывода, первый 3, второй 4 и третий 5 регистры и имеет 1 входов-выходов 6 (каналов) для подключения к контактам, просд

00

| сд

со

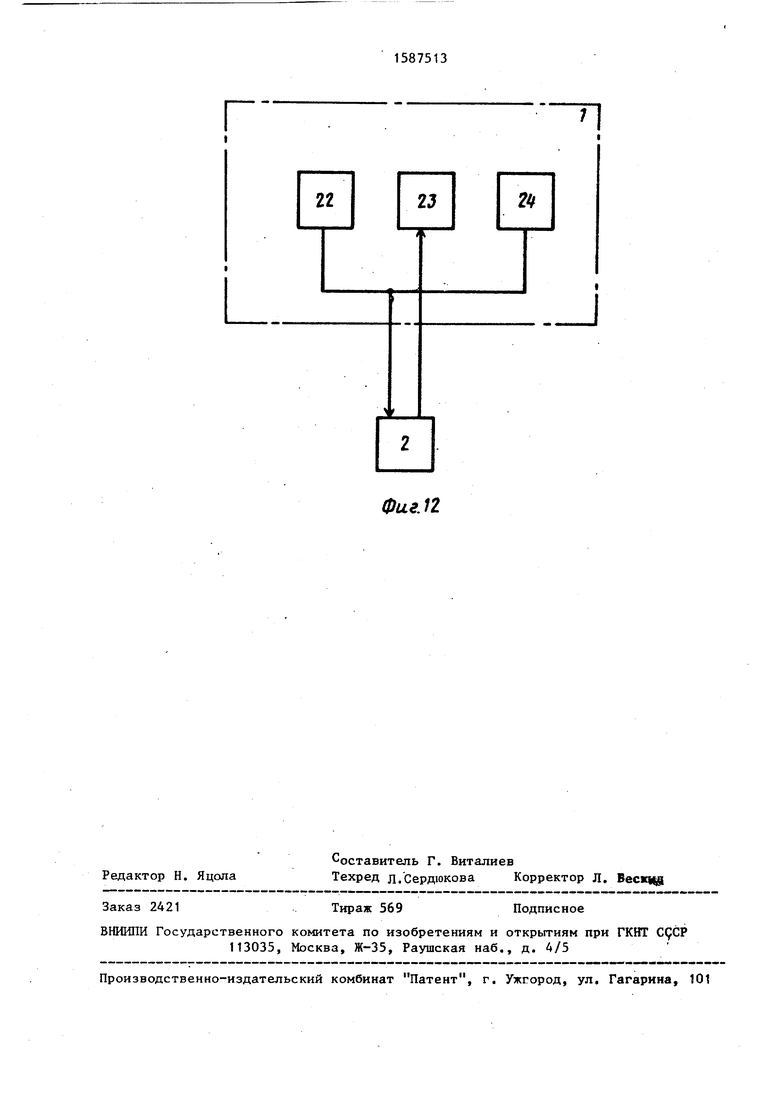

веряемого узла. Кроме того, устройство содержит 1 узлов 7 сравнения, 1 формирователей 8 импульсов блок 9 управления, сигнатурный анализатор 10, блок 11 памяти, четвертый и пятый регистры 12 и 13, 1 элементов И 14, блок 15 индикации сигнатур, первьй коммутатор 16, группу коммутаторов 17 элемент ИЛИ 18 и селектор 19. Устрой- ство имеет также выход 20 для подключения к синхровходу проверяемого узла и вход 21 для подключения к диагностируемой точке проверяемого узла. Блок 1 терминалов содержит алфавитно-циф- ровую клавиатуру 22, устройство 23 отображения и устройство 24 вводаБлок управления (фиг. 2) содержит первый и второй узлы 25.1 и 25.2 сравнения, первый счетчик 26, второй счет ,чик 27, коммутатор 28, первый и второй элементы ИЛИ 29 и 30, первый и второй дешифраторы 31 и 32, первый, второй и третий регистры 33-35, эле- |Мент И 36, первый и второй триггеры 37 и 38, элемент 39 задержки, генератор 40 импульсов, группу 41 триггеров установки, микропрограммный узел 42 управления, третий и четвертый триггеры 43 и 44, третий элемент ШТИ. :145 и регистр 46 сдвига.

Сигнатурный анализатор (фиг. 4). содержит регистр 47 сдвига и сумматор 48 по модулю два. Блок индикации сигнатур (фиг, 5) содержит регистр 49, .шифратор 50 и индикатор 51. .Элемент задержки (фиг. 6) содержит элемент И 52, счетчик 53 и триггер 54. .Группа триггеров установки (фиг, 7) содержит : пер вый: триггер 55 и второй триггер 56 Микропрограммный узел управления (фиг. 8) содержит регистр 57, постоянную память 58, регистр 59, дешифраг тор 60 и мультиплексор 61.

Устройство работает следующим об- разом,

В устройстве реализуются режимы контроля и диагностики. К режимам (Контроля относятся: режим одноразог- вой проверки с остановом на каждом ошибочном кадре; режим циклической проверки с остановом на первом ошибочном кадре. К режимам диагностики относятся; режимы одноразовой проверки с остановом на заданном номаде кадра с дальнейшим продвижением по шагам; режим щ клической проверки без реакции на ошибки. Режимы работы устройства задаются оператором.

, , Ю tS

25 зо

дз

CQ

Устройство работает в указанных режимах со следующими процедурами программы проверки: коммутация ; тест- набор ; маска ; измерение задержки.

35

40

55

,11.

пачка ; установка ; асинхронный ре- асинхронный режим с выборочным .контролем ; контроль z-состояния.

Режимы контроля предназначены для классификации контролируемого узла типа годен, не годен, режимы диагностики - для вьшвления причин не- испра.вности.

Процедура коммутация разделяет каналы устройства на входные и выходные в соответствии с каналами контролируемого узла. Процедура установка устанавливает схемы контролируемого узла (типа счетчик, регистр сдвига и т.д., не имеющие сброса) в исходное состояние. Процедура пачка предназначена для подачи на заданные входы контролируемого узла последовательность из заданного количества импульсов, что позволяет сократить объем блока 1 Г памяти. Процедура измерение задержки предназначена для измерения по заданным входам, контролируемого узла времени задержки ответного сигнала относительно момента воздействия. Процедура тест-набор предназначена дпя подачи воздействия на контролиру- емый узел и записи ответных сигналов. Процедура маска блокирует ответные сигналы от контролируемого узла на заданных каналах, Проце дуры асинхронный режим.предназначены для контроля асинхронных логических узлов. Процедура контроль z-состояния предназначена для контроля логических узлов, выводы которых могут принимать высокоинпедансное состояние. Программа проверки представляет собой комбинацию указанных процедур.

С клавиатуры 22 в блок 2 поступает команда, по которой с устройства 24 ввода информация через блок 2 загружается в блок 11 памяти. В качестве устройства 24 может применяться фотосчи- тьшающий..механизм, накопитель на магнитном диске или ленте, специализированные устройства ввода на ПЗУ и т.д. Загрузка блока 11 памяти происходит в два этапа. На первом этапе, считав очередную процедуру программы проверки из устройства 24, блок 2 устанавливает данные и адрес, поступающий на вход дешифратора 31, который, дешифрируя этот адрес, вырабатывает

стробы на втором и пятом выходах.Строб с второго выхода дешифратора 31 поступает на синхровход регистра 35. Происходит запись данных, поступаюпщх на вход регистра 35. Данные появляются на выходе регистра 35 и, так как в это время действует строб на запись данных в счетчик 26 с пятого выхода дешифратора 31, записьшаются в счетчик д 26 и, появляясь на его выходе, адресуют блок 11 памяти. На втором йтапе блок 2 устанавливает адрес и данные, поступающие и на вход блока 11 памяти. Дешифратор 31, расшифровывая адрес, вырабатывает на первом выходе строб, который устанавливает блок 2 памяти в режим записи (все остальное время блок 2 памяти находится в режиме чтения), и происходит запись данных в блок 11 памяти по ранее установленному адресу, хранящемуся в счетчике 26. Таким образом по кадрам загружается вся программа проверки. После загрузролируемого узла. Так происходит разделение каналов на входы и выходы. ; Процедура тест-набор вьтолняется по-разному э зависимости от режима и от предшествующих процедур. Если- процедура тест-набор предшествует процедуре установка, пачка, измерение задержки, асинхронный режим

или на зтой процедуре снимается дейст вие процедуры маска, то перед началом выполнения процедуры тест-набор необходимо обнулить регистр 13, либо записав в него всё нули, либо сбросив 15 его (цепи сброса не показаны).

Как правило, в программах проверки несколько тест-наборов следуют один за другим. В этом случае тест-наборы объединяются в пакет. Например, пакет имеет адрес первого тест-набора - п и адрес последнего тест-набора - т.

Блок 2 устанавливает адрес и данные. Адрес представляет собой двоичный код, которьй, расшифровываясь де-

20

ки программы проверки устройство пере- 25 шифратором 31, вьфабатывает строб на

ролируемого узла. Так происходит разделение каналов на входы и выходы. ; Процедура тест-набор вьтолняется по-разному э зависимости от режима и от предшествующих процедур. Если- процедура тест-набор предшествует процедуре установка, пачка, измерение задержки, асинхронный режим

или на зтой процедуре снимается действие процедуры маска, то перед началом выполнения процедуры тест-набор необходимо обнулить регистр 13, либо записав в него всё нули, либо сбросив его (цепи сброса не показаны).

Как правило, в программах проверки несколько тест-наборов следуют один за другим. В этом случае тест-наборы объединяются в пакет. Например, пакет имеет адрес первого тест-набора - п и адрес последнего тест-набора - т.

Блок 2 устанавливает адрес и данные. Адрес представляет собой двоичный код, которьй, расшифровываясь де-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

Изобретение относится к вычислительной технике и предназначено для тестового контроля и диагностики цифровых узлов, приборов, пультов и т.п. Целью изобретения является расширение области применения за счет обеспечения проверки цифровых узлов с независимой синхронизацией и произвольными начальными состояниями. С этой целью в устройство, содержащее три регистра, блок управления, сигнатурный анализатор, блок памяти, L узлов сравнения и L формирователей импульсов, введены четвертый и пятый регистры, L элементов И, блок индикации сигнатур, первый коммутатор, группа L коммутаторов, элемент ИЛИ и селектор. 1 з.п. ф-лы, 12 ил.

ходит к вьтолнению процедур тест-программы в соответствии с заданным оператором режимом.

Процедура коммутация выпсшняется одинаково для всех режимов и обязательно присутствует в начале программы проверки. Процедура вьтолняется следуняцим образом. Блок 2 устанавливаего третьем выходе и записьшает в р гистр 34 данные, которые представля собой двоичный код числа т, т.е. п ледний адрес пакета тест-наборов. Д 30 лее блок 2 устанавливает адрес и да ные. Адрес представляет собой двоич ный код, который, расшифровываясь д шифратором 31, вырабатывает стробы его втором и пятом выходах и через

ет адрес и данные, выполняя адресацию регистр 35 записывает в счетчик 26

блока 11 памяти через счетчик 26 аналогично первому этапу заггрузки блока 11. Затем блок 2 повторно устанавливает адрес и данные. Дешифратор 31, расшифровывая адрес, вырабатывает сТроб на одиннадцатом выходе, открывающий дешифратор 32. Данные, поступая на второй вход дешифратора 32, расшифровываются, на втором выходе дешифратора 32 появляется сигнал записи в регистр 4. Так как блок 11 памяти находится в режиме чтения, то на его выходах находится информация, соответству- юцая установленному адресу,которая -и записывается в регистр 4. Единица с какого-либо разряда регистра 4 постуг пает на вход формирователя 8 импульсов, переключая его .в высокоим- педансное состояние. Канал 6, сортвет- ствукяций данному разрезу, является входом устройства и выходом контролируемого узла. Если в разряд регистра.

данные, которые представляют собой двоичный код числа п, т.е. начальны адрес пакета тест-наборов., поступаю щий на адресные входы блока 2 памят

40 Если в программе проверки присутств ет не пакет тест-наборов, а только один тест-набор, то числа тип равны.

Рассмотрим.вьшолнекие пакета тйс

45 наборов применительно к режиму одно разовой проверки с остановом на каж дом ошибочном кадре. После загрузки регистра 34 и счетчика 26 блока 2 у танавливает адрес и данные для загр

50 ки микропрограммного узла 42 управл ния. Загрузка узла 42 заключается в записи режима в регистр задани режима. Дешифратор 31, расшифровьша адрес, установленный блоком 2, выра

55 тьшает строб на восьмом выходе и за писывает данные, поступающие на пер вый вход операции узла 42, которые

55 тьшает строб на восьмом выходе и записывает данные, поступающие на первый вход операции узла 42, которые

тест4 записан О, то данный канал 6 .явля- представляют собой код режима

ется выходом устройства и входом конт- с анализом ошибки. Узел 42 пе-)

его третьем выходе и записьшает в регистр 34 данные, которые представляют собой двоичный код числа т, т.е. последний адрес пакета тест-наборов. Да- 30 лее блок 2 устанавливает адрес и данные. Адрес представляет собой двоичг ный код, который, расшифровываясь дешифратором 31, вырабатывает стробы на его втором и пятом выходах и через

регистр 35 записывает в счетчик 26

регистр 35 записывает в счетчик 26

данные, которые представляют собой двоичный код числа п, т.е. начальный адрес пакета тест-наборов., поступающий на адресные входы блока 2 памяти.

40 Если в программе проверки присутствует не пакет тест-наборов, а только один тест-набор, то числа тип равны.

Рассмотрим.вьшолнекие пакета тйст45 наборов применительно к режиму одноразовой проверки с остановом на каждом ошибочном кадре. После загрузки регистра 34 и счетчика 26 блока 2 устанавливает адрес и данные для загруз50 ки микропрограммного узла 42 управления. Загрузка узла 42 заключается в записи режима в регистр задания режима. Дешифратор 31, расшифровьшая адрес, установленный блоком 2, выраба55 тьшает строб на восьмом выходе и записывает данные, поступающие на первый вход операции узла 42, которые

тест представляют собой код режима

с анализом ошибки. Узел 42 пе-)

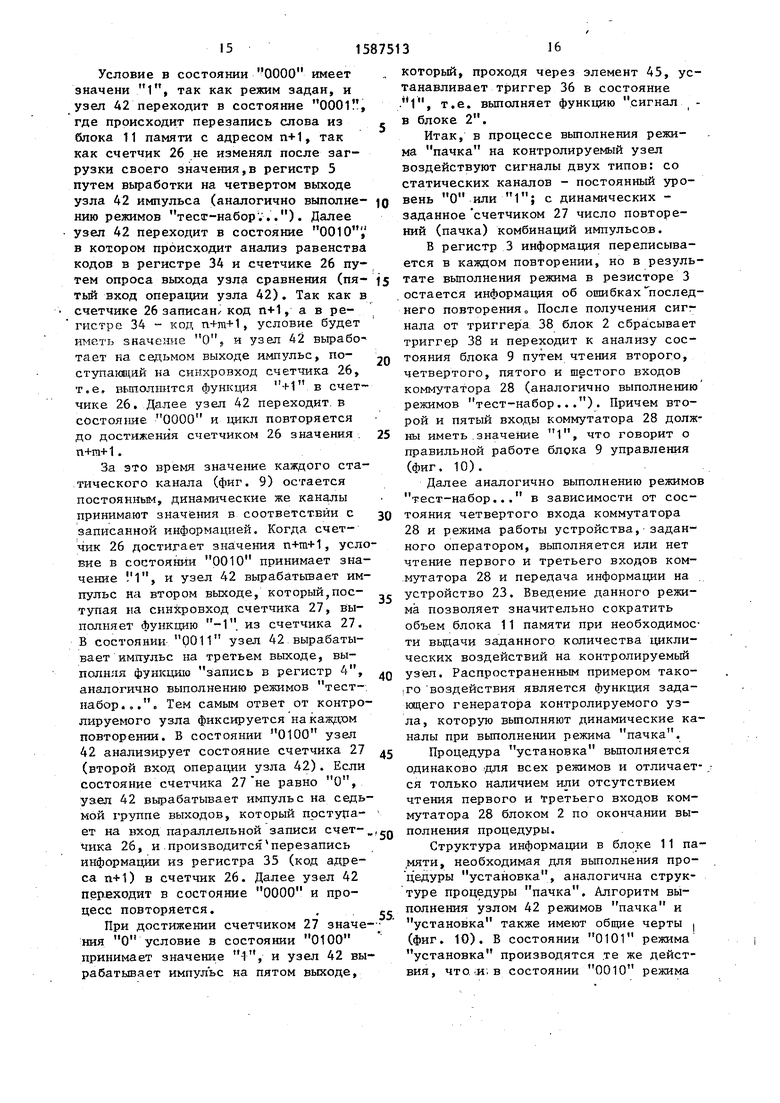

реходит к выполнению заданного режима, алгоритм которого представлен на фиг. 3.

После задания режима (состояние с 0000) узел 42 вьфабатывает импульс на четвертом выходе, которьй через элемент 30 поступает на вход регистра 5, производя запись в него слова (состояние 0001) из блока 11 памяти, имею- JQ |шка 26 код п+1, который адресует следующее слово блока 11 памяти. Далее : узел 42 переходит в состояние 0000, и цикл повторяется. Как видно из фиг. 3, выход из цикла возможен либо при наличии ошибки (в состоянии условие имеет значение 1), при достижении счетчиком 26 значения кода, записанного в регистре 34, когда на выходе узла. ..24 сравнения появится сигнал Лог . 1, анализируемый в состоянии 0100. И в том и в другом случае блок 9 вьвдает сигнал в блок 2 путем выработки импульса на пятом выходе, который проходит через элемент

(щего адрес п. С выхода регистра 5 ин- ,формация поступает на входы формирователей 8 импульсов и на вторые входы узлов 7 сравнения. Если канал 6 за- коммутирован как выход устройства, то 15 информация с входа формирователя 8 поступает на его вьпсод и далее на выход устройства и представляет собой воздействие на контролируемой узел.

ЕСЛИ канал 6 закоммутирован как 20 вход устройства, то информация с входа формирователя 8 не проходит на его выход, а поступает только на второй вход узла 7 сравнения и представляет

собой эталонную информацию, с которой 25 45, взводит триггер 38. Блок 2 при пона узле 7 сравнения сравнивается ответ, , получаемый от контролируемого узла на данное воздействие. С выходов узлов 7 сравнения информация об ошибке (при Несовпадении информации на первом и втором входах узла 7 сравнения на его выходе формируется 1), если таковые имеются, поступает на входы регистра 3. Далее узел 42 переходит в cqcтoяниe 00.10, в котором пр.оисходит запись 35 информации об ошибках в регистр 3 путем вьщачи импульса с третьего выхода узла 42, поступающего через элемент ... 29 и пятый выход блока 9 на вход записи регистра 3. Так как перед началом 40 выполнения процедуры регистр 13 бьт обнулен, то на выходы коммутаторов 17 проходит информация с их третьих входов, т.е. -информация о наличии ошибок, записанная в регистр 3.Далее информа- 45 дня с входов коммутатора 16 (так как триггер 37 сброшен) поступает на его выход и далее на вход элемента 18, на

30

тест-набор с анализом ошибки необходимо анализировать на первом этапе чтения сигналы с входов четыре и пят коммутатора 28. Возможны три ситуаци Первая ситуация. С четвертого вхо

котором сворачивается, и через вход

блока 9 поступает на третий вход one- 50 коммутатора 28 (сигнал о наличии

рации узла 42 в виде сигнала условия ошибки) в блок 2 поступает Лог. О,

которое и анализируется узлом 42 в

состоянии 0011.

Предположим, что ошибка отсутствует (условие имеет значение 0. В этом случае узел 42 переходит в сое- , тояние 0100, в котором происходит анализ следующего условия, поступающе- го на пятый вход операции узла 42 с.

а с пятого входа (с узла 24 сравнег.. ния) - Лог. 1. Эта ситуация говори о том, что блок 9 закончил выполнени данного пакета тест-наборов, ошибок в контролируемом узле не обнаружено и блок 2 может переходить к загрузке исходных данных в блок 9 для выполне ния следующей процедуры. Второй и тр

с ле, я15875138

выхода узла 27 сравнения, которое принимает значение 1 при равенстве кодов, записаннь,1х в счетчике 26 и ре- | гистре 34. Предположим, что условие

имеет значение О. Тогда на -седьмом выходе узла 42 появляется сигнал, поступающий на тактовый вход счетчика 26, который устанавливает на выходе счет50 5

ступлении на его вход сигнала с выхода триггера 38 начинает чтение информации с выхода коммутатора 28. Блок 2 устанавливает адрес, который, расшиф- 0 ровываясь дешифратором 31 , вьграбатыва- ет на его двенадцатом выходе сигнал сброса триггера 38. Далее блок 2 устанавливает адрес, который, расшифро- вываясь дешифратором 31, вырабатывает на его шестом выходе сигнал чтения, подключающий к выходу коммутатора 28 соответствующую группу входов, информация с которой записьшается в блок 2. Чтеьше информации может происходить в несколько этапов. На первом этапе происходит анализ состояния блока 9 путем подключения к выходу коммутатора 28 его второго, четвертого, пятого и шестого входов. В режиме

тест-набор с анализом ошибки необходимо анализировать на первом этапе чтения сигналы с входов четыре и пять коммутатора 28. Возможны три ситуации. Первая ситуация. С четвертого вхоошибки) в блок 2 поступает Лог. О,

а с пятого входа (с узла 24 сравнег.. ния) - Лог. 1. Эта ситуация говорит о том, что блок 9 закончил выполнение данного пакета тест-наборов, ошибок в контролируемом узле не обнаружено и блок 2 может переходить к загрузке исходных данных в блок 9 для выполнения следующей процедуры. Второй и третий этапы чтения информации с коммутатора 28 не производятся.

Вторая ситуация.С четвертого и пятого входов коммутатора 28 в блок - 2 поступают сигналы Лог. 1. Это говорит о том, что ошибка обнаружена в последнем кадре пакета тест-наборов . При этом блок 2 переходит ко второму этапу чтения путем подключения третьего входа коммутатора 28 к его выходу.Информация на выходе коммутатора 28 представляет собой код числа щ, записанного в счетчике 26, и гово

рит о номере кадра, на котором про- изопша ошибка. Эта информация поступает на вход блока 2 и далее в блок 1 терминалов на устройство 23. Затем блок 2 производит третий этап чтения путем подключения первого входа коммутатора 28 к его выходу.На первом входе находится информация об ошибках которые поступают с выходов коммутаторов. 17. Считанная за третий руап блоком 2 информация передается в блок 1 терминалов на устройство 23. В итоге оператор имеет на экране устройства отображения информацию о номере адра и номерах каналов, на которых рроизошла ошибка. Устройство готово к вьтолнению следующей процедуры, но (Цожидается команды оператора с алфа-. витно-цифровой клавитауры 22.

Третья ситуация. С четвертого входа коммутатора 28 в блок 2 поступает |Сигнал Лог. 1, с пятого входа - . О. Это говорит о том,что блок 9 обнаружил ошибку в кадре номер k (п k m), который не является последним кадром пакета тест-наборов. Блок 2 производит второй и третий этапы чтения аналогично второй ситуации, вьщавая на устройство 23 информацию о номере кадра и номерах каналов ,на которьк обнаружены ошибки,и переходит в состояние ожидания. По команде оператора о продолжении выполнения режима блок 2 загружает в счетчик 26 код числа k+1 ив. узел 42 код режима тест-набор с анализом ошибки. Загрузка происхоит аналогично первоначальной загрузке параметров режима. Тем самым образуется новый пакет тест-наборов с границами от k+1 до т который выполняется по уже известному

алгоритму. Пакет тест-наборов в режиме циклическая проверка с остановом на первом ошибочном кадре вьшолняется так же, как и в режиме одноразовая

JQ

15

20

30

- 25

35

40

0

5

проверка с остановом на каждом ошибрч- ном кадре, с той лишь разницей, что при попадании начального адреса зацикливаемого участка в пределы пакета тест-наборов начальный адрес пакета тест-наборов будет равен начальному адресу зацикливаемого участка, а при попадании конечного адреса заклиниваемого участка в пределы пакета тест-наборов будет равен конечному адресу зацикливаемого участка.

Выполнение пакета тест-наборов в режиме одноразовая проверка с остановом на заданном номере кадра с дальнейшим продвижением по шагам ртлича- ется от вьшолнения его в режиме одноразовая проверка с остановом на каждом ошибочном кадре по двум пунктам.

Первый пункт заключается в том, что в узел 42 загружается не код режима тест-набор с анализом ошибки, :а код режима тест-набор без анализа ошибки. Алгоритм вьшолнения дан- ного режима (фиг. 3) отличается выполнением состояния 0011. В этом состоянии отсутствует анализ ошибки и выход из цикла возможен только по совпадению кодов регистра 34 и счетчика 26 (состояние 0100).

Второй пункт заключается в том, что при попадании кадра останова, заданного оператором с клавиатуры 22, в пределы пакета тест-наборов адрес пакета тест-наборов будет равен адресу кадра останова, допустим k. Далее блок 2 загружает и в счетчик 26 и в регистр 34 код числа k+1, затем, после выполнения режима k+2 и т.д. до достижения последнего адреса пакета тест-наборов о Вьтолнение пакета тест- наборов в режиме циклическая проверка без реакции на ошибки отличается от выполнения пакета тест-набора в режиме циклическая проверка с остановом на первом ошибочном кадре тем,

узел 42 загружается не код режи- тест-набор с анализом ошибки,, а код режима тест-набор без анализа ошибки.

Процедура маска выполняется одинаково для всех режимов и является подготовительной операцией для процедуры тест-набор „ Процедура маска выполняется следукщим образом. Блок 2 адресует соответствующее слово блока 11 памяти, загружая код адреса в счетчик 26 (процесс загрузки описан). Затем блок 2 повторно устанавливает

что в ма

адрес и данные .Дешифратор 31, расшиф- ровьгаая адрес, вырабатьшает строб на своем одиннадцатом выходе, стробируя в свою очередь дешифратор 32 (по , первому входу). Дешифратор 32, расшифровывая данные, поступаняцие на его вход, вьфабатьтает строб на третьем выходе, который, поступая на вход

блок 2 адресует второе слово процедуры.

Далее блок 2 производит загрузку элемента 39 задержки, устанавливая на второй группе выходов адрес и данные, которые представляют собой двоичный код длительности задержки и .поступают на второй вход элемента 39 задержки.

регистра 13, записывает в него инфор- Q Адрес расшифровывается дешифратором

мацию с выхода блока 11 памяти. Информация с выхода регистра 13 поступает на управляющие входы коммутаторов 17. Если в соответствующем разряде регистра 13 записана 1, то на 15 вь1ход коммутатора 17 будет проходить информация с входа, соединенного с выходом регистра 12, если О г- то на выход коммутатора 17 будет проходить информация с входа, соединенного с вы-20 ходом регистра 3.

При выполнении процедуры тест-набор после процедуры маска сигналы об ошибках не появляются на выходах коммутаторов ,17 на замаскированных ка .налах, так как в регистр 12,который 1редварительно сбрасывается (цепи

31, на седьмом выходе которого появляется сигнал, поступаюций на третий вход элемента 39 задержки и стробиру- ющий запись данных в счетчик (фиг. 6) элемента задержки. Далее блок 2 загружает в узел 42 код режима контроль с измерением з.адержки. Загрузка узла 42 происходит аналогично процедуре тест-набор.

После загрузки узел 42 переходит к вьшолнению режима контроль с измерением задержки (фиг. 3). Так как ре- жим задан, условие в состоянии 0000 имеет значение 1, и узел 42 перехо- -25 дит в состояние 0001, где производится запись адресованного ранее слова в регистр 5 (аналогично выполнению режимов тест-набор...) и запуск элемента 39 задержки путем выработки

сброса не показаны), в режиме тест- набор информация не записывается, и на выходе заблокированного коммутато- 30 уровня Лог. 1 на первом выходе узра 17 независимо от информации на его входе Присутствует О, т.е. фиксируется отсутствие ошибки. Следовательно, каналы, которые на каком-то количестла 42, который, поступая на цервыи вход элемента 39 задержки, открывает элемент 52 (фиг. 6), разрешая поступление импульсов от генератора 40 тесве тест- наборов невозможно однозначно 35 тов на тактовый вычитаюищй вход счетчика 53, и отпускает по входу R триггер 54.

определить, маскируются и не участву- ют в проверке контролируемого узла, Процедура измерение задержки выпол- няется одинаково для всех режимов и отличается только наличием или отсутст- вием чтения первого и третьего входов коммутатора 28 блоком 2 по окончании вьшолнения процедуры.

Информация, необходимая для выполнения процедуры, защищает два адреса блока 11 памяти. Полпервому адресу процедуры размещается информация, указывающая, на каких каналах будет производиться измерение задержки. Эти каналы обозначены 1.

Действия над первым словом процедуры измерение задержки аналогичны

т.е..инвыполнению процедуры маска, формация из блока 11 памяти заносится в регистр 5, производя тем самым уп- равление коммутаторами 17. Если канал обозначен единицей, то к выходу коммутатора 17 подключается его вход, соединенный с регистром 12. Затем

блок 2 адресует второе слово процедуры.

Далее блок 2 производит загрузку элемента 39 задержки, устанавливая на второй группе выходов адрес и данные, которые представляют собой двоичный код длительности задержки и .поступают на второй вход элемента 39 задержки.

Q Адрес расшифровывается дешифратором

5 20

31, на седьмом выходе которого появляется сигнал, поступаюций на третий вход элемента 39 задержки и стробиру- ющий запись данных в счетчик (фиг. 6) элемента задержки. Далее блок 2 загружает в узел 42 код режима контроль с измерением з.адержки. Загрузка узла 42 происходит аналогично процедуре тест-набор.

После загрузки узел 42 переходит к вьшолнению режима контроль с измерением задержки (фиг. 3). Так как ре- жим задан, условие в состоянии 0000 имеет значение 1, и узел 42 перехо- 25 дит в состояние 0001, где производится запись адресованного ранее слова в регистр 5 (аналогично выполнению режимов тест-набор...) и запуск элемента 39 задержки путем выработки

30 уровня Лог. 1 на первом выходе узла 42, который, поступая на цервыи вход элемента 39 задержки, открывает элемент 52 (фиг. 6), разрешая поступление импульсов от генератора 40 тестов на тактовый вычитаюищй вход счетчика 53, и отпускает по входу R триггер 54.

В состоянии 0010 происходит запись ответа от контролируемого узла в регистр 3 аналогично выполнению режимов тест-набор..о по всем каналам.

В состоянии 0011 происходит анализ состояния узла 39 задержки. Счетчик 53 элемента 39 задержки обнуляетс .через время, соответствукщее коду задержки, и на его выходе заема появляется сигнал, который, установит триггер 54 в состояние 1. На выходе триггера 54 появляется перепад из О в 1, который через четвертый выход блока 9 поступает на вход регистра 12 и записывает в него ответ от контролируемого узла. Уровень Лог о 1 с выхода этого же триггера 54 элемента 39 задержки поступает на шестой вход операции (вход условия) узла 42, который по этому условию выдает сигнал в блок 2 (аналогично выполнению режимов тест-набор...) и

заканчивает вьтолнение режима. Т.е. в данном режиме запись ответа от контролируемого узла происходит два раза: первый, раз - в регистр 3 (аналогично вьтолнению режимов тест-набор....) через определяемое быстродействием устройства время; второй раз - в регистр 12 через промежуток времени, сформированный узлом 39 задержки, Кро ме того, происходит приостанов (состояние 0011) узла 42, если время задержки превосходит время продвижения узла 42 до состояния 0011, что необходимо для синхронизации работы узла 42 и блока 2.

Информация с выхода регистра 3 поступает на входы коммутаторов 17, а информация с выходов регистра 12 - на другие входы коммутаторов 17. Если в каком-либо разряде регистра 13 записана 1, то на выход коммутатора 17 поступает информация с вькода регистра 12, если О - то с выхода регистра 3. Информация с выходов коммутато- ров 17 поступает на входы коммутатора 28 блока 9 и представляет собой на части каналов ответ от контролируемого узла, записанный через нормальное время, а на другой части каналов - от вет, записанный через заданное время.

По окончании выполнения режима узлом 42 блок 2 переходит к чтению информации с первого и третьего входов коммутатора 28, устанавливая соответ- ствующий адрес на выходах, аналогично выполнению режимов тест-набор,,..

Если процедура измерение задержки вьшолняется в режимах контроля, то информация об ошибках выдается на устройство 23, Если процедура измерение задержки выполняется в режиме одноразовая проверка с остановом на заданном номере кадра,,. и информация , считанная блоком 2 с выхо- да счетчика 26, соответствует данному оператором кадру останова, то информация об ошибках и номере кадра выдается на устройство 23. В остальных режимах после окончания выполнения процедуры измерение задержки устройство переходит к выполнению следующей процедуры.

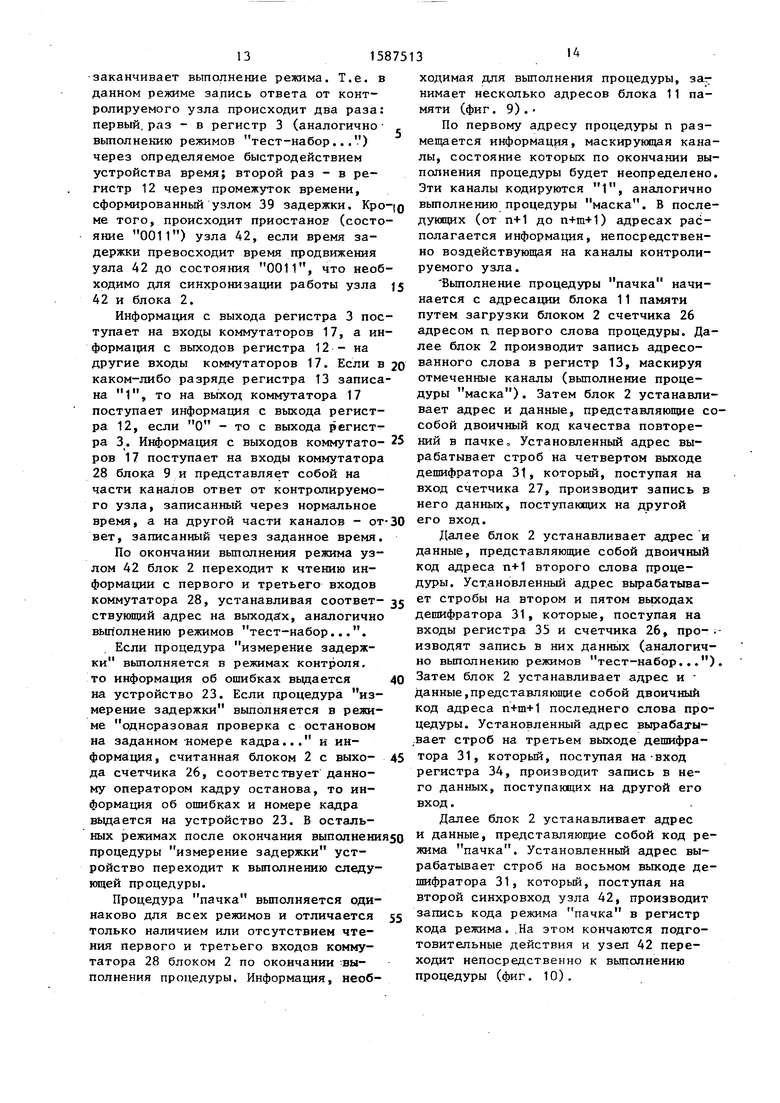

Процедура пачка вьшолняется одинаково для всех режимов и отличается только наличием или отсутствием чтения первого и третьего входов коммутатора 28 блоком 2 по окончании -выполнения процедуры. Информация, необходимая для выполнения процедуры, занимает несколько адресов блока 11 памяти (фиг. 9).

По первому адресу процедуры п размещается информация, маскирующая каналы, состояние которых по окончании выполнения процедуры будет неопределено Эти каналы кодируются 1, аналогично вьтолнению процедуры маска, В после дукщих (от п+1 до n+m+1) адресах располагается информация, непосредственно воздействующая на каналы контролируемого узла.

Вьтолнение процедуры пачка начинается с адресации блока 11 памяти путем загрузки блоком 2 счетчика 26 адресом п первого слова процедуры. Далее блок 2 производит запись адресованного слова в регистр 13, маскируя отмеченные каналы (вьтолнение процедуры маска), Затем блок 2 устанавливает адрес и данные, представляющие со собой двоичный код качества повторений в пачке. Установленный адрес вырабатывает строб на четвертом выходе дешифратора 31, который, поступая на вход счетчика 27, производит запись в него данных, поступающих на другой его вход.

Далее блок 2 устанавливает адрес и данные, представляющие собой двоичный код адреса п+1 второго слова процедуры. Установленный адрес вьфабатыва- ет стробы на втором и пятом выходах дешифратора 31, которые, поступая на входы регистра 35 и счетчика 26, про- изводят запись в них данньпс (аналогично выполнению режимов тест-набор,,,) Затем блок 2 устанавливает адрес и данные,представляющие собой двоичный код адреса п+т+1 последнего слова процедуры. Установленный адрес вырабауы- .вает строб на третьем выходе дешифратора 31, который, поступая на-вход регистра 34, производит запись в него данных, поступающих на другой его вход.

Далее блок 2 устанавливает адрес и данные, представляющие собой код режима пачка. Установленный адрес вы- рабатьшает строб на восьмом выходе дешифратора 31, который, поступая на второй синхровход узла 42, производит запись кода режима пачка в регистр кода режима..На этом кончаются подготовительные действия и узел 42 переходит непосредственно к выполнению процедуры (фиг. 10).

Условие в состоянии 0000 имеет знамени 1, так как режим задан, и узел А2 переходит в состояние 0001, где происходит перезапись слова из блока 11 памяти с адресом п+1, так как счетчик 26 не изменял после загрузки своего значения,в регистр 5 путем вьфаботки на четвертом выходе узла 42 импульса (аналогично выполне- нию режимов тест-набор ...). Далее узел 42 переходит в состояние , в котором происходит анализ равенства кодов в регистре 34 и счетчике 26 путем опроса выхода узла сравнения (пя- тьй вход операции узла 42). Так как в счетчике 26 записан/ код п+1, а в регистре 34 код п+га+1, условие будет иметь значение О, и узел 42 вырабо- тает на седьмом выходе импульс, по- ступакщий на сиихровход счетчика 26, т.е. ВЫПОЛ1ШТСЯ функция +1 в счетчике 26. Далее узел 42 переходит, в состояние 0000 и цикл повторяется до достижения счетчиком 26 значения . п+та+1.

За это время значение каждого статического канала (фиг. 9) остается постоянным, динамические же каналы принимают значения в соответствии с записанной информацией. Когда счетчик 26 достигает зна:чения n+m+1, условие в состоянии 0010 принимает значение 1, и узел 42 вырабатьтает импульс на втором выходе, который,пос- тупая на синхровход счетчика 27, выполняет функцию -Г . из счетчика 27. В состоянии 0011 узел 42 вырабатывает импульс на третьем выходе, выполняя функцию запись в регистр 4, аналогично выполнению режимов тестнабор . ,,

Тем самым ответ от контролируемого узла фиксируется на каждом повторении. В состоянии 0100 узел 42 анализирует состояние счетчика 27 (второй вход операции узла 42). Если состояние счетчика 27 не равно О, узел 42 вырабатывает импульс на седьмой выходов, который поступает на вход параллельной записи счет-. чика 26, и производится перезапись информации из регистра 35 (код адреса п-ь1) в счетчик 26. Далее узел 42 пер.входит в состояние 0000 и процесс повторяется..

При достижении счетчиком 27 значения О условие в состоянии 0100 принимает значение 4, и узел 42 вырабатывает импульс на пятом выходе.

которьй, проходя через элемент 45, устанавливает триггер 36 в состояние ., т.е. выполняет функцию сигнал в блоке 2.

Итак, в процессе вьшолнения режима пачка на контролируемый узел воздействуют сигналы двух типов: со статических каналов - постоянный уровень О или с динамических - заданное счетчиком 27 число повторений (пачка) комбинаций импульсов.

В регистр 3 информация переписывается в каждом повторении, но в результате вьшолнения режима в резисторе 3 остается информация об ошибках последнего повторения После получения сигг нала от триггера 38 блок 2 сбра сывает триггер 38 и переходит к анализу состояния блока 9 путем чтения второго, четвертого, пятого и шестого входов коммутатора 28 (аналогично выполнению режимов тест-набор...). Причем второй и пятый входы коммутатора 28 должны иметь .значение 1, что говорит о правильной работе блока 9 управления (фиг. 10).

Далее аналогично выполнению режимо тест-набор... в зависимости от состояния четвертого входа коммутатора 28 и режима работы устройства, заданного оператором, выполняется или нет чтение первого и третьего входов коммутатора 28 и передача информации на устройство 23. Введение данного режима позволяет значительно сократить объем блока 11 памяти при необходимости вьдачи заданного количества циклических воздействий на контролируемый узел. Распространенным примером тако- |ГО воздействия является функция задающего генератора контролируемого узла, которую вьтолняют динамические каналы при выполнении режима пачка.

Процедура установка выполняется одинаково ДЛЯ всех режимов и отличает ся только наличием или отсутствием чтения первого и третьего входов коммутатора 28 блоком 2 по окончании выполнения процедуры.

Структура информации в блоке 11 па ,мяти, необходимая для выполнения процедуры установка, аналогична структуре процедуры пачка. Алгоритм выполнения узлом 42 режимов пачка и установка также имеют общие черты | (фиг. 10). В состоянии 0101 режима установка производятся те же действия, что. .;и. в состоянии 0010 режима

пачка

17Т5.

т.е. организация цикла вьща- чи и приема информации от адреса п+1 до адреса n+m+l (фиг. 9). В состояний 0110 режима установка выполняют-. ся те же действия, что и в состоянии 0100 режима пачка, т.е. организация цикла второго порядка, который заключается в циклической вьщаче какого-то количества блоков (от п+1 до п+т+1) информации.

Загрузка блока 9 блоком 2 при вы

полнении процедуры установка анало

гична

дуры пачка

загрузке при вьтапнении процес той лишь разницей.,

||„„„„ 11

что при выполнении процедуры пачка в счетчик 27, определяющий количество повторений, загружается код, нормирующий число повторений, а при выполнении процедуры установка в счетчик 27 загружается код максимально возможного числа повторений, т.е. на контролируемый узел вьщается нормированное число повторений...

Итак, после загрузки кода режима установка узел 42 проходит состояния 0000, 0001, 0010, вьшолняя вьщачу на контролируемый узел информации (состояние 0001) и прием от него ответа (состояние 0010). Далее ЗО узел 42 переходит в состояние 0011, в котором происходит запись в группу 41 триггеров установки путем вьфабот- ки на шестом выходе узла 42 импульса,

который поступает на С-вход D-тригге- j шихся каналов и адрес слова блока 11 ра 55 группы 41 (фиг. 7). На D-вход памяти.

|ЗтЬго же триггера 55 поступает инфор- Процедура асинхронный режим .с вы- мация с выхода элемента 18, который борочным контролем выполняется слеЕсли контролируемый узел не устанавливается в требуемое состояние, например, вследствие неисправности, выход из режима произойдет из состояния 0110. В этом случае шестой вход коммутатора 28 будет иметь значение О, а второй, третий и четвертый - значение 1, и устройство в зависимости от режима, заданного оператором либо перейдет к выполнению следующей процедуры, либо к вьщаче на устройств 23 результатов вьшопнения режима, сообщая оператору номера неустановивобъединяет информацию об ошибках с незамаскированных каналов контролируе- до мого узла, поступающую с регистра 3 через коммутаторы 17 и коммутатор 16.

Узел 41 установки (фиг. 7).устроен таким образом, что на его выходе появляется уровень логической 1 (триггеры предварительно сброшены) только по исчезновении ошибки, т.е. при перепаде значения ошибки из 1 в О.

В состоянии 0100 производится анализ состояния узла 41 (четвертый вход операции узла 42). Если условие имеет значение О, узел 42 переходит в состояние 0101, если 1 - выдается сигнал в блок 2 и заканчивается выполнение режима. Итак, при выполнении режима установка на .заданные каналы вьщаются последователь- . ности импульсов и происходит анализ

дующим образом. Блок 2 адресует блок 22 памяти путем загрузки кода адреса первого слова процедуры в счетчик 26. Далее блок 2 записывает информацию первого слова процедуры в регистр 3, устанавливая на второй группе выходов 45 адрес, которьй, расшифровываясь дешифратором 31, вырабатывает строб на его одиннадцатом выходе, и данные, которые, расшифровываясь дешифратором 32, вьфабатьшают на его третьем выходе им- пулБС записи в регистр 13. Первое слово процедуры обозначает каналы (единица в соответствукяцем разряде регистра 13), по которым определяется готовность контролируемого узла к вцдаче ответа на воздействие. Воздействие и эталонные ответы образуют второе слово процедуры. Затем блок 2 адресует блок 11 памяти путем загрузки кода адреса второго слова процедуры в счет50

55

18

0

ошибок на заданных (незамаскированных) каналах на каждом адресе (от п+1 до n+m+O каждого повторения. Выход из режима может произойти из состояния 0100 и из состояния 0110 (фиг. 10). После получения блоком 2 сигнала от блока 9 (выход из режима) блок 2 вьшолняет сброс триггера 38 и переходит к чтению состояния блока 9 (второй, четвертый, пятый и шестой Bk- ходы коммутатора 28) аналогично выпол5

n

5

О

j шихся каналов и адрес слова блока 11 памяти.

нению процедуры пачка.

Если контролируемый узел установился в требуемое состояние, выход из режима происходит из состояния 0100. В этом случае шестой вход коммутатора 28 будет иметь значение 1, а второй и четвертый входы - значение О, и устройство переходит к выполнению следующей процедуры.

Если контролируемый узел не устанавливается в требуемое состояние, например, вследствие неисправности, выход из режима произойдет из состояния 0110. В этом случае шестой вход коммутатора 28 будет иметь значение О, а второй, третий и четвертый - значение 1, и устройство в зависимости от режима, заданного оператором, либо перейдет к выполнению следующей процедуры, либо к вьщаче на устройстве 23 результатов вьшопнения режима, сообщая оператору номера неустановиво

дующим образом. Блок 2 адресует блок 22 памяти путем загрузки кода адреса первого слова процедуры в счетчик 26. Далее блок 2 записывает информацию первого слова процедуры в регистр 3, устанавливая на второй группе выходов 5 адрес, которьй, расшифровываясь дешифратором 31, вырабатывает строб на его одиннадцатом выходе, и данные, которые, расшифровываясь дешифратором 32, вьфабатьшают на его третьем выходе им- пулБС записи в регистр 13. Первое слово процедуры обозначает каналы (единица в соответствукяцем разряде регистра 13), по которым определяется готовность контролируемого узла к вцдаче ответа на воздействие. Воздействие и эталонные ответы образуют второе слово процедуры. Затем блок 2 адресует блок 11 памяти путем загрузки кода адреса второго слова процедуры в счет0

5

чик 26. Далее блок 2 вьфабатьшает на втором выходе адрес, который, расшиф ровываясь дешифратором 31, вырабатывает строб на его одиннадцатом выходе и данные, которые, расшифровываясь Дешифратором 32, вырабатывают импульс на его первом выходе. Импульс с перво го выхода дешифратора 32 поступает через элемент 30 на вход регистра 5, производя в него запись второго слова процедуры, т.е. вьщавая воздействие на контролируемьй узел и определяя эталонный ответ. ,

Этот же импульс поступает на вход триггера 37, устанавливая его в состояние 1. Лог.1 с выхода триггера 37 поступает на первый вход элемента 36, на второй вход которого поступает строб дешифратора 32. Наличие 1 на первом входе и О на втором подготавливает элемент 36 к реакции на сигнал йшибки. Лог, 1 с выхода триггера 37 поступает на управля сщий вход коммутатора 16, разрешая прохождение на выход сигналов с его информационного входа.

Таким образом, устройство находится в состоянии ожидания кодовой комбинации, заданной втррым словом проце- дуры, на выходных каналах контролируемого узла, заданных первым словом процедуры. Запуск устройства происходит по исчезновении ошибки. В формировании ошибки участвуют только каналы, отмеченные единицей в соответствукщем разряде регистра 13, так как уровень ЛОР. 1 открывает соответствующий элемент 14. Если информация на одном или нескольких заданных выходах конт- ролируемого узла не соответствует эталонному ответу, сигнал ошибки уровнем Лог. 1 поступает через элемент 14, коммутатор Т6, элемент 18 на инверсный вход элемента 36. Если информация на заданных выходах контролируемого узла приняла значеьше,. соответствующее эталонному, на вьтходах всех элементов 14 появляется уровень Лог. О, который через коммутатор 16 и элемент 18 поступает на инверсный вход . элемента 36, устанавливая на его выходе значение 1. Эта ситуация говорит о готовности контролируемого узла, т.е. о том, что можно считывать информа- цию с остальных выходов. Уровень Лог, 1 с выхода триггера 43 поступает через элемент 29 на вход регистра 3, производя запись информации об

ошибках со всех каналов контролируемого узла, В то же время уровень Лог. 1 с выхода элемента 36 поступает через Tt)Hrrep 34 на первый вход триггера 38, устанавливая его в состояние 1, что является сигналом в блок 2с Получив сигнал, блок 2 сбрасывает триггеры 37 и 38, чем обеспечивает подключение к выходам коммутатора 16 сигналов со второй группы его входов и снятие сигнала с выхода триггера 38 Затем блок 2 адресует блок 11 памяти путем загрузки кода адреса третьего слова процедуры в счетчик 26. Далее блок 2, вырабатывая соответствующий адрес и данные, записывает информацию третьего слова процедуры в регист 13. Информация третьего слова процедуры определяет, с какух каналов контролируемого узла (отмечены О в соответствующем разряде) будет производиться чтение ответа. Регистр 13 производит управление коммутаторами 17 аналогично вьшолнению процедуры маска. Затем блок 2 переходит к анализу состояния блока 9 путем чтения четвертого входа коммутатора 28. При наличии ошибки ( четвертом входе) блок 2 в зависимости от режима либо переходит к чтению третьего и первого входов коммутатора 28 и вьщачи сообщения на устройство 23, либо к выполнению следующей процедуры. При отсутствии ошибки устройство переходит к выполнению следующей процедуры.

Процедура асинхронньй редким выполняется аналогично процедуре асин- хронньш режим с выборочным контролем с той лишь разницей, что информация в .третьем слове процедуры асинхрон- 4ПЛЙ режим представляет собой все О, т.е. анализ ошибок производится по всем каналам.

Процедура контроль z-состряния выполняется следующим образом. Блок 2 загружает в счетчик 26 адрес первого слова процедуры. Информация первого слова соответствует информации последней присутствующей в программе проверки процедуры коммутация, с той лишь разницей, что выводы контролируемого узла, находящиеся в z-состоя- нии, отмечаются О,

Далее блок 2 устанавливает адрес и данные. Адрес, расшифровываясь дешифратором 31, вырабатывает сигнал а его одиннадцатом выходе, стробируя дешифратор 32. На второй вход дешифратора 32 поступают данные, KOTOpbiej расшифровываясь, вырабатывают на его втором вьгходе импульс записи в регист 4. Таким образом, производится коммутация каналов 6, которые электрически связаны с выводами контролируемого узла, находящимися в третьем состоянии, как выходов устройства.

Последукщие два слова процедуры представляют собой две процедур, тест-набор. Информация в двух словах одинакова, за исключением каналов 6, на которых необходимо контролиро- вать z-состояние. На данных каналах в первом режиме тест-набор информация имеет значение 1, во втором резкиме тест-набор - О. Таким образом, на выводах объекта контроля, на которых контролируется z-состояние, последовательно подается значение 1 и О. Если указанные выводы контролируемого узла находятся э z-состоянии, то ошибок не возникает.

После вьшолнения процедуры коммутация восстанавливается в соответствии с последней присутствующей в програме проверки процедурой коммутации.

Диагностика контролируемого цифро- вого узла значительно упрощается в связи с наличием в устройстве: выхода 20 синхронизации;сигнатурного анализатора 10 и блока 15 инд жaции сигнатур.

В процессе поиска неисправности в контролируемом цифровом узле часто возникает необходимость увидеть на осциллографе определенный фрагмент программы проверки в определенной точке схемы контролируемого узла. Для это- го оператор должен задать режим циклической проверки без анализа ошибки и номер того кадра,который необходимо увидеть на осциллографе. Набранный оператором номер кадра поступает в блок 2, который записывает его в регистр 33 блока 9 путем вьфаботки на втором выходе адреса и данных. Данные представляют собой двоичный код наб- ранного оператором номера кадра, KOTCрый поступает на информационный вход регистра 33. Адрес vпpeдcтaвляeт собой двоичный код, который, расшифро- вываясь дешифратором 31, вырабатывает импульс на десятом выходе дешифрато- ра 31, поступакиций на..синхровход регистра 33. Таким образом;происходит запись номера кадра в регистр 33. .С выхода регистра 33 код номера кадра

поступает на второй вход узла 25 сра.в нения, на первый вход которого поступает код номера кадра с выхода счетчика 26. При достижении счетчиком 26 значения кода, записанного в регистр 33, на выходе узла 25 сравнения появляется сигнал (выход 20), который целесообразно подавать на вход внешней синхронизации осциллографа .

Наиболее эффективным средством для поиска неисправности контролируемого узла является сигнатурный анализатор. Проведя режим контроля и определив канал (каналы), на которых присутствуют ошибки, оператор задает режим циклической проверки без анализа ошибки. Подключив вход 21 к соответствующему (ошибочному) выходу контролируемого узла, оператор убеяодается в несоответствии сигнатуры эталонной (сигнатуры должны быть предварительно сняты с исправного узла). Затем, подключая вход 21 к соответствукяцим точкам контролируемого узла (двигаясь по схепе от выхода ко входу), оператор определяет неисправный элемент, т.е. эле мент, на входах которого сигнатуры истинны, на выходах - нет. Управление работой сигнатурного анализатора происходит таким образом, что запись информации в анализатор 10 производится на тех участках программы проверки, где все выходные каналы контролируемого узла имеют определенное значение. Управление работой сигнатурного анализатора осуществляется следующим образом. В исходном состоянии регистр анализатора 10 (фиг.4) и регистр блока 15 индикации сигнатур (фиг. 5) сброшены (цепи сброса не показаны).

При появлении в программе проверки процедур тест-набор или асинхронный режим блок 2 перед началом загрузки параметров процедуры в блок 9 разрешает запись информации в анализатор 10 путем установки триггера 43. в состояние 1. Установка регистра 49 в состояние 1 производится следую-- щим образом. Блок 2 на выходах устанавливает адрес и данные. Адрес, расшифровываясь дешифратором 31, вырабатывает импульс на его девятом выходе, который поступает на синхровход триггера 43. В это время на информационном входе триггера 43 присутствует уровень Лог. 1, т.е. один из разрядов (допустим, первый) данных. Уровень

23

логической единицы с выхода триггера 43 поступает на двенадцатый выход блока 9 и далее на первый вход селектора 19, разрешая поступление импульсов « записи в регистр 3 на тактовый вход регистра 47 анализатора 10. Таким образом, запись информации в регистр 47 производится синхронно с записью в регистр 3. По окончании вьтолнения ука- ю занных процедур в триггер 43 записывается О,, запрещая прохождение импульсов через селектор 19. Таким образом состояние триггера 43 определяет окно, в котором разрешается запись 15 информации в анализатор 1Q.

По окончании выполнения тест-про- грам2Ф1 блок 2 записьтает 1 в триггер 44 путем выработки на втором выхотри регистра, блок управления ,сигнатурный анализатор, блок памяти, 1 ,узлов сравнения и 1 формирователей импульсов, причем первый вход i-ro узла сравнения ( 1) соединен с выходом i-ro формирователя импульсов и является i-M входом-выходом устройства для подключения к информационному входу-выходу контролируемого узла, первый выход блока управления подключен к адресному входу блока памяти, второй выход блока управления являет- гя вьпсодом индикации состояния устройства, информационный вход сигнатурно- fro анализатора является входом устройства для подключения к диагностируе- ,ой точке контролируемого узла, вход сброса сигнатурного анализатора соёде адреса и данных. Адрес, расшифровы-20 Динен с третьим выходом блока управ- ваясь дешифратором 31, вырабатывает строб на его девятом выходе, который поступает на синхровход триггера 44. В это время на информационном входе триггера 44 присутствует уровень Лог.1, т.е. один из разрядов (допустим, второй) данных. Лог.,1 с выхода триггера. 44 поступает на вход регистра 46 сдвига, переключая его в

25

ления, отличающееся тем, что, с целью расширения области применения за счет обеспечения проверки цифровых узлов с независимой синхронизацией и произвольными начальными состояниями, оно содержит четвертый и пятый регистры, 1 элементов И, блок индикации сигнатур, первый коммутатор, jrpynny 1 коммутаторов, элемент ИЛИ и

режим сдвига. Регистр 46 сдвига (пред-30 селектор, при этом i-й информационный вход первого регистра подключен к выходу i-ro узла сравнения, i-e информационные входы второго и третьего регистров соединены с i-м выходом бловарительно обнуленный состоянием О

триггера 44) под действием тактовых

импульсов, поступающих на его первый

вход, начинает записывать единицу,

последовательно вырабатьшая на пepвoм 35 памяти, i-й информационный вход пер

вой группы входов первого коммутатора подключен к выходу i-ro коммутатора Лог.,1 с первого выхода регистра

46 сдвига поступает на такт.овый вход

втором и третьем входах уровень . ;Г.

группы и к i-му входу кода операции .блока управления, синхровход, i-й инрегистра 49 блока 15 индикахщи сигна- 40 Формахщонный вход и i-й выход четвертого регистра подключены соответственно к четвертому выходу блока управления, выходу i-ro узла сравнения и первому информационному входу i-ro 45 коммутатора группы, первый и второй входы и выход i-ro элемента И соединены соответственно с выходом i-ro узла сравнения, i-м выходом пятого регистра и i-м инфортур, производя перезапись в него информации из анализатора 10. Записанный в регистр блока 15 код сигнатуры поступает на шифратор. 50 и далее - на индикатор 51. Затем уровень Лог. 1 появляется на втором выходе,регистра 46 сдвига, который поступает на вход анализатора 10, производя ег.о сброс. Таким образом происходит индикация полученной сигнатуры и подготовка для 50 Ционным входом второй группы входов следующего цикла записи. Уровень первого коммутатора, синхровход и ЛоГо 1 с третьего выхода поступает выход первого регистра подключены на вход сброса триггера 44, который соответственно к пятому выходу блока приводит регистр 46 в исходное состоя- управления и второму информационному ние., 55 коммутатора группы, шестой

выход блока управления соединен с уп- Фррмула изобретения равляняцим входом блока индикации сиг 1. Устройство для контроля и диаг- натур, информационный вход которого ностики цифровых .узлов, содержащее подключен к выходу сигнатурного ана«5

51324

три регистра, блок управления ,сигнатурный анализатор, блок памяти, 1 ,узлов сравнения и 1 формирователей импульсов, причем первый вход i-ro узла сравнения ( 1) соединен с выходом i-ro формирователя импульсов и является i-M входом-выходом устройства для подключения к информационному входу-выходу контролируемого узла, первый выход блока управления подключен к адресному входу блока памяти, второй выход блока управления являет- гя вьпсодом индикации состояния устройства, информационный вход сигнатурно- fro анализатора является входом устройства для подключения к диагностируе- ,ой точке контролируемого узла, вход сброса сигнатурного анализатора соёДинен с третьим выходом блока управ-

ления, отличающееся тем, что, с целью расширения области применения за счет обеспечения проверки цифровых узлов с независимой синхронизацией и произвольными начальными состояниями, оно содержит четвертый и пятый регистры, 1 элементов И, блок индикации сигнатур, первый коммутатор, jrpynny 1 коммутаторов, элемент ИЛИ и

ный вход первого регистра подключен к выходу i-ro узла сравнения, i-e информационные входы второго и третьего регистров соединены с i-м выходом бло памяти, i-й информационный вход пер

вой группы входов первого коммутатора подключен к выходу i-ro коммутатора

группы и к i-му входу кода операции .блока управления, синхровход, i-й инФормахщонный вход и i-й выход четвертого регистра подключены соответственно к четвертому выходу блока управления, выходу i-ro узла сравнения и первому информационному входу i-ro коммутатора группы, первый и второй входы и выход i-ro элемента И соединены соответственно с выходом i-ro узла сравнения, i-м выходом пятого регистра и i-м инфор Ционным входом второй группы входов первого коммутатора, синхровход и выход первого регистра подключены соответственно к пятому выходу блока управления и второму информационному коммутатора группы, шестой

25

лиэатора, синхровход которого соединен с выходом селектора, синхровход,. i-й информа1щонный вход и i-й выход литого регистра подключены соответстт венно к седьмому выходу блока управления, i-му выходу блока памяти и управляющему входу i-ro коммутатора группы, синхровход и i-й выход второго регистра соединены соответственно с восьмым выходом блока управления и управляющим входом i-ro формирователя импульсов, управляющий вход и i-й выход первого коммутатора подключены соответственно к девятому выходу блок управления и i-му входу элемента ИЛИ, выход которого соединен с входом начальной установки блока управления, синхровход и i-й выход третьего региг стра подключены соответственно к десятому выходу блока управления и второму входу i-ro узла сравнения, кото- 1.

рый также соединен с информационным входом i-ro формирователя импуха сов, вход режима блока управления объединен с информационным входом блока памяти и является входом устройства для загрузки программы п|эоверки контролируемого узла, одиннадцатый выход

блока управления является выходом уст-30 информационным входом третьего регист- ройства для подключения к синхровходу контролируемого узла, двенадцатый вы- Код блока управления подключен к информационному входу селектора, управляющий вход которого соединен с пятым выходом блока управления.

35

ра, инфopмaIl oнным входом второго счетчика, выход которого подключен к второму входу операции микропрограммного узла управления, третий вход операхщи которого соединен с четвертым информационным входом коммутатора, инфррмационным входом группы триггеров установки и является вторым входом блока, выход первого узла срав- .сравнения подключен к пятому информационному входу коммутатора, тестой информационга 1й вход которого соединен с выходом группы триггеров установки и четвертым входом операции микропрограммного узла управления, пятый вход операции которого объединен с пятым информационньм входом коммутатора, управляюпогй вход которого подключен к шестому выходу первого JQ дешифратора, первый выход микропрог граммного узла управления соединен с первым входом элемента задержки, второй вход которого подключен к информационному входу второго счетчика, синхровход которого соединен с вторым выходом микропрограммного узла управления, третий вход элемента задержки подключен к седьмому выходу первого дешифратора, восьмой выход которого

10

15

751326

первого дешифратора и является первьтц выходом блока, второй и третий выход первого дешифратора соединены соответственно с синхровходами третьего и второго регистров, выход второго регистра подключен к второму входу первого узла сравнения, четвертый выход первого дешифратора соединен с входом записи второго счетчика, выход которого подклкзчен к второму информационному входу коммутатору, третий информационный вход которого соединен с выходом первого счетчика, вход записи которого подключен к пятому выходу первого дешифратора, первый выход генератора импульсов соединен с первым синхровходом микропрограммного узла управления, второй выход генератора импульсов подключен к синхровходу регистра сдвига, вход режима которого соединен с выходом четвертого триггера , синхровход которого объединен с синхровходом третьего триггера, информационный вход которого объединен с информационным входом четвертого триггера, первым входом операции микропрограммного узла управления, информационным входом второго регистра.

20

25

30 информационным входом третьего регист-

35

40

., , ра, инфopмaIl oнным входом второго счетчика, выход которого подключен к второму входу операции микропрограммного узла управления, третий вход операхщи которого соединен с четвертым информационным входом коммутатора, инфррмационным входом группы триггеров установки и является вторым входом блока, выход первого узла срав- .сравнения подключен к пятому информационному входу коммутатора, тестой информационга 1й вход которого соединен с выходом группы триггеров установки и четвертым входом операции микропрограммного узла управления, пятый вход операции которого объединен с пятым информационньм входом коммутатора, управляюпогй вход которого подключен к шестому выходу первого JQ дешифратора, первый выход микропрог граммного узла управления соединен с первым входом элемента задержки, второй вход которого подключен к информационному входу второго счетчика, синхровход которого соединен с вторым выходом микропрограммного узла управления, третий вход элемента задержки подключен к седьмому выходу первого дешифратора, восьмой выход которого

5

соединен с вторым синхровходом микропрограммного узла управления, шестой вход операции которого подключен к выходу элемента задержки,.четвертый вход, третьего элемента ИЛИ соединен с выхо10

15

которого соединен с третьим выходом генератора импульсов, девятый выход первого дешифратора подключен к син- ровходу третьего триггера, выход которого является двенадцатым выходом блока, десятый выход первого дешифратора соединен с синхровходом первого регистра, одиннадцатый выход первого дешифратора подключен к стробирующе- му входу второго дешифратора, первый выход которого соединен с входом установки первого триггера, выход которого подключен к первому входу элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к третьему выходу микропрограммного узла управления, четвертый выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к первому выходу второго дешифратора, информационный вход которого соединен с информационным входом первого регистра информационным входом третьего регистра и вместе с вхо- зо дом первого дешифратора образует вход режима блока, вход установки второго триггера подключен к выходу третьего элемента ИЛИ, первый вход которого соединен с пятым -выходом микропрограм-

20

25

дом элемента И, второй вход которого подключен к стробирукнцему входу второ го депифратрра, второй выход которого является восьмым выходом блока, двенадцатый выход первого дешифратора соединен с входом сброса первого триггера и входом сброса второго триггера, выход которого вместе с выходом ком. татора образуют второй выход блока, первый выход регистра сдвига является шестым выходом блока, второй выход регистра сдвига является третьим выходом блока,третий выход регистра сдвига подключен к входу сброса четвертого триггера, выход третьего регистра соединен с информаци- онным входом первого счетчика, счетный вход которого подключен к седьмому выходу микропрограммного узла управления, вькод первого элемента ИЛИ является пятым выходом блока, выход второго элемента ИЛИ является десятым выходом блока, третий выход второго дешифратора является седьмым выходом блока, третий вход элемента И соединен с информационным входом группы триггеров установки, а выход второго узла сравнения является одиннадцатым выходом блока.

много узла управления, шестой выход которого подключен к синхррвходу, группы триггеров установки, второй вход

0

5

о

0

5

дом элемента И, второй вход которого подключен к стробирукнцему входу второ го депифратрра, второй выход которого является восьмым выходом блока, двенадцатый выход первого дешифратора соединен с входом сброса первого триггера и входом сброса второго триггера, выход которого вместе с выходом ком. татора образуют второй выход блока, первый выход регистра сдвига является шестым выходом блока, второй выход регистра сдвига является третьим выходом блока,третий выход регистра сдвига подключен к входу сброса четвертого триггера, выход третьего регистра соединен с информаци- онным входом первого счетчика, счетный вход которого подключен к седьмому выходу микропрограммного узла управления, вькод первого элемента ИЛИ является пятым выходом блока, выход второго элемента ИЛИ является десятым выходом блока, третий выход второго дешифратора является седьмым выходом блока, третий вход элемента И соединен с информационным входом группы триггеров установки, а выход второго узла сравнения является одиннадцатым выходом блока.

«..;

./

Tl 12

Фие.

фиг. 5

Фиг. 6

г 7

Фиэ.в

Зчпаскщюданные кана/гы (хо устройства)

Дииамичкк11е Ч 1 / &jftaHiwcKue каналы канальНвтоды NJ/ (Выходы ) tfcmpotxfnoa /.. ,- ,

уипройст( а

Слттическив намолы fSxoffb/ и Sbixo i ycmpt cmSa)

I I I I 1 I ,

III II-.

Ш-ГГ: -;..

I r-f-

I I.

nti

,.l

Mn/imtfn i n Z Номера HoffpoS

Фиг

Канал fJsj HjHonflsZ

Состояние

Пачка

Условие 0 i/CJ7odue 7

л « л о

0000 .-„.. задан.

0001

Зи Запись регистр S

00 10

ООП

Запись б регистр 3

Нет

0100

ЗаписьЛ

0101

L

( Конец J

01 10

0777

а

yc/naHo6f ct

Услодие 0 Условие 7

да

Да

Запись о регис/пр S

Ло

i

Запись 8 регистр 3

I

Запись 6 схему

Ма

Нет

OJSMLJI в

блок Z

Фиг.Ю

Первый Выход

Второй Выход

Треглий Ьымд

J

шшллллллл.

Фае,п

Г

22

Редактор Н. Яцола

Составитель Г. Виталиев

Техред л.Сердюкова Корректор Л. Вескщ

Заказ 2421

Тираж 569

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

л

2J

2«

Фае. 12

Подписное

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1987-08-03—Подача