вода соответственно, третий выход узла имитации сигналов соединен с информационным входом регистра входных данных, второй управляющий вход которого соединен со стробирующим выходом узла имитации сигналов, четвеотьй выход которого соединен с первым управляющим входом узла контроля, группой управляющих входов узла фиксации режима работы и второй группой управляющих входов узла анализа управляющих сигналов, третья группа информационных выходов регистра режимов и управляющий выход узлп фиксации режима работы соединены с третьим входом узла имитации сигналов, четвертьп вход которого соединен с информационным выходом регистра выходных данных, причем управляющий выход узла фиксации режима работы соединен с вторым управляющим входом узла контроля, при этом узел имитации сигналов содержит два мультиплексора, дешифратор, триггер, два элемента И и группу элементов Н, причем первые входы элементов Н группы и первый информационный вход первого мультиплексора образуют первый вход узла имитации, первый информационныйвход второго мультиплексора образует второй вход узла имитации, первые единичный и нулевой входы триггера и первьш вход первого элемента И образуют третий вход и второй вход узла имитации, группа входов второго элемента И и дешифратора и второй информационньй вход первого мультиплексора образуют четвертый вход и первый выход узла имитации, выходы первого и второго мультиплексоров являются третьим и четвертым выходами узла имитации соответственно, выход первого элемента И является стробирующим выходом узла имитации, выход второго элемента И соединен с вторым единичным и нулевым входами триггера, третьи единичньй и нулевой входы которого соединены с соответствующими выходами дешифратора, группа выходов которого соединена с вторыми входами элементов И группы, выходы которых соединены с вторым информационным входом второго мультиплексора, управляющий вход которого соединен с управляющим входом . первого мультиплексора, с вторым входом первого элемента И и с выходом триггера.

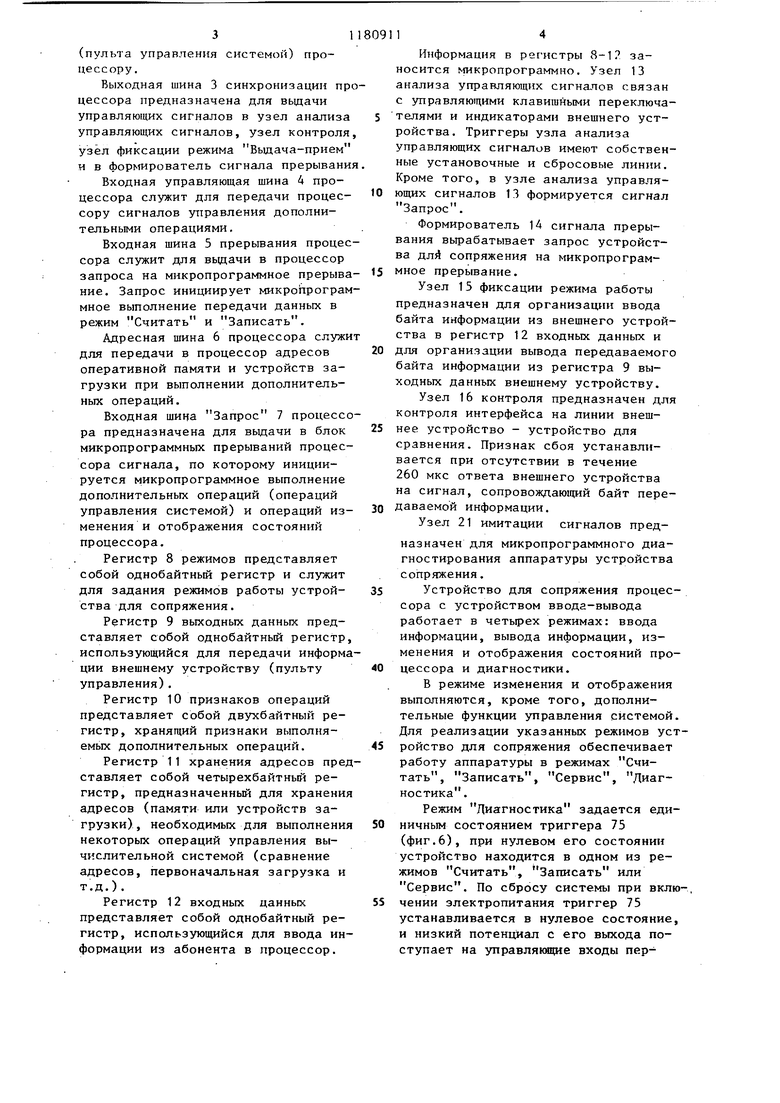

2.Устройство по П.1, отличающееся тем, что узел фиксации режима работы содержит пять триггеров, четыре элемента И и элемент ИЛИ, причем первые входы первого и второго элементов И и первый вход третьего элемента И образуют группу синхровходов узла, второй вход первого элемента И и первый вход четвертого элемента И образуют группу управляющих входов узла, второй вход третьего элемента Н, второй вход четвертого элемента И, нулевой вход первого триггера образуют вход режима узла, единичный вход второго триггера является установочным входом узла, выход третьего элемента И соединен с первыми единичными входами первого и третьего триггеров первьм входом элемента ИЛИ и является стробирующим выходом узла, выход первого триггера соединен с вторым входом элемента ИЛИ, первым единичным входом четвертого триггера и является сигнальным выходом узла, вывыход четвертого триггера является управляющим выходом узла, при этом

в узле фиксации режима работы второй вход первого элемента И соединен с первым нулевым входом пятого триггера, нулевым и вторым единичным входами третьего триггера, выход которого соединен с третьим входом первого элемента И и вторым входом второго элемента И, выход которого соединен с вторым нулевым входом пятого триггера, единичный вход которого соединен с выходом первого элемента И, а выход - с третьим входом третьего элемента И, четвертый вход кото.рого соединен с выходом элемента ИЛИ, второй единичный вход первого триггера соединен с выходом четвер.того элемента И, третий вход которого соединен с выходом второго триггера и вторым единичным входом четвертого триггера, первый и второй нулевые входы которого соединены с нулевым входом второго триггера и первым входом четвертого элемента И.

3.Устройство по П.1, о т л и чающееся тем, что узел анализа управляющих сигналов содержит двенадцать триггеров, два элемента И, элемент ИЛИ, причем первый вход первого элемента И, первый единичный вход первого триггера и синхровход второго триггера образуют группу синхровходов узла, первый единичный вход четвертого триггера, первый единичный и нулевой входы ПЯтого триггера, первый единичный вход шестого триггера, нулевой вход седьмого триггера, второй вход первого элемента И, первый вход элемента ИЛИ и нулевой вход второго триггера образуют первую группу управляющих входов узла, первый и -второй единичные входы третьего триггера, вторые единичные входы пятого и шестого триггеров, единичный вход восьмого триггера и второй единичный ,-вхрд первого триггера образуют вторую группу управляющих входов узла, второй вход элемента ИЛИ является входом запроса узла, первый единичный вход седьмого триггера является установочным входом узла, выходы второго, седьмого, девятого, десятого, одиннадцатого и двенадцатого триггеров, элемента ИШ и единичньй выход третьего триггера образуют информационный выход узла, выход элемента ИЛИ, кроме этого является запускающим выходом узла, выход второго элемента И является выходом запроса узла, при этом в узле анализа управляющих :сигналов нулевой вход третьего триггера соединен со своими .единичными входами единичный выход третьего триггера соединен с первым единичным входом второго триггера, второй единичньй вход которого соединен с выходом четвертого триггера, нулевой вход которого соединен с выходом второго триггера и с третьим входом элемента ИЛИ, синхровход которого соединен с синхровходами девятого, десятого и одиннадцатого триггеров, выходы которых соединены с четвертым, пятым и шестым входами элемента ИЛИ соответственно, седьмой вход которого соединен с выходом седьмого триггера, второй единичный вход которого соединен с первым единичным входом пятого триггера, второй единичный вход которого соединен с первым единичным входом девятого триггера, второй единичный и нулево

входы которого соединены с выходом пятого триггера, нулевой выход третьего триггера соединен с вторым единичным входом четвертого триггера, второй единичный вход шестого триггера соединен с первым единичным входом десятого триггера, второ единичный и нулевой входы которого соединены с выходом шестого триггера, нулевой вход которого соединен с нулевыми входами пятого и восьмого триггеров, единичный вход.которого соединен с первым единичным входом одиннадцатого триггера, второй единичный и нулевой входы которого соединены с выходом восьмого триггера, нулевой вход седьмого триггера соединен с первым входом второго элемента И, второй вход которого соединен с выходом двенадцатого триггера, первый единичный вход которого соединен с вторым единичным входом первого триггера, выход которого соединен с вторым единичным и нулевым входами двенадцатого триггера, выход первого элемента И соединен с нулевым входом первого триггера.

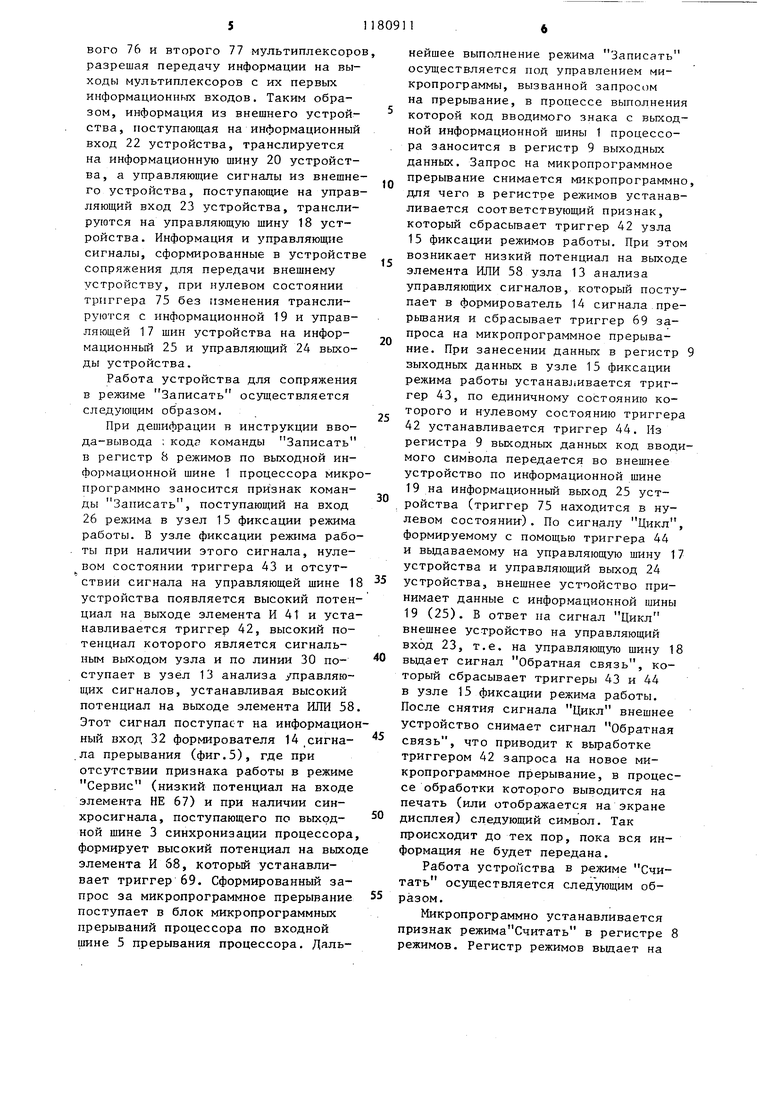

4. Устройство по п.1,о тл ичающееся тем, что узел контроля содержит триггер, три элемента И, элемент ИЛИ, элемент НЕ, элемент задержки, причем вход элемента НЕ соединен с входом элемента зaдepжkи, первым входом первого элемента И и является синхровходом узла, первый и второй входы элемента ИЛИ являются первым и вторым управляющими входами узла соответственно выход второго элемента И является выходом узла, при этом выход элемента задержки соединен с первым входом третьего элемента И и вторым входом первого элемента И,,выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом триггера, первьй единичный вход которого, соединен с выходом третьего элемента И второй вход которого соединен с выходом элемента НЕ, вькод элемента ИЛИ соединен с нулевым и вторым единичным; входами триггера.

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессора с устройствами ввода-вывода, в том числе с устройствами, работающими в качестве пультов управления вычислительной системой.

Целью изобретения является повышение достоверности путем организации микропрограммного диагностирования оборудования.

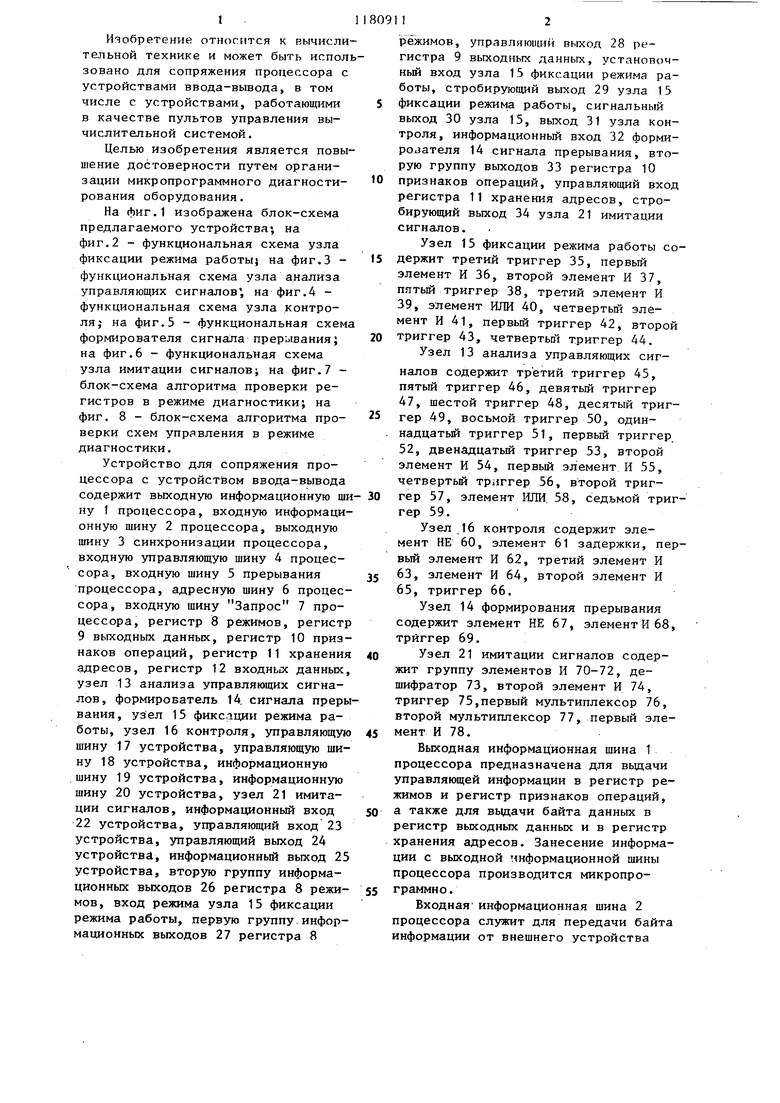

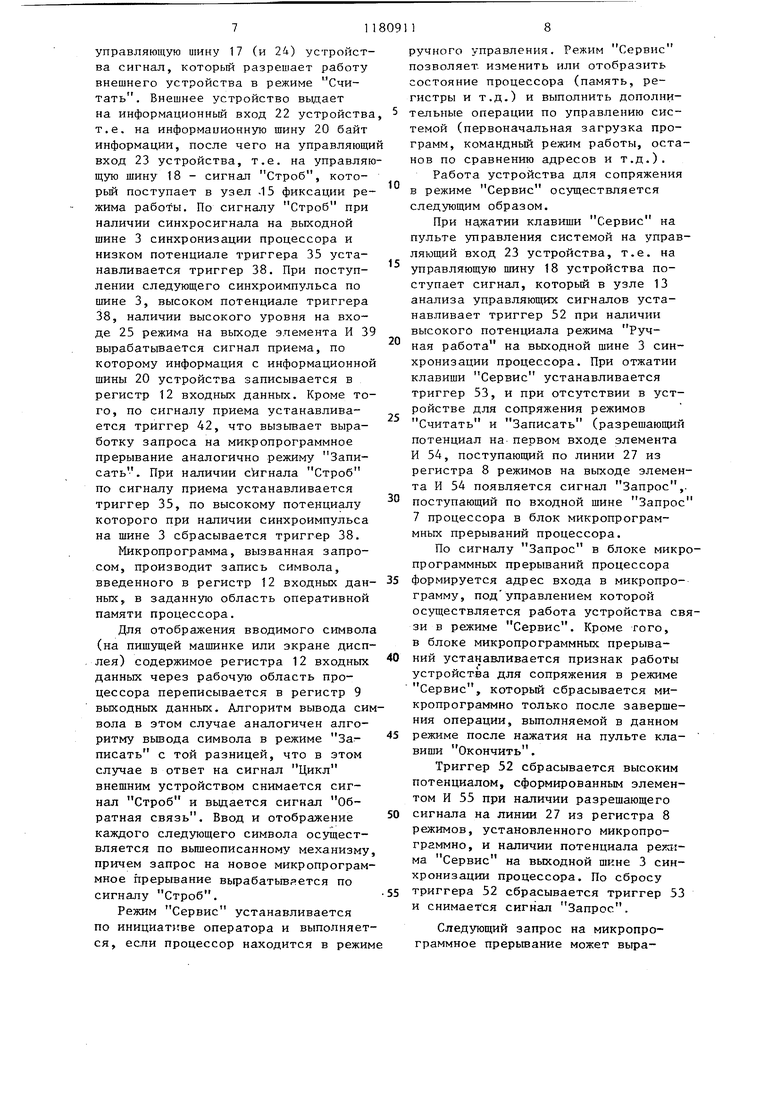

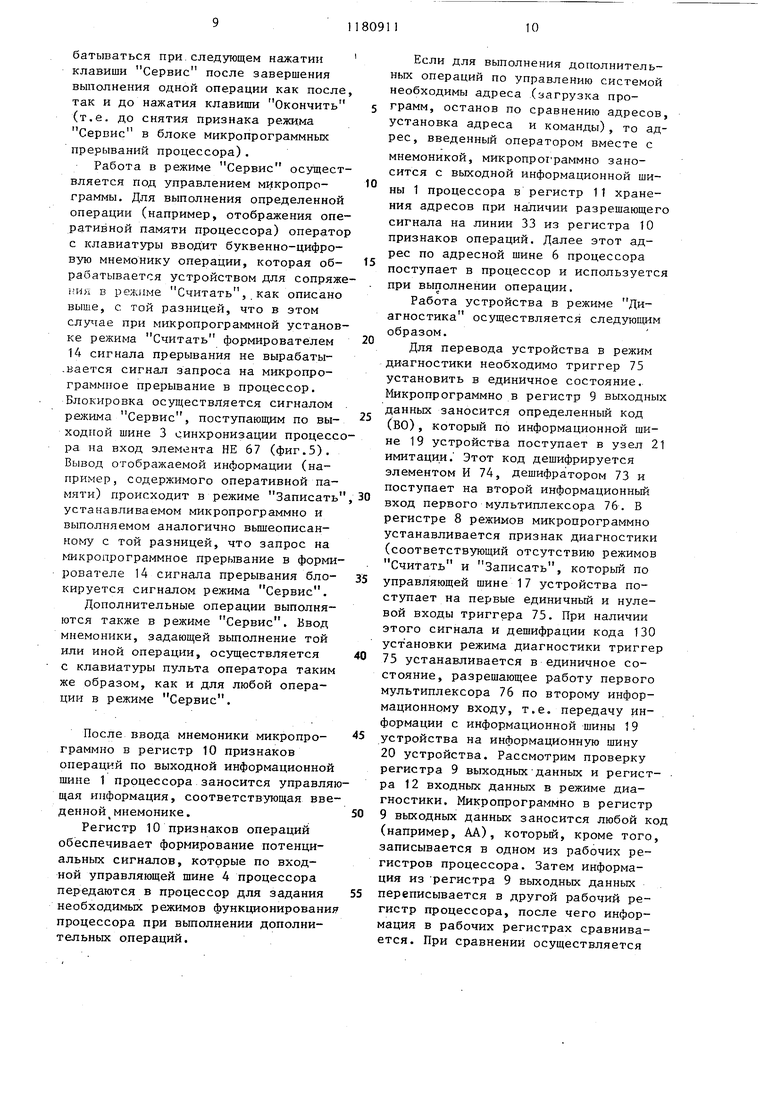

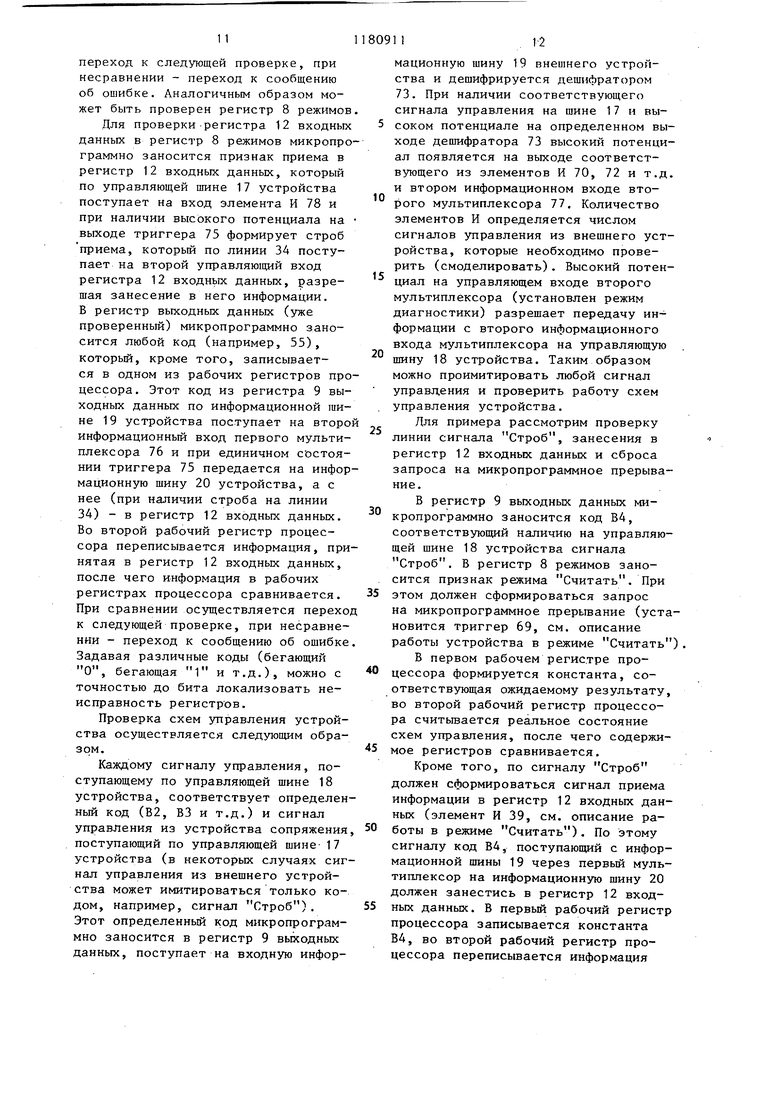

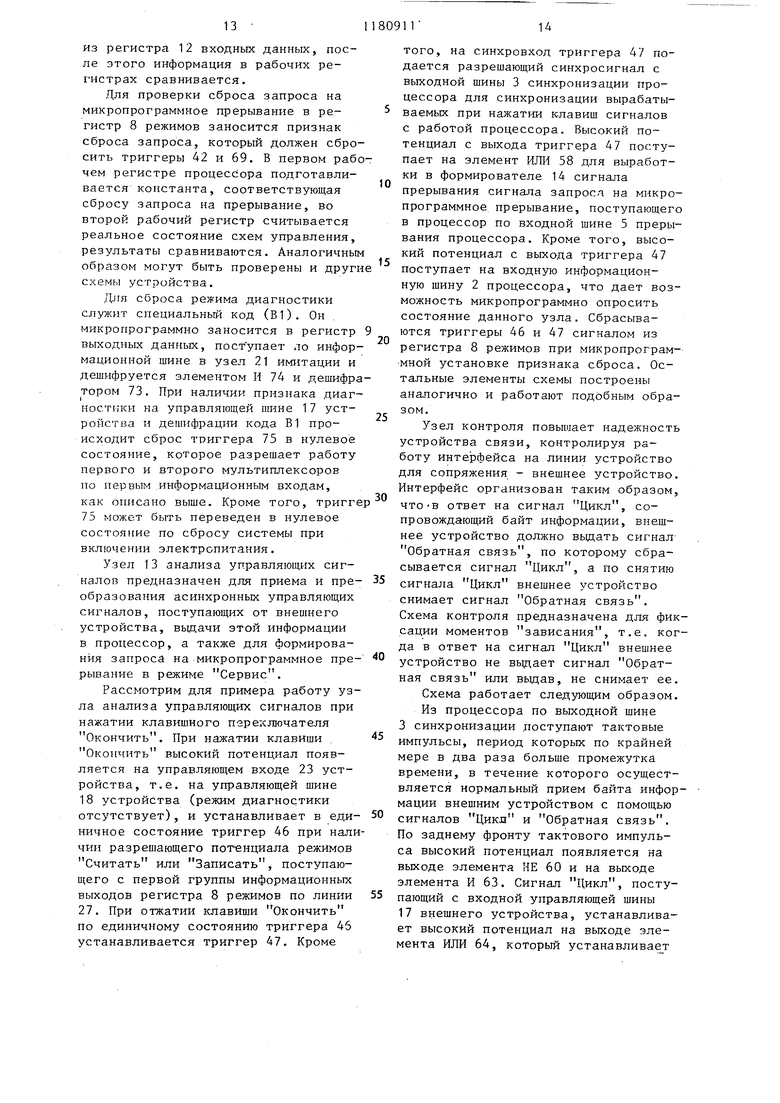

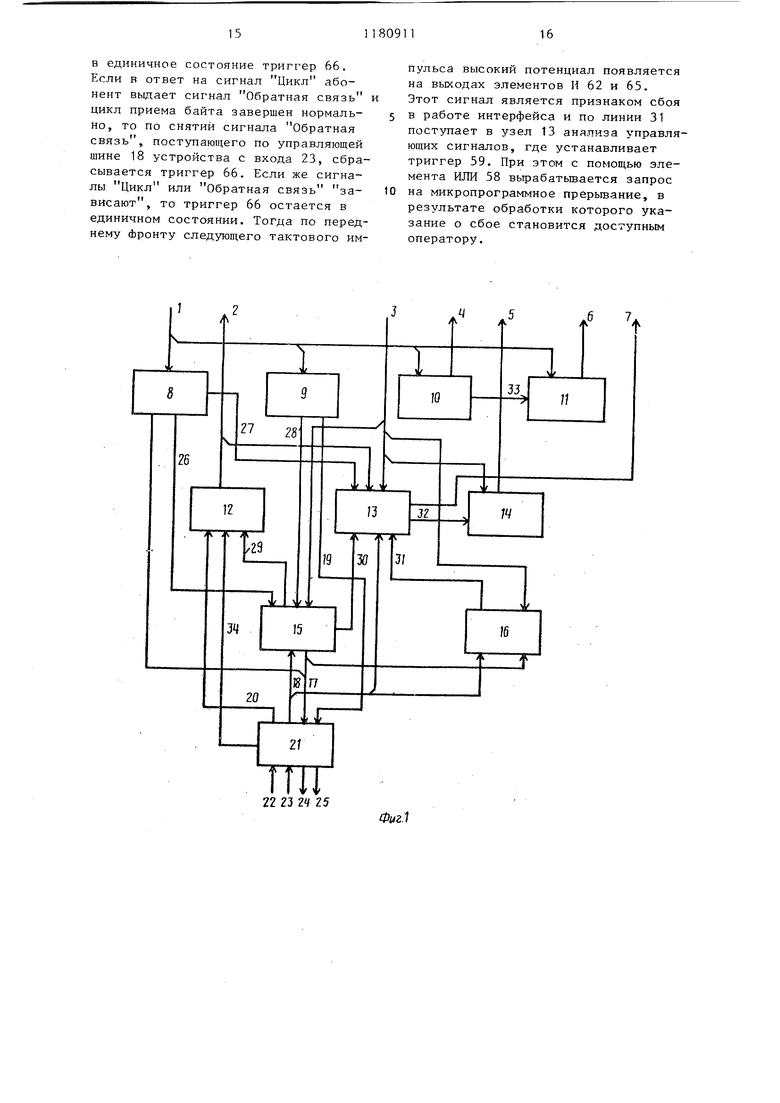

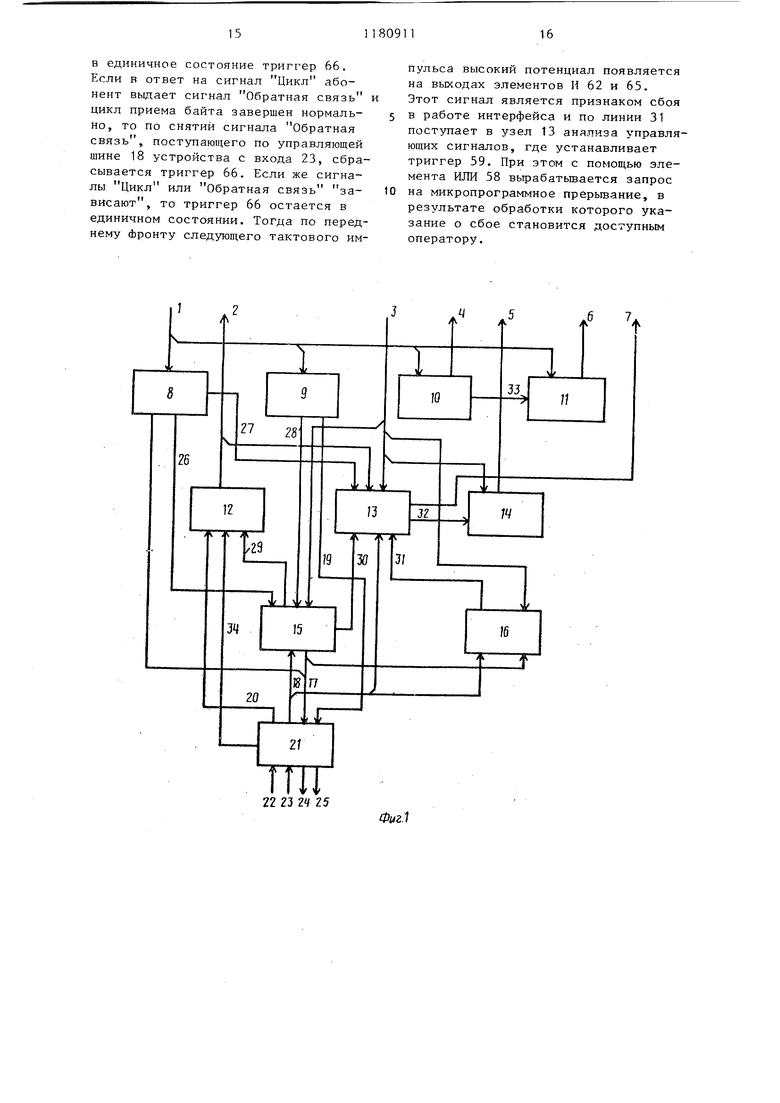

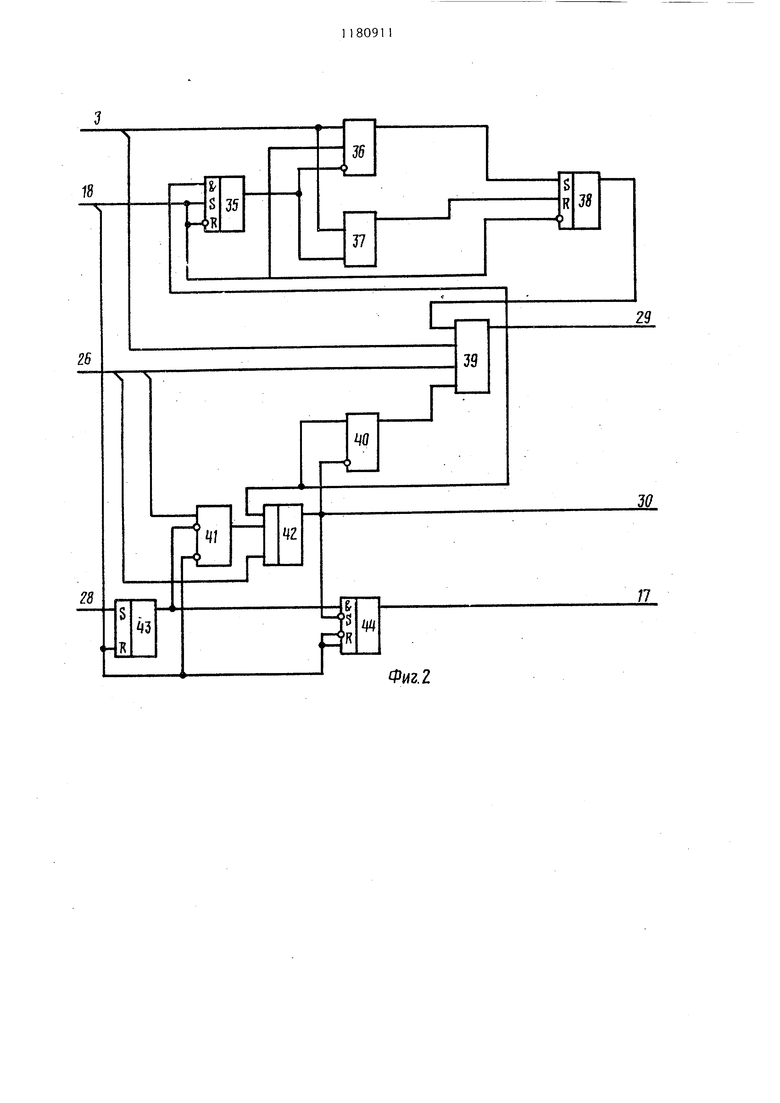

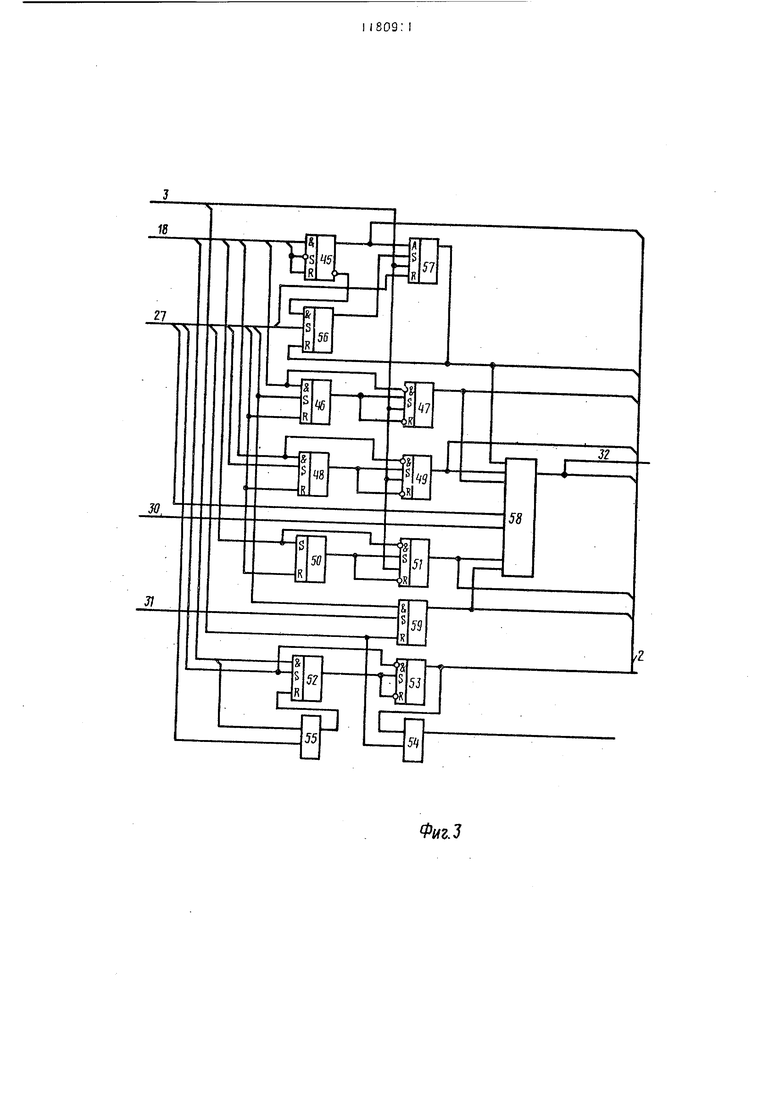

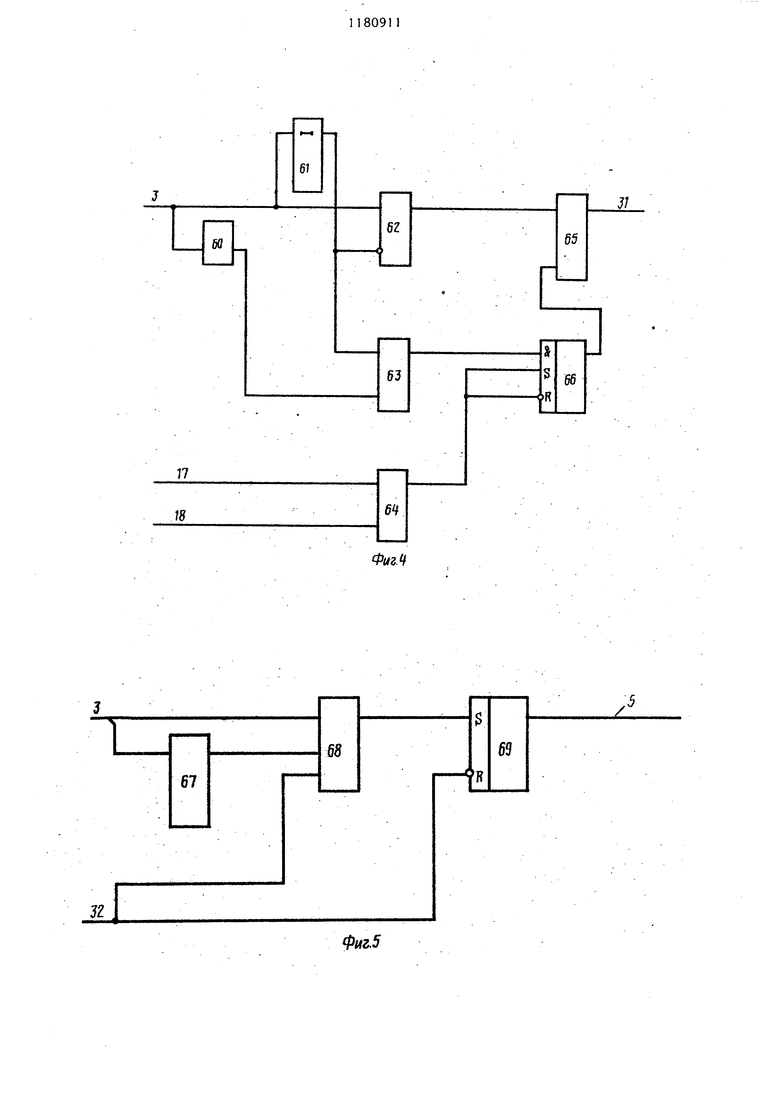

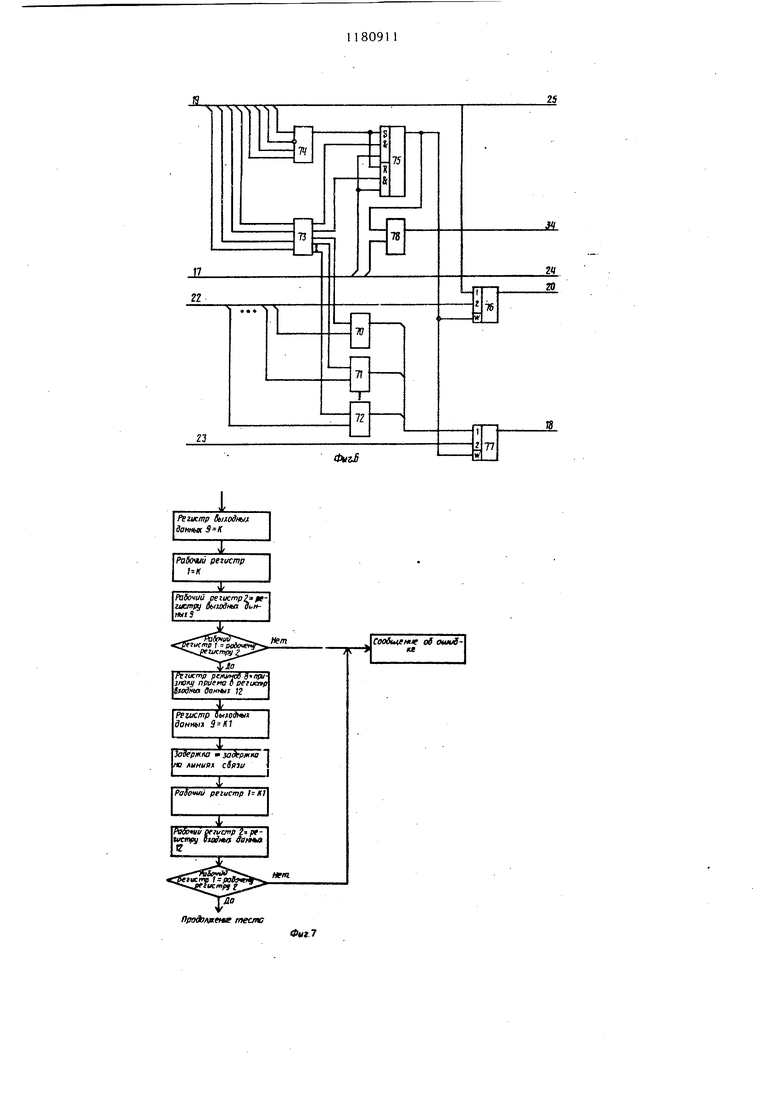

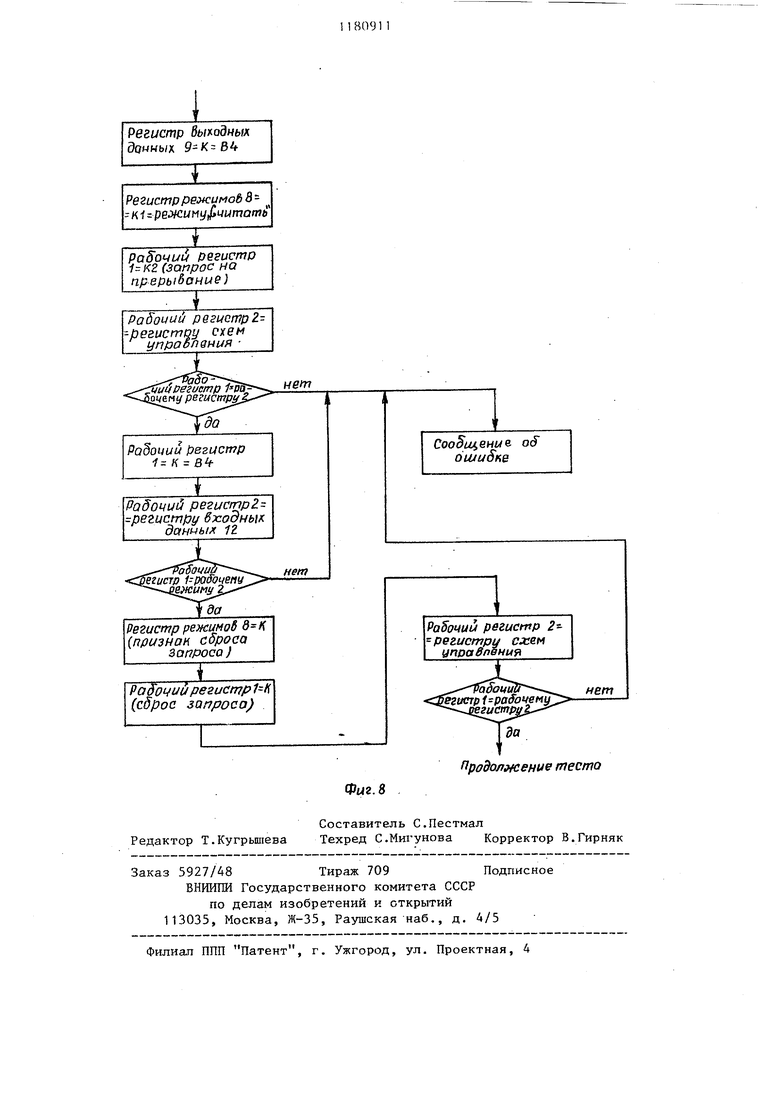

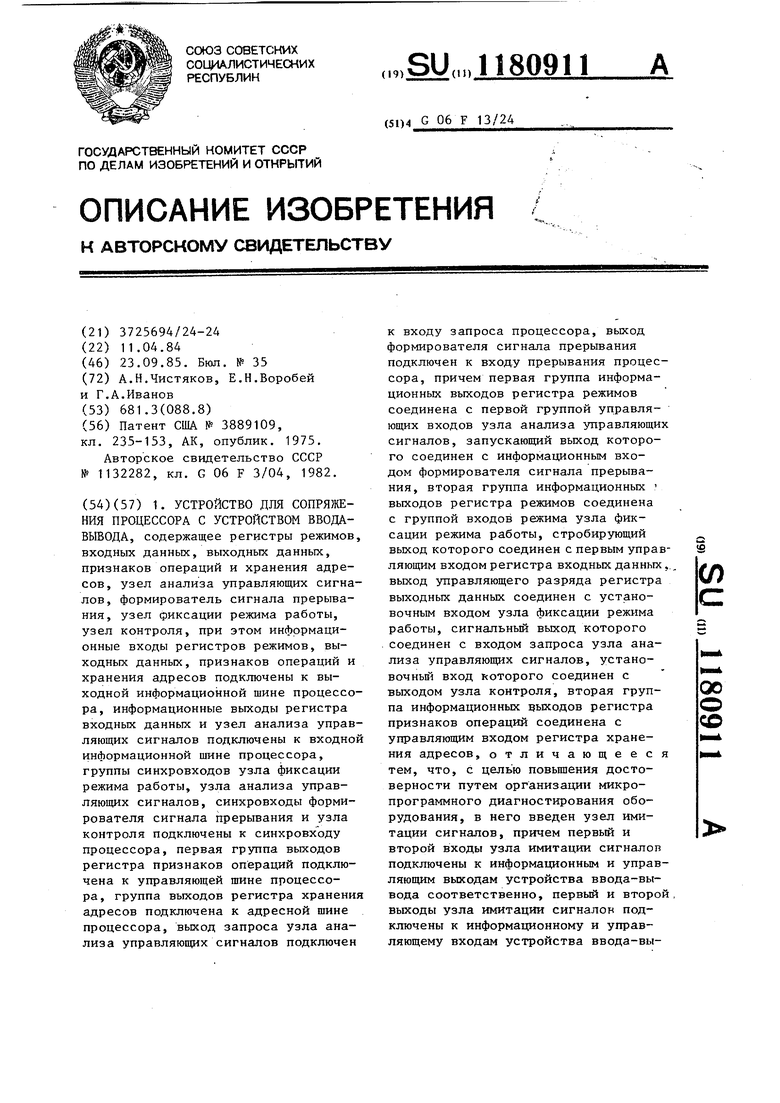

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 - функциональная схема узла фиксации режима работы; на фиг.З функциональная схема узла анализа управляющих сигналов , на фиг.4 функциональная схема узла контроля; на фиг.З - функциональная схема формирователя сигнала прерывания; на фиг.6 - функциональная схема узла имитации сигналов; на фиг.7 блок-схема алгоритма проверки регистров в режиме диагностики; на фиг. 8 - блок-схема алгоритма проверки схем управления в режиме диагностики.

Устройство для сопряжения процессора с устройством ввода-вывода содержит выходную информационную шину 1 процессора, входнзпо информационную шину 2 процессора, выходную шину 3 синхронизации процессора, входную управляющую шину 4 процессора, входную шину 5 прерывания процессора, адресную шину 6 процессора, входную шину Запрос 7 процессора, регистр 8 режимов, регистр 9 выходных данных, регистр 10 признаков операций, регистр 11 хранения адресов, регистр 12 входньос данных, узел 13 анализа управляющих сигналов, формирователь 14. сигнала прерывания, узел 15 фиксации режима работы, узел 16 контроля, управляющую шину 17 устройства, управляющую шину 18 устройства, информационную шину 19 устройства, информационную шину 20 устройства, узел 21 имитации сигналов, информационный вход 22 устройства, управляющий вход 23 устройства, управляющий выход 24 устройства, информационный выход 25 устройства, вторую группу информационных выходов 26 регистра 8 режимов, вход режима узла 15 фиксации режима работы, первую группу информационных выходов 27 регистра 8

режимов, управляющий выход 28 регистра 9 выходных данных, установочный вход узла 15 фиксации режима работы, стробирующий выход 29 узла 15 фиксации режима работы, сигнальный выход 30 узла 15, выход 31 узла контроля, информационный вход 32 формирователя 14 сигнала прерывания, вторую группу выходов 33 регистра 10

признаков операций, управляющий вход регистра 11 хранения адресов, стробирующий выход 34 узла 21 имитации сигналов.

Узел 15 фиксации режима работы содержит третий триггер 35, первый элемент И 36, второй элемент И 37, пятый триггер 38, третий элемент И 39, элемент ИЛИ 40, четвертый элемент И 41, первый триггер 42, второй

триггер 43, четвертьп триггер 44.

Узел 13 анализа управляющих сигналов содержит третий триггер 45, пятый триггер 46, девятый триггер 47, шестой триггер 48, десятый триггер 49, восьмой триггер 50, одиннадцатьй триггер 51, первый триггер

52, двенадцатый триггер 53, второй

элемент И 54, первый элемент И 55,

четвертый триггер 56, второй триггер 57, элемент ИЛИ. 58, седьмой триггер 59.

Узел 16 контроля содержит элемент НЕ 60, элемент 61 задержки, первый элемент И 62, третий элемент И

63, элемент И 64, второй элемент И 65, триггер 66.

Узел 14 формирования прерывания содержит элемент НЕ 67, элемент И 68, триггер 69.

Узел 21 имитации сигналов содержит группу элементов И 70-72, дешифратор 73, второй элемент И 74, триггер 75,первый мультиплексор 76, второй мультиплексор 77, первый элемент И 78.

Выходная информационная шина 1 процессора предназначена для вьщачи управляющей информации в регистр режимов и регистр признаков операций,

а также для вьщачи байта данных в регистр выходных данных и в регистр хранения адресов. Занесение информации с выходной информационной шины процессора производится микропрограммно.

Входная информационная шина 2 процессора служит для передачи байта информации от внешнего устройства

31

(пульта управления системой) процессору.

Выходная шина 3 синхронизации процессора предназначена для выдачи управляющих сигналов в узел анализа управляющих сигналов, узел контроля, узел фиксации режима Выдача-прием и в формирователь сигнала прерывания

Входная управляющая шина 4 про, цессора служит для передачи процес сору сигналов управления дополнительными операциями.

Входная шина 5 прерывания процессора служит для вьщачи в процессор запроса на микропрограммное прерывание. Запрос инициирует микропрограммное выполнение передачи данных в режим Считать и Записать.

Адресная шина 6 процессора служи для передачи в процессор адресов оперативной памяти и устройств загрузки при выполнении дополнительных операций.

Входная шина Запрос 7 процессора предназначена для выдачи в блок микропрограммных прерываний процессора сигнала, по которому инициируется микропрограммное выполнение дополнительных операций (операций управления системой) и операций изменения и отображения состояний процессора.

Регистр 8 режимов представляет собой однобайтный регистр и служит для задания режимов работы устройства для сопряжения.

Регистр 9 выходных данных представляет собой однобайтный регистр, использующийся для передачи информации внешнему устройству (пульту управления).

Регистр 10 признаков операций представляет собой двухбайтный регистр, хранящий признаки выполняемых дополнительных операций.

Регистр 11 хранения адресов представляет собой четырехбайтный регистр, предназначенный для хранения адресов (памяти или устройств загрузки) , необходимых для выполнения некоторых операций управления вычислительной системой (сравнение адресов, первоначальная загрузка и т.д.).

Регистр 12 входных данных представляет собой однобайтный регистр, использующийся для ввода информации из абонента в процессор.

14

Информация в регистры 8-1 заносится микропрограммно. Узел 13 анализа управляющих сигналов связан с управляющими клавишными переключателями и индикаторами внешнего устройства. Триггеры узла анализа управляющих сигналов имеют собственные установочные и сбросовые линии. Кроме того, в узле анализа управляющих сигналов 13 формируется сигнал Запрос.

Формирователь 14 сигнала прерывания вьфабатывает запрос устройства дли сопряжения на микропрограммное прерывание.

Узел 15 фиксации режима работы предназначен для организации ввода байта информации из внешнего устройства в регистр 12 входных данных и для организации вывода передаваемого байта информации из регистра 9 выходных данных внешнему устройству.

Узел 16 контроля предназначен для контроля интерфейса на линии внешнее устройство - устройство для сравнения. Признак сбоя устанавливается при отсутствии в течение 260 МКС ответа внешнего устройства на сигнал, сопровождающий байт передаваемой информации.

Узел 21 имитации сигналов предназначен для микропрограммного диагностирования аппаратуры устройства сопряжения.

Устройство для сопряжения процессора с устройством ввода-вывода работает в четырех режимах: ввода информации, вывода информации, изменения и отображения состояний процессора и диагностики.

В режиме изменения и отображения выполняются, кроме того, дополнительные функции управления системой Для реализации указанных режимов усройство для сопряжения обеспечивает работу аппаратуры в режимах Считать, Записать, Сервис, Диагностика.

Режим Диагностика задается единичным состоянием триггера 75 (фиг.6), при нулевом его состоянии устройство находится в одном из режимов Считать, Записать или Сервис. По сбросу системы при вкл чении электропитания триггер 75 устанавливается в нулевое состояние и низкий потенциал с его выхода поступает на управляющие входы первого 76 и второго 77 мультиплексоров разрешая передачу информации на выходы мультиплексоров с их первых информационных входов. Таким образом, информация из внешнего устройства, поступающая на информационный вход 22 устройства, транслируется на информационную шину 20 устройства, а управляющие сигналы из внешнего устройства, поступающие на управляющий вход 23 устройства, транслируются на управляющую шину 18 устройства. Информация и управляющие сигналы, сформированные в устройстве сопряжения для передачи внешнему устройству, при нулевом состоянии триггера 75 без изменения транслируются с информационной 19 и управляющей 17 шин устройства на информационный 25 и управляющий 24 выходы устройства.

Работа устройства для сопряжения в режиме Записать осуществляется следующим образом.

При дешифрации в инструкции ввода-вывода ; кода команды Записать в регистр 8 режимов по выходной информационной шине 1 процессора микропрограммно заносится признак команды Записать, поступающий на вход 26 режима в узел 15 фиксации режима работы. В узле фиксации режима работы при наличии этого сигнала, нулевом состоянии триггера 43 и отсутствии сигнала на управляющей шине 18 устройства появляется высокий потенциал на выходе элемента И 41 и устанавливается триггер 42, высокий потенциал которого является сигнальным выходом узла и по линии 30 поступает в узел 13 анализа управляющих сигналов, устанавливая высокий потенциал на выходе элемента ИЛИ 58 Этот сигнал поступает на информационный вход 32 формирователя 14 сигнала прерывания (фиг.5), где при отсутствии признака работы в режиме Сервис (низкий потенциал на входе элемента НЕ 67) и при наличии синхросигнала, поступающего по выходной шине 3 синхронизации процессора формирует высокий потенциал на выход элемента И 68, который устанавливает триггер 69. Сформированный запрос за микропрограммное прерывание поступает в блок микропрограммных прерываний процессора по входной шине 5 прерывания процессора. Дальнейшее выполнение режима Записать осуществляется под управлением микропрограммы, вызванной запросом на прерьшание, в процессе выполнения которой код вводимого знака с выходной информационной шины 1 процессора заносится в регистр 9 выходных данных. Запрос на микропрограммное прерывание снимается микропрограммно, для чего в регистре режимов устанавливается соответствующий признак, который сбрасьшает триггер 42 узла 15 фиксации режимов работы. При этом возникает низкий потенциал на выходе элемента ИЛИ 58 узла 13 анализа управляющих сигналов, который поступает в формирователь 14 сигнала прерьшания и сбрасывает триггер 69 запроса на микропрограммное прерывание. При занесении данных в регистр 9 выходных данных в узле 15 фиксации режима работы ycтaнaвJiИвaeтcя триггер 43, по единичному состоянию которого и нулевому состоянию триггера 42 устанавливается триггер 44. Из регистра 9 выходных данных код вводимого символа передается во внешнее устройство по информационной шине 19 на информационньш выход 25 устройства (триггер 75 находится в нулевом состоянии-). По сигналу Цикл, формируемому с помощью триггера 44 и вьщаваемому на управляющую шину 17 устройства и управляющий выход 24 устройства, внешнее устпойство принимает данные с информационной шины 19 (25). В ответ на сигнал Цикл внешнее устройство на управляющий вход 23, т.е. на управляющую шину 18 вьщает сигнал Обратная связь, который сбрасывает триггеры 43 и 44 в узле 15 фиксации режима работы. После снятия сигнала Цикл внешнее устройство снимает сигнал Обратная связь, что приводит к вьфаботке триггером 42 запроса на новое микропрограммное прерывание, в процессе обработки которого выводится на печать (или отображается на экране дисплея) следующий символ. Так происходит до тех пор, пока вся информация не будет передана.

Работа устройства в режиме Считать осуществляется следующим образом.

Микропрограммно устанавливается признак режима Считать в регистре 8 режимов. Регистр режимов выдает на управляющую шину 17 (и 24) устройства сигнал, которьй разрешает работу внешнего устройства в режиме Считать. Внешнее устройство выдает на информационный вход 22 устройства т.е. на информаиионную шину 20 байт информации, после чего на управляющи вход 23 устройства, т.е. на управляю щую шину 18 - сигнал Строб, которьй поступает в узел -15 фиксации режима работы. По сигналу Строб при наличии синхросигнала на выходной шине 3 синхронизации процессора и низком потенциале триггера 35 устанавливается триггер 38. При поступлении следуюш,его синхроимпульса по шине 3, высоком потенциале триггера 38, наличии высокого уровня на входе 25 режима на выходе элемента И 3 вырабатьгоается сигнал приема, по которому информация с информационной шины 20 устройства записывается в регистр 12 входных данных. Кроме то го, по сигналу приема устанавливается триггер 42, что вызьгоает выработку запроса на микропрограммное прерывание аналогично режиму Записать. При наличии сигнала Строб по сигналу приема устанавливается триггер 35, по высокому потенциалу которого при наличии синхроимпульса на шине 3 сбрасывается триггер 38. Микропрограмма, вызванная запросом, производит запись символа, введенного в регистр 12 входных дан ных, в заданную область оперативной памяти процессора. Для отображения вводимого символ (на пишущей машинке или экране дисп лея) содержимое регистра 12 входных данных через рабочую область процессора переписывается в регистр 9 выходных данных. Алгоритм вывода си вола в этом случае аналогичен алгоритму вьшода символа в режиме Записать с той разницей, что в этом случае в ответ на сигнал Цикл внешним устройством снимается сигнал Строб и выдается сигнал Обратная связь. Ввод и отображение каждого следующего символа осуществляется по вьш еописанному механизму причем запрос на новое микропрограм мное прерывание вьфабатывзется по сигналу Строб. Режим Сервис устанавливается по инициативе оператора и выполняет ся, если процессор находится в режим ручного управления. Режим Сервис позволяет изменить или отобразить состояние процессора (память, регистры и т.д.) и выполнить дополнительные операции по управлению системой (первоначальная загрузка программ, командный режим работы, останов по сравнению адресов и т.д.). Работа устройства для сопряжения в режиме Сервис осуществляется следующим образом. При нджатии клавищи Сервис на пульте управления системой на управляющий вход 23 устройства, т.е. на управляющую шину 18 устройства поступает сигнал, который в узле 13 анализа управляющих сигналов устанавливает триггер 52 при наличии высокого потенциала режима Ручная работа на выходной шине 3 синхронизации процессора. При отжатии клавиши Сервис устанавливается триггер 53, и при отсутствии в устройстве для сопряжения режимов Считать и Записать (разрешающий потенциал на- первом входе элемента И 54, поступающий по линии 27 из регистра 8 режимов на вькоде элемента И 54 появляется сигнал Запрос,, поступающий по входной шине Запрос 7 процессора в блок микропрограммных прерываний процессора. По сигналу Запрос в блоке микропрограммных прерываний процессора формируется адрес входа в микропрограмму, подуправлением которой осуществляется работа устройства связи в режиме Сервис. Кроме того, в блоке микропрограммных прерываний устанавливается признак работы устройства для сопряжения в режиме Сервис, который сбрасывается микропрограммно только после завершения операции, выполняемой в данном режиме после нажатия на пульте клавиши Окончить. Триггер 52 сбрасывается высоким потенциалом, сформированным элементом И 55 при наличии разрешающего сигнала на линии 27 из регистра 8 режимов, установленного микропрограммно, и наличии потенциала режима Сервис на выходной шине 3 синхронизации процессора. По сбросу триггера 52 сбрасывается триггер 53 и снимается сигнал Запрос. Следующий запрос на микропрограммное прерьшание может вьфабатываться при следующем нажатии клавиши Сервис после завершения выполнения одной операции как после так и до нажатия клавиши Окончить (т.е. до снятия признака режима Сервис в блоке микропрограммных прерываний процессора).

Работа в режиме Сервис осуществляется под управлением микропрограммы. Для выполнения определенной операции (например, отображения оперативной памяти процессора) оператор с клавиатуры вводит буквенно-цифровую мнемонику операции, которая обрабатывается устройством для сопряже|;ия в режиме Считать,. как описано выше, с той разницей, что в этом случае при микропрограммной установке режима Считать формирователем 14 сигнала прерывания не вырабаты-вается сигнал запроса на микропрограммное прерывание в процессор. Блокировка осуществляется сигналом режима Сервис, поступающим по выходпой шине 3 синхронизации процессора на вход элемента НЕ 67 (фиг.5). Вывод отображаемой информации (например, содержимого оперативной памяти) происходит в режиме Записать устанавливаемом микропрограммно и выполняемом аналогично вьш1еописанHONry с той разницей, что запрос на микропрограммное прерывание в формирователе 14 сигнала прерывания блокируется сигналом режима Сервис.

Дополнительные операции выполняются также в режиме Сервис. Ввод мнемоники, задающей выполнение той или иной операции, осуществляется с клавиатуры пульта оператора таким же образом, как и для любой операции в режиме Сервис.

После ввода мнемоники микропрограммно в регистр 10 признаков операций по выходной информационной шине 1 процессора заносится управляющая информация, соответствующая введенной мнемонике.

Регистр 10 признаков операций обеспечивает формирование потенциальных сигналов, которые по входной управляющей шине 4 процессора передаются в процессор для задания необходимых режимов функционирования процессора при вьтолнении дополнительных операций.

Если для выполнения дополнительных операций по управлению системой необходимы адреса (загрузка программ, останов по сравнению адресов установка адреса и команды), то адрес, введенный оператором вместе с мнемоникой, микропротраммно заносится с выходной информационной шины 1 процессора в регистр 11 хранения адресов при наличии разрешающег сигнала на линии 33 из регистра 10 признаков операций. Далее этот адрес по адресной шине 6 процессора поступает в процессор и используетс при выполнении операции.

Работа устройства в режиме Диагностика осуществляется следующим образом.

Для перевода устройства в режим диагностики необходимо триггер 75 установить в единичное состояние. Микропрограммно в регистр 9 выходны данных заносится определенный код (во), который по информационной шине 19 устройст;ва поступает в узел 2 имитации. Этот код дешифрируется элементом И 74, дешифратором 73 и поступает на второй информационный вход первого мультиплексора 76. В регистре 8 режимов микропрограммно устанавливается признак диагностики (соответствующий отсутствию режимов Считать и Записать, который по управляющей шине 17 устройства поступает на первые единичный и нулевой входы триггера 75. При наличии этого сигнала и дешифрации кода 130 установки режима диагностики тригге 75 устанавливается в единичное состояние, разрешающее работу первого мультиплексора 76 по второму информационному входу, т.е. передачу информации с информационной шины 19 устройства на информационную шину 20 устройства. Рассмотрим проверку регистра 9 выходныхданных и регистра 12 входных данных в режиме диагностики. Микропрограммно в регистр 9 выходных данных заносится любой к (например, АА), которьй, кроме того записывается в одном из рабочих регистров процессора. Затем информация из регистра 9 вькодных данных переписывается в другой рабочий регистр процессора, после чего информация в рабочих регистрах сравнивается. При сравнении осуществляется

переход к следующей проверке, при несравнении - переход к сообщению об ошибке. Аналогичнь м образом может быть проверен регистр 8 режимов

Для проверки регистра 12 входных данных в регистр 8 режимов микропрограммно заносится признак приема в регистр 12 входных данных, который по управляющей шине 17 устройства поступает на вход элемента И 78 и при наличии высокого потенциала на выходе триггера 75 формирует строб приема, который по линии 34 поступает на второй управляющий вход регистра 12 входньгх данных, разрешая занесение в него информации. В регистр выходных данных (уже проверенный) микропрограммно заносится любой код (например, 55), который, кроме того, записывается в одном из рабочих регистров процессора. Этот код из регистра 9 выходных данных по информационной шине 19 устройства поступает на второ информационный вход первого мультиплексора 76 и при единичном состоянии триггера 75 передается на информационную шину 20 устройства, а с нее (при наличии строба на линии 34) - в регистр 12 входных данных. Во второй рабочий регистр процессора переписывается информация, принятая в регистр 12 входных данных, после чего информация в рабочих регистрах процессора сравнивается. При сравнении осуществляется перехо к следующей проверке, при несравненни - переход к сообщению об ошибке Задавая различные коды (бегающий О, бегающая 1 и т.д.), можно с точностью до бита локализовать неисправность регистров.

Проверка схем управления устройства осуществляется следующим образом.

Каждому сигналу управления, поступающему по управляющей шине 18 устройства, соответствует определенный код (В2, ВЗ и т.д.) и сигнал управления из устройства сопряжения поступающий по управляющей шине 17 устройства (в некоторых случаях сигнал управления из внешнего устройства может имитироваться только кодом, например, сигнал Строб), Этот определенный код микропрограммно заносится в регистр 9 выходных данных, поступает на входную информационную шину 19 внешнего устройства и дешифрируется дешифратором 73. При наличии соответствующего сигнала управления на шине 17 и высоком потенциале на определенном выходе дешифратора 73 высокий потенциал появляется на выходе соответствующего из элементов И 70, 72 и т.д и втором информационном входе второго мультиплексора 77. Количество элементов И определяется числом сигналов управления из внешнего устройства, которые необходимо проверить (смоделировать). Высокий потенциал на управляющем входе второго мультиплексора (установлен режим диагностики) разрешает передачу информации с второго информационного входа мультиплексора на управляющую шину 18 устройства. Таким образом можно проимитировать любой сигнал управдения и проверить работу схем управления устройства.

Для примера рассмотрим проверку линии сигнала Строб, занесения в регистр 12 входных данных и сброса запроса на микропрограммное прерывание.

В регистр 9 выходных данных микропрограммно заносится код В4, соответствующий наличию на управляющей шине 18 устройства сигнала Строб. В регистр 8 режимов заносится признак режима Считать. При этом должен сформироваться запрос на микропрограммное прерьгоание (установится триггер 69, см. описание работы устройства в режиме Считать

В первом рабочем регистре процессора формируется константа, соответствующая ожидаемому результату во второй рабочий регистр процессора считьгоается реальное состояние схем управления, после чего содержимое регистров сравнивается.

Кроме того, по сигналу Строб должен сформироваться сигнал приема информации в регистр 12 входных данных (элемент И 39, см. описание работы в режиме Считать). По этому сигналу код В4, поступающий с информационной шины 19 через первый мультиплексор на информационную шину 20 должен занестись в регистр 12 входных данных. В первый рабочий регист процессора записывается константа В4, во второй рабочий регистр процессора переписывается информация

из регистра 12 входных данных, после этого информация в рабочих регистрах сравнивается.

Для проверки сброса запроса на микропрограммное прерывание в регистр 8 режимов заносится признак сброса запроса, который должен сбросить триггеры 42 и 69. В первом рабочем регистре процессора подготавливается константа, соответствующая сбросу запроса на прерывание, во второй рабочий регистр считывается реальное состояние схем управления, результаты сравниваются. Аналогичным образом могут быть проверены и други схемы устройства.

Для сброса режима диагностики служит специальный код (В1). Он г-1икропрограммно заносится в регистр выходных данных, поступает ло информационной шине в узел 21 имитации и дешифруется элементом И 74 и дешифратором 73. При наличии признака диагностики на управляющей шине 17 устройства и дешифрации кода В1 происходит сброс триггера 75 в нулевое состояние, которое разрешает работу первого и второго мультиплексоров по первым .информационным входам, как описано выше. Кроме того, тригге 75 может быть переведен в нулевое состояние по сбросу системы при включении электропитания.

Узел 13 анализа управляющих сигналов предназначен для приема и преобразования асинхронных управляющих сигналов, поступающих от вргешнего устройства, выдачи этой информации в процессор, а также для формирования запроса на микропрограммное прерывание в режиме Сервис.

Рассмотрим для примера работу узла анализа управляющих сигналов при нажатии клавишного переключателя Окончить. При нажатии клавиши , Окончить высокий потенциал появляется на управляющем входе 23 устройства, т.е. на управляющей шине 18 устройства (режим диагностики отсутствует), и устанавливает в единичное состояние триггер 46 при наличии разрещающего пот-енциала режимов Считать или Записать, поступающего с первой группы информационных выходов регистра 8 режимов по линии 27. При отжатии клавиши Окончить по единичному состоянию триггера 46 устанавливается триггер 47. Кроме

того, на синхровход триггера 47 подается разрешающий синхросигнал с выходной шины 3 синхронизации процессора для синхронизации вырабатываемых при нажатии клавиш сигналов с работой процессора. Высокий потенциал с выхода триггера 47 поступает на элемент ИЛИ 58 для выработки в формирователе 14 сигнала прерывания сигнала запроса на микропрограммное прерывание, поступающего в процессор по входной шине 5 прерывания процессора. Кроме того, высокий потенциал с выхода триггера 47 поступает на входную информационную шину 2 процессора, что дает возможность микропрограммно опросить состояние данного узла. Сбрасываются триггеры 46 и 47 сигналом из регистра 8 режимов при микропрограммной установке признака сброса. Остальные элементы схемы построены аналогично и работают подобным образом.

Узел контроля повышает надежность устройства связи, контролируя работу интерфейса на линии устройство для сопряжения - внешнее устройство Интерфейс организован таким образом, что-в ответ на сигнал Цикл, сопровождающий байт информации, внешнее устройство должно вьщать сигнал Обратная связь, по которому сбрасывается сигнал Цикл, а по снятию сигнала Цикл внешнее устройство снимает сигнал Обратная связь. Схема контроля предназначена для фиксации моментов зависания, т.е. когда в ответ на сигнал Цикл внешнее устройство не вьщает сигнал Обратная связь или вьщав, не снимает ее

Схема работает следующим образом

Из процессора по выходной шине 3 синхронизации поступают тактовые импульсы, период которых по крайней мере в два раза больше промежутка времени, в течение которого осуществляется нормальный прием байта информации внешним устройством с помощью сигналов Цикл и Обратная связь. По заднему фронту тактового импульса высокий потенциал появляется на выходе элемента НЕ 60 и на выходе элемента И 63. Сигнал Цикл, поступающий с входной управляющей шины 17 внешнего устройства, устанавливает высокий потенциал на выходе элемента ИЛИ 64, который устанавливает

в единичное состояние триггер 66, Если в ответ на сигнал Цикл абонент выдает сигнал Обратная связь цикл приема байта завершен нормально, то по снятий сигнала Обратная связь, поступающего по управляющей шине 18 устройства с входа 23, сбрасывается триггер 66. Если же сигналы Цикл или Обратная связь зависают, то триггер 66 остается в единичном состоянии. Тогда по переднему фронту следующего тактового импульса высокий потенциал появляется на выходах элементов И 62 и 65. Этот сигнал является признаком сбоя в работе интерфейса и по линии 31 поступает в узел 13 анализа управляющих сигналов, где устанавливает триггер 59. При этом с помощью элемента ИЛИ 58 вырабатьшается запрос на микропрограммное прерьгоание, в результате обработки которого указание о сбое становится доступным оператору.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С УСТРОЙСТВОМ ВВОДАВЫВОДА, содержащее регистры режимов, входных данных, выходных данных, признаков операций и хранения адресов, узел анализа управляющих сигналов, формирователь сигнала прерывания, узел фиксации режима работы, узел контроля, при этом информационные входы регистров режимов, выходных данных, признаков операций и хранения адресов подключены к выходной информационной шине процессора, информационные выходы регистра входных данных и узел анализа управляющих сигналов подключены к входной информационной шине процессора, группы синхровходов узла фиксации режима работы, узла анализа управляющих сигналов, синхровходы формирователя сигнала прерывания и узла контроля подключены к синхровходу процессора, первая группа выходов регистра признаков операций подключена к управляющей шине процессора, группа выходов регистра хранения адресов подключена к адресной шине процессора, выход запроса узла анализа управляющих сигналов подключен к входу запроса процессора, выход формирователя сигнала прерывания подключен к входу прерывания процессора, причем первая группа информационных выходов регистра режимов соединена с первой группой управляющих входов узла анализа управляющих сигналов, запускающий выход которого соединен с информационным входом формирователя сигнала прерывания, вторая группа информационных выходов регистра режимов соединена с группой входов режима узла фиксации режима работы, стробирующий ю выход которого соединен с первым управляющим входом регистра входных данных,., (Л выход управляющего разряда регистра выходных данных соединен с установочным входом узла фиксации режима работы, сигнальный выход которого соединен с входом запроса узла анализа управляющих сигналов, установочньш вход которого соединен с 00 выходом узла контроля, вторая групо па информационных выходов регистра ;0 признаков операций соединена с управляющим входом регистра хранения адресов, отличающееся тем, что, с целью повьш1ения достоверности путем организации микропрограммного диагностирования оборудования, в него введен узел ими тации сигналов, причем первый и второй входы узла имитации сигналов подключены к информационным и управляющим выходам устройства ввода-вывода соответственно, первый и второй, выходы узла имитации сигналов подключены к информационному и управляющему входам устройства ввода-вы

S

35

№

IB

S R

n

39

42

5

S 71

3

J(7

/7

Фиг. 2

65

и

Т

68

S R

66

/1

т

Регистр бы ладных данных

Рабочий регистр 1К

Рабочий pezucmp7i fгистру StDtafHin динMutS

Нет

Coofu tHOf off ршиУпгастр ренимсв Sifuналу приет 6 petaatf tmdma вонтг 12

Регистр doHMtit 9-HI

ЗоЯеркю mjoo p/Kia МО кинияк с1я1и

Pafowii регистр 1-111

PaSfv/v gfivcfnf Ifetvcmfy Siafiuf ва№ла P

| Патент США № 3889109, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-11—Подача