входами первого, первыми установочными входами второго, третьего,.четвертого, пятого, шестого,, седьмого, восьмого и девятого триггеров, выходная шина синхронизации процессора соединена с синхровходами третьего, пятого, седьмого, десятого триггеров, вторым установочным входом восьмого триггера и первым входом первого элемента И, третий разрядный выход регистра режимов соединен с вторым и третьим установочными входами второго и четвертого Триггеров, вторым установочным входом шестого триггера, первым и вторым установочными входами двенадцатого триггера, вторым входом первого и первым входом второго элементов И, первым входом элемента ИЛИ и первыми установочными входами десятого и одиннадцатого триггеров, сигнальный выход узла фиксации режима вьщача-прием и выход узла контроля соединены соответственно с вторым входом элемента ИЛИ и третьим установочным входом двенадцатого триггера, первые выходы первого и одиннадцатого триггеров соединены с вторым и третьим установочными входами десятого триггера, второй выход первого триггера соединен с вторым установочным входом одиннадцатого триггера, третий установочный вход которого и третий вход элемента ИЛИ соединены с выходом десятого тригге раувыход второго триггера соединен с вторым и третьим установочными вхо дами третьего триггера, выход которо го соединен с четвертым входом эле- мента ИЛИ, выходы четвертого и шесто го триггеров соединены с вторыми и третьими установочными входами соответственно пятого и седьмого триггеров, выходы которьк соединены с пятым и шестым входами элемента ИЛИ, выход двенадцатого триггера соединен с седьмым входом элемента ШЩ, выход восьмого триггера соединен с вторым , и третьим установочными входами девя того триггера, выход которого соединен с вторым входом второго элемента И, выход первого элемента И соединен с третьим установочным входом восьмого триггера, первый выход первого триггера, выходы третьего, пятого, седьмого, девятого, десятого и двенадцатого триггеров и выход эле мента ИЛИ соединены с входной информационной шиной процессора, выход 1 82 второго элемента и соединен с входной шиной Запрос процессора, выход элемента ИЛИ соединен с информационным входом формирователя сигнала прерывания, причем узел фиксации режима выдача-прием содержит пять триггеров, четьфе элемента И и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с входом синхронизации узла, второй вход третьего элемента И, первые входы четвертого элемента И и первого триггера соединены с входом режима узла, первый управляющий вход узла соединен с первым входом второго триггера, выход которого соединен с вторым входом четвертого элемента И и первым входом третьего триггера, выход которого является управляющим выходом узла, второй упра1шяющий вход узла соединен с первым и вторым входами четвертого триггера, вторым входом первого эле- . мента И, первым входом пятого триггера, вторым входом второго триггера, третьим входом четвертого элемента И и вторым и третьим входами третьего триггера, выход четвертого триггера соединен с третьим входом первого элемента И и вторым входом второго элемента И, выходы которых соединены с вторым и третьим входами пятого триггера, выход которого соединен с третьим входом третьего элемента И, четвертый вход которого соединен с выходом элемента ИЛИ, а выход - с третьим входом четвертого триггера, вторым входом первого триггера, первым входом элемента ИЛИ и является стробирующим выходом узла, третий вход первого триггера соединен с выходом четвертого элемента И, а выход - с вторым входом элемента ИЛИ, четвертым входом третьего триггера и является сигнальным выходом узла, при этом узел контроля содержит триггер, три элемента И, элемент ШШ, элемент НЕ и элемент задержки, причем первый и второй входы элемента ИЛИ являются первым и вторым входами узла, а выход соединен, с первым и вторым входами триггера, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом второго элемента И, а выход является выходом узла, третий вход узла соединен с первом входом второго элемента И, через элемент НЕ - с первым входом третьего элемента И, а через элемент за-

держки - с вторыми входами второго и третьего элементов И, выход третьего элемента И соединен с третьим входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С УСТРОЙСТВОМ ВВОДА-ВЫВОДА, содержащее формирователь сигнала прерывания, регистр.входных данных, регистр выходных данных, регистр режимов, причем входы регистра режимов и регистра выходных данных соединены с выходной информационной шиной процессора, выход формирователя сигнала прерывания соединен с входной шиной прерывания процессора, информационный вход регистра входных данных соединен с выходной информационной шиной внешнего устройства, а его выход - с входной информационной шиной процессора, разрядный выход регистра выходных данных и первый разрядньй выход регистра режимов соединены соответствеяно, с информационной и управляющей входными шинами внешнего устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет организации обмена по инициативе внешнего устройства и повьш1ения достоверности, в устройство введены ре,гистр признаков операций, регистр хранения адресов, узел фиксации режима вьщача-прием, узел контроля и узел анализа управляющих сигналов, причем информационные входы регистра признаков операций и регистра хранения адресов соединены с выходной информационной шиной процессо-. ра, управляющий вход регистра хранения адресов соединен с первым разрядным выходом регистра признаков операций, второй разрядный выход которого, и разрядный выход регистра хранения адресов соединены соответственно с входной управляющей и дополнительной информационной шинами процессора, входы режима, синхронизации и первый и второй управляющие входы узла фик сации режима выдача-прием соединены i соответственно с вторым разрядным выходом регистра режима, выходной О) шиной синхронизации процессо1)а, управляющим выходом регистра выходных данных и выходной упраьл.яющей шиной внешнего устройства, управлякнций вы. ход,узла фиксации режима ввдача-при- ем соединен с входной управляющей шиной внешнего устройства и первым входом узла контроля, второй и третий входы которого соединены соответственно с выходной управляющей шиной внешнего устройства и выходной шиной синхронизации процессора, стробирующий выход узла фиксации режима вьщача-прием соединен с .управляющим входом регистра входных данных, синхровход формирователя сигнала прерывания соединен с выходной шиной синхронизации процессора, при этом узел анализа управляющих сигналов содержит двенадцать .триггеров, два элемента И и элемент ИЛИ, причем выходная управляющая шина внешнего устройства соединена с первьы, вторым и третьим установочными

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессора с устройствами ввода-вывода, в том числе с устройствами, работающими в качестве пультов управления вычислительной системой. Известно устройство для подключения устройств ввода-вывода (в том числе и пультов- оператора) к процессору через универсальный канал ввода-вывода, содержащий управляющие и информационные шины процессора и абонента., регистр команд, буферные регистры, схему управления буфером, блок управления каналом m. Недостатками такого устройства яв ляются большой объем оборудования канала и сложность,алгоритмов взаимо действия с абонентом, обусловленные универсальностью канала, а также тем, что он рассчитан на подключение большого числа абонентов. Кроме того функциональные возможности канала ог раничены лишь вводом и выводом инфор мации. Для абонентов, подключаемых к такому каналу, характерно наличие из быточного оборудования. Наиболее близким к предлагаемому по технической сущности является уст ройство связи, имеющее узел формирования прерывания, регистр входных . данных, регистр выходных данных, регистр режимов, выходную управляющую шину абонента, входную управляющую шину абонента, выходную информахщонкую шину абонента, входную информаци онную шину абонента, шину Прерывание, выходную управляющую шину процессора входную информационную шину процессора, выходную информационную шину процессора, которая соединена с входом регистра режимов и входом регистра выходных данных, первый выход которого соединен с входной информационной шиной абонента, первый выход регистра режимов соединен с входной управляющей шиной абонента. первый вход и выход регистра входных данных соединены соответственно с выходной информационной шиной абонента и входной информационной шиной процессора, а выходная управляющая шина процессора соединена с первым входом узла формирования прерывания, выход которого соединен с шиной Прерывание {2j . Недостатком известного устройства является невозможность вьщачи в процессор прерывания по инициативе абонента. Прерывание вырабатывается только при наличии команды обмена для инициализации программы, обеспечивающей считывание и запись информации с абонента. Это не позволяет использовать известное устройство для подкйючения к ЭВМ активных абонентов, таких как пульты управления системой (пишущая машинка, дисплей). Известное устройство связи выполняет только операции ввода-вывода и не обеспечивает выполнение других операций (управление режимами работы процессора, управление программами .д.), что невозможно в связис отсутствием: в аппаратуре известного устройства : информационного и управляющего регистров дополнительных операций и шин выдачи их содержимого в процессор. Это также ограничивает возможности использования известного блока. Отсутствие контроля отработки абонентом команд устройства связи снижает контролепригодность известного устройст- , ва. Цель изобретения - расширение функциональных возможностей за счет организации обмена по инициативе внешнего устройства и довьш1ения достоверности, что обеспечит возможность подключения к процессору пульта управления системой. Поставленная цель достигается тем, что в устройство, содержащее формирователь сигнала прерывания, регистр входных данных, регистр выходных н-

ных, регистр режимов, причем входы регистра режимов и регистра выходных данных соединены с выходной информационной шиной процессора, выход формирователя сигнала прерывания соединен с входной шиной прерьгоания процессора, информационный вход регистра входных данных соединен с выходной информационной шиной внешнего устройства, а.его выход - с входной информационной шиной процессора, разряд- ньй выход регистра выходных данных и первьй разрядный выход регистра режимов соединены соответственно синформационной и управляющей входными шинами внешнего устройства, введены регистр признаков операций, регистр хранения адресов, узел фиксации режима вьщача-прием, узел контроля и узел анализа управляющих сигналов, причем информационные входы регистра признаков операций и регистра хранения адресов соединены с выходной ийформационной шиной процессора, управляющий вход регистра хранения адресов соедине с первым разрядным выходом регистра признаков операций, второй

разрядный выход которого и разрядный вькод регистра хранения адресов соединены соответственно с входной управляющей и дополнительной информационной шинами процессора, входы режима, синхронизации и первьй и второй управляющие входы узла фиксации режима выдача-прием соединены соответственно с вторым разрядным выходом регистра режима,выходной шиной синхронизации процессора, управляющим выходом регистра выходных данных и. выходной управляющей шиной внешнего устройства, управляющий выход узла фиксации режима вьщача-прием соединен с входной управляющей шиной внешнего устройства и первым входом узла контроля, второй и третий входы которого соединены соответственно с выходной управляющей шиной внешнего устройства и выходной шиной синхронизации процессора, стробирующий выход, узла фиксации режима вьщача-прием соединен с управлякяцим входом регистра входных данных, синхровход формирователя сигнала прерывания соединен с выходной шиной синхронизации процессора, при этом узел анализа управляющих сигналов содержит двенадцать триггеров, два элемента И и элемент ИЛИ, причем выходная управляющая шина внешнего устройства соединена с первым, вторьи

третьим установочньми входами первого, первыми установочными входами второго, третьего, четвертого, пятого, естого,седьмого, восьмого и девятого

триггеров, выходная шина синхронизации процессора соединена с синхровхоами третьего, пятого, седьмого, есятого триггеров, вторым установочным входом восьмого триггера и первым

входом первого элемента И, третий разрядньй выход регистра режимов соеинен с вторым и третьим установочными входами второго и четвертого триггеров, вторым установочным входом

шестого триггера, первым и вторым установочными входами двенадцатого триггера, вторым входом первого и первым входом второго элементов И, первым входом элемента ИЛИ и первыми

установочными входами десятого и одиннадцатого триггеров, сигнальньй выход узла фиксации режима вьщачаприем и выход узла контроля соединены соответственно с вторым входом

элемента ИЛИ и третьим установочным входом двенадцатого триггера, первые выходы первого.и одиннадцатого триггеров соединены с вторым и третьим установочными входами десятого триггера, второй выход первого триггера соединен с вторым установочным входом одиннадцатого триггера, третий установочный вход которого и третий вход элемента ИЛИ соединены с выходом десятого триггера, выход второго триггера соединен с вторым и третьим ус- тановочными входами третьего триггера, выход которого соединен с четвертым ВХОД9М элемента ИЛИ, выходы четвертого и шестого триггеров соединены с вторыми и третьими установочными входами соответственно пятого и седьмого триггеров, выходы которых соединены с пять1М и шестым входами

элемента ИЛИ, выход двенадцатого триггера соединен с седьмым входом элемента ИЛИ, выход восьмого триггера соединен с вторым и третьим установочными входами девятого триггера,

выход которого соединен с вторым входом второго элемента И, выход первого элемента И соединен с третьим установочным входом восьмого триггера, первьй выход первого триггера, выходы третьего, пятого, седьмого, девятого,

десятого,и двенадцатого триггеров и выход элемента ИЛИ соединены с входной информационной шиной процессора, выход второго элемента И соединен

с входной шиной Запрос процессора, выход элемента ИЛИ соединен с информационным входом формирователя сигнала прерьшания, причем узел фиксации режимавыдача-прием содержит пять триггеров, четыре элемента И и элемент ИЛИ, причем первые входы первого второго и третьего элементов И соединены с входом синхронизации узла второй вход третьего элемента И, первые входы .четвертого элемента И и первого триггера соединены -с входом режима узла, первый управляющий вход узла соединен с первым входом второго триггера, выход которого соединен с вторым входом четвертого элемента И и первым входом третьего триггера, выход которого является управляющим выходом узла,второй управляющий вход узла соединен с первым и вторым входами, четвертого триггера, вторым входом первого элемента И, первым входом пятого триггера, вторым входом второго триггера, третьим входом четвертого элемента И и вторым и третьим входами третьего триггера, выход четвертого триггера соединен с третьим входом первого элемента И и вторым входом второго элемента И, выходы которых соединены с вторым и третьим входами пятого триггера, выход которого соединен с третьим входом третьего элемента И, четвертый вход которого соединен с выходом элемента ИЛИ, а выход - с третьим входом четвертого триггера, вторым входом первого триггера, первым входом элемента ИЛИ и является стробирующим выходом узла, третий вход первого триггера соединен с выходом четвертого элемента И, а выход - с вторым входом элемента ИЛИ, четвертым входом третьего триггера и является .сигнальным выходом узла, при этом узел контроля содержит триггер, три

элемента И, элемент ИЛИ, элемент НЕ 1

и элемент задержки, прИчем первый и второй входы элемента ИЛИ являются первым и вторым входами узла, а выход соединен с первым и вторым входами триггера, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом второго элемента И, а выход является выходом узла, третий вход узла соединен с первым входом второго элемента И, через элемент НЕ - с первым входом третьего элемента И, а через

элемент задержки - с вторыми входами второго и третьего элементов И, выход третьего элемента И соединен с третьим входом триггера.

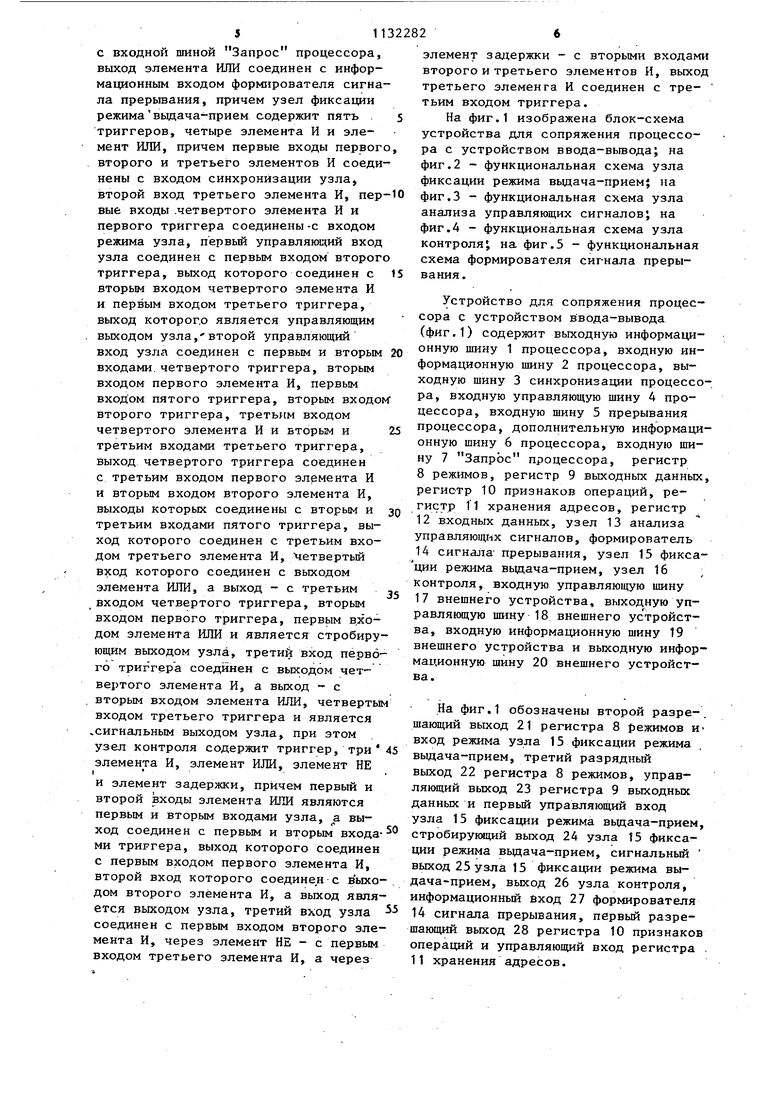

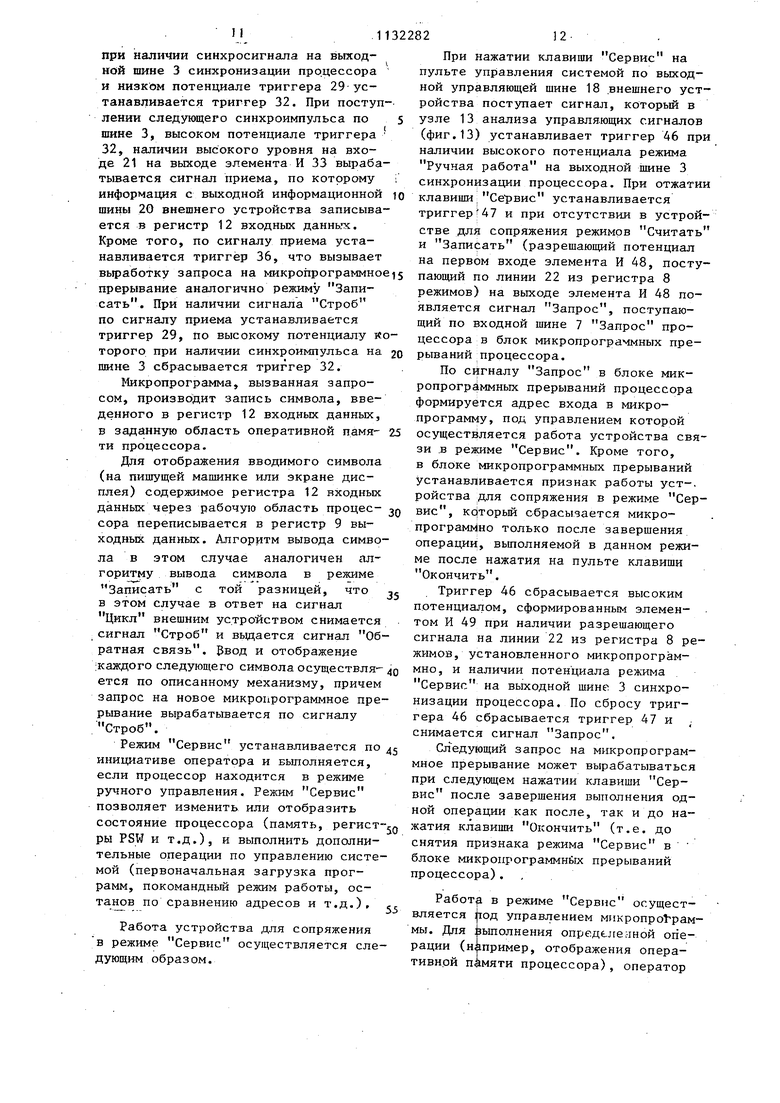

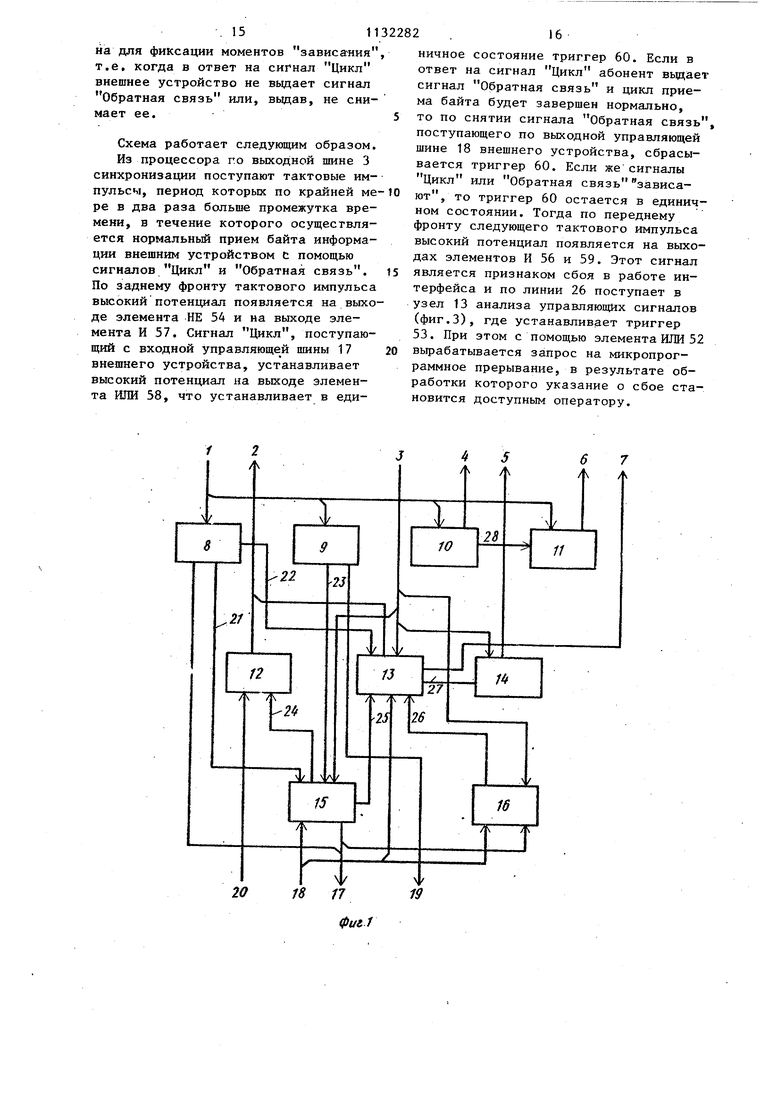

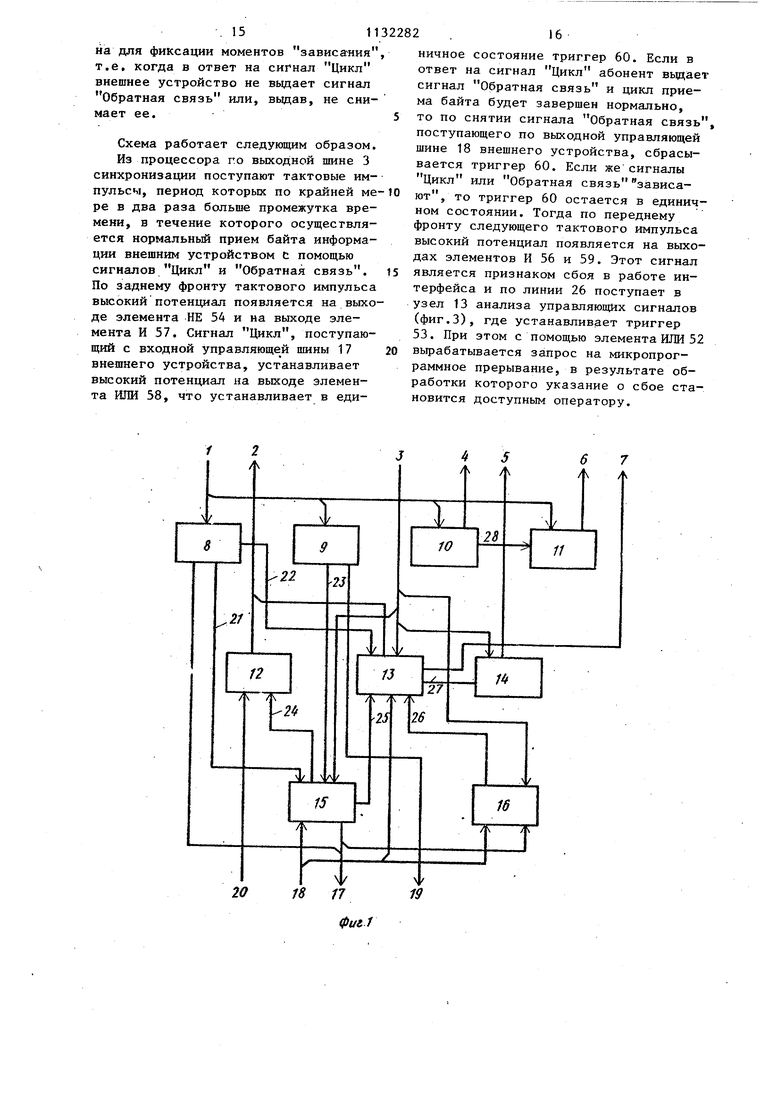

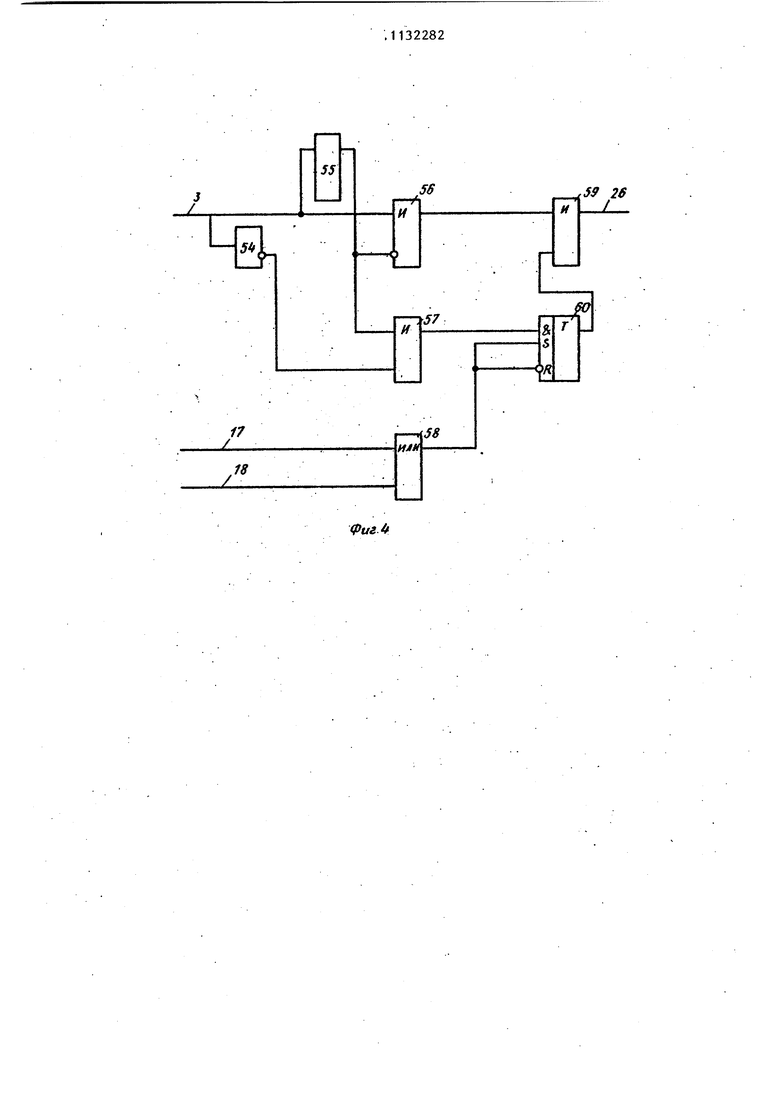

На фиг.1 изображена блок-схема устройства для сопряжения процессора с устройством ввода-вьгоода; на фиг.2 - функциональная схема узла фиксации режима выдача-прием; на фиг.З - функциональная схема узла анализа управляющих сигналов; на фиг.4 - функциональная схема узла контроляi на фиг.5 - функциональная схема формирователя сигнала прерывания.

Устройство для сопряжения процессора с устройством ввода-вывода (фиг.1) содержит выходную информационную шину 1 процессора, входную информационную шину 2 процессора, выходную шину 3 синхронизации процессора, входную управляющую шину 4 процессора, входную шину 5 прерывания процессора, дополнительную информационную шину 6 процессора, входную шину 7 Запрос процессора, регистр 8 режимов, регистр 9 выходных данных регистр 10 признаков операций, регистр 11 хранения адресов, регистр 12 входных данных, узел 13 анализа управляющих сигналов, формирователь 14 сигнала- прерывания, узел 15 фиксации режима вьщача-прием, узел 16 контроля, входную управляющую шину 17 внешнего устройства, выходную управляющую шину 18 внешнего устройства, входную информационную шину 19 внешнего устройства и выходную информационную шину 20 внешнего устройства.

На фиг.1 обозначены второй разрешающий выход 21 регистра 8 режимов ивход режима узла 15 фиксации режима вьщача-прием, третий разрядный выход 22 регистра 8 режимов, управляющий выход 23 регистра 9 выходных данных и первый управляющий вход узла 15 фиксации режима вьщача-прием стробирующий выход 24 узла 15 фиксации режима вьщача-прием, сигнальный выход 25 узла 15 фиксащти режима выдача-прием, выход 26 узла контроля, информационный вход 27 формирователя 14 сигнала прерывания, первый разрешающий выход 28 регистра 10 признако операций и управляющий вход регистра 11 хранения адресов. Узел фиксации режима вьщача-прием (фиг.2) содержит четвертый триггер 29, первый элемент И 30, второй элемент И 31, пятьй триггер 32, третий элемент И 33, элемент ИЛИ 34, четвер тый эл.емент И 35, первый триггер 36, второй триггер 37, третий триггер 38 Узел анализа управляющих сигналов (фиг.З) содержит первьй триггер 39, второй триггер 40, третий триггер 41 четвертьй триггер 42, пятый триггер 43, шестой триггер 44, седьмой триггер 45, восьмой триггер 46, девятый триггер 47, второй элемент И 48, первый элемент И 49, одиннадцатый триггер 50, десятьш триггер 51, элемент ИЛИ 52, двенадцатьй триггер 53. Узел контроля (фиг.4) содержит элемент НЕ 54, элемент 55 задержки, второй элемент И 56, третий элемент И 57, элемент ИЛИ 58, первьй элемент И 59, триггер 60. Формирователь сигнала прерывания (фиг.5) содержит элемент НЕ 61, элемент И 62,триггер 63. Выходная информационная шина 1 процессора предназначена для выдачи управляющей информации в регистр режимов и регистр признаков операций, а также для 1вьцз;ачи байта данных в регистр выходных данных и в регистр крайения адресов. Занесение информации с выходной информационной шины процессора производится микропрограммно , . Входная информационная шина 2 про цессора служит для. передачи байта ин формации от внешнего устройства (пульта управления системой) продёссору. Выходная шина 3 синхронизации про цессора предназначена дл.я выдачи управляющих сигналов в узел анализа управляющих сигналов, узел контроля, узел организации.обмена и формирова:тель сигнала прерыва1щя. ( Входная управляющая шина 4 процес сора служит для передачи процессору сигналов управления дополнительными операциями. Входная шина 5 прерывания процессора служит для выдачи в процессор запросов на микропрограммное прерывание. Запрос инициирует микропрог. paMNJHoe выполнение передачи данных в режимах Считать и Записать, Дополнительная информационная шина 6 процессора служит для передачи 828 в процессор адресов оперативной памяти и устройств загрузки при выполнении допблнительных операций. Входная шина 7 - Запрос процессора предназначена для вьщачи в блок микропрограммных прерываний процессеР« сигнала, по которому инициируется микропрограммное вьтолнение дополнительных операций (операций управления системой) и операций изменения и отображения состояний процессора. Регистр 8 режимов является однобайтным и служит для задания режимов работы устройства для сопряжения. Регистр 9 выходных данных также является однобайтным и используется для передачи информации внешнему устройству (пульту управления). Регистр 10 признаков операций двухбайтньй, он предназначен для хранения признаков вьтолняемых дополнительных операций. Регистр 11 хранения адресов является четырехбайтным, предназначен для хранения адресов (памяти или устройства загрузки), необходимых для вьшолнения некоторых операций управления вычислительной системой (срав-t нение адресов, первоначальная загрузка и т.д.). Регистр 12 входных данных представляет собой однобайтный регистр, использующийся для ввода информации из внешнего устройства в процессор. Информация в регистры 9-12 заносится микропрограммно. Узел 13 анализа управляющих сигналов связан с управляющими клавишными переключателями и индикаторами внешнего устройства. Триггеры узла анализа управляющих сигналов имеют собственные установочные и сбросовые линии. Кроме того, в узле 13 анализа управляющих сигналов формируется сигнал Запрос. Формирователь 14 сигнала прерывания вырабатывает запрос устройства для сопряжения на микропрограммное прерывание. Узел 15 фиксации режима выдачаприем предназначен для организации ввода байта информации внешнего устройства в регистр 2 входных данных и для организации вывода передаваемого байта информации из регистра 9 выходных данных внешнему устройству. Узел 16 контроля предназначен для контроля интерфейса на линии внешнее устройство - устройство для сопряже9113ния. Признак сбоя устанавливается при отсутствии в течение 260 мкс ответа внешнего устройства на сигнал, Сопровождающий байт передаваемой информацич. Устройство .для сопряжения процессора с устройством ввода-вьшода работает в трех режимах: ввод информации; вывод информации; изменение и отображение состояний процессора. В режиме изменения и отображения вьшолняются, кроме того, дополнитель.ные функции управления сист-емой. Дпя реализации указанных режимов устройство связи обеспечивает работу аппара туру в режимах Считать, Записать, Сервис. Работа устройства для сопряжения в режиме Записать осуществляется следующим образом. При дешифрации в инструкции вводавывода кода команды Записать в регистр 8 режимов (фиг.1) по выходной информационной шине 1 процессора микропрограммно заносится признак команды Записать, поступающий на вход 2 режима в узел 15 фиксации режима выдача-прием. В узле 15 фиг.2) при налйч1Ш этого сигнала,нулевом состоянии триггера 37 и отсутствии сигнала на выходной управляющей шине 18 внешнего устройства, появляется высокий потенциал на выходе элемента И 35 и устанавливает триггер 36, высокий потенциал которого является сигнальным выходом узла и по линии 25 поСтупает в узел 13 анализа управляющих сигналов (фиг.З), устанавливая высокий потенциал на выходе элёмен- . та ИЛИ 52. Этот сигнал поступает на информационный вход 27 формирователя f 4 сигнала прерывания (фиг.5), где при; отсутствии признак работы в режиме Сервис (низкий потенциал на входе .элемента НЕ 61) и при наличии .. сиЙхросигнала, поступающего по выходндйшине 3 синхронизациипроцессора, формирует высокий потенциал на выходе элемента И 62, который устанавливает триггер 63. Сформированный запрос за микропрограммное прерывание поступает в блок микропрограммных прерываний процессора по входной шине 5 прерывания процессора. Дальнейшее выполнение режима Записать осуществляется под . управлением микропрограммы., вызванной запросом на прерывание, в процессе выполнения которой код вводимого знака с выходной информационной шины t : 2 10 процессора заносится в регистр 9 выходных данных. Запрос на микропрограммное прерывание снимается микропрограммно, для чего в регистре режимов устанавливается соответствующий признак, который сбрасывает триггер 36 узла 15. При этом возника-ет низкий потенциал на выходе элемента ИЛИ 52 узла 13 анализа управляющих сигналов (фиг.З), который поступает в формирователь 14 сигнала . прерывания (фиг.5) и сбрасывает триггер 63 запроса на микропрограммное прерывание. При занесении данньк в регистр 9 выходных данных в узле 15 фиксации режима вьщача-прием устанавливается триггер 37, по единичному состоянию которого и нулевому состоянию триггера 36 устанавливается триггер 38. Из регистра 9 выходных данньк код выводимого символа передается во внешнее устройство по входной информационной шине 19. По сигналу Цикл, формируемому .с помощью триггера 38 и вьщаваемому на входную управляющую шину 17 внешнего устройства, внешнее устройство принимает данные с входной информационной шины 19. В ответ на сигнал Цикл .внешнее устройство по управляющей Ш1ше 18 вьвдает сигнал Обратная связь, который сбрасывает . триггеры 37 и 38 в узле 15. После снятия сигнала Цикл внешнее устрой-, ство снимает сигнал Обратная связь, что приводит к выработке триггером 36 запроса на новое микропрограммное прерывание, в процессе обработки которого выводится на печать (или отображается на экране дисплея) следующий символ. Так происходит до тех пор, пока вся информация не будет передана. Работа устройства в реяшме- Считать осуществляется следующим образом. V Микропрограммно устанавливается признак режима Считать в регистре 8 режимов. Регистр режимов выдает на входную управляющую шину 17 внешнего устройства сигнал,, который разрешает работу внешнего устройства в режиме Считать. Внешнее устройство выдает на входную информационную шину 20 байт информации, после чего на выходнз- ю управляющую шину 18 выдает сигнал Строб, который поступает в узел 15 (фиг.2). По сигналу Строб при наличии синхросигнала на выходной шине 3 синхронизации про.цессора и низком потенциале триггера 29 устанавливается триггер 32. При поступ лении следующего синхроимпульса по шине 3, высоком потенциале триггера 32, наличии высокого уровня на входе 21 на выходе элемента И 33 вырабатывается сигнал приема, по которому информация с выходной информационной шины 20 внешнего устройства записыва ется в регистр 12 входных данных. Кроме того, по сигналу приема устанавливается триггер 36, что вызывает вьфаботку запроса на микропрограммно прерывание аналогично режиму Записать. При наличии сигнала Строб по сигналу приема устанавливается триггер 29, по высокому потенциалу к торого при наличии синхроимпульса на шине 3 сбрасывается триггер 32. Микропрограмма, вызванная запросом, производит запись символа, введенного в регистр 12 входных данных, в заданную область оперативной памяти процессора. Для отображения вводимого символа (на пишущей машинке или экране дисплея) содержимое регистра 12 входных данных через рабочую область процессора переписывается в регистр 9 выходных данных. Алгоритм вывода симво ла в этом случае аналогичен алгоритму вывода символа в режиме Записать с той разницей, что в этом случае в ответ на сигнал Цикл внешним устройством снимается сигнал Строб и вьщается сигнал Об ратная связь. Ввод и отображение :каждого следующего символа осуществля ется по описанному механизму, причем запрос на новое микропрограммное пре рывание вырабатывается по сигналу Строб. Режим Сервис устанавливается по инициативе оператора и вьшолняется, если процессор находится в режиме ручного управления. Режим Сервис позволяет изменить или отобразить состояние процессора (память, регист ры PSW и т.д.), и выполнить дополнительные операции по управлению систе мой (первоначальная загрузка программ, покомандньй режим работы, останов по сравнению адресов и т.д.). Работа устройства для сопряжения в режиме Сервис осуществляется сле дующим образом. .1 212 При нажатии клавиши Сервис на пульте управления системой по выходной управляющей шине 18 внешнего устройства поступает сигнал, который в узле 13 анализа управляющих сигналов (фиг.13) устанавливает триггер 46 при наличии высокого потенциала режима Ручная работа на выходной шине 3 синхронизации процессора. При отжатии клавиши Сервис устанавливается триггер47 и при отсутствии в устройстве для сопряжения режимов Считать и Записать (разрешающий потенциал на первом входе элемента И 48, поступающий по линии 22 из регистра 8 режимов) на выходе элемента И 48 появляется сигнал Запрос, поступающий по входной шине 7 Запрос процессора в блок микропрограммных прерываний процессора. По сигналу Запрос в блоке микропрограммных прерываний процессора формируется адрес входа в микропрограмму, под управлением которой осуществляется работа устройства связи .в режиме Сервис. Кроме того, в блоке микропрограммных прерываний устанавливается признак работы уст-, ройства для сопряжения в режиме Сервис, кс торьй сбрасызается микропрограммно только после завершения операции, выполняемой в данном режиме после нажатия на пульте клавиши Окончить. Триггер 46 сбрасывается высоким потенциалом, сформированным элементом И 49 при наличии разрешающего сигнала на линии 22 из регистра 8 режимов, установленного микропрограммно, и наличии потенциала режима Сервис на выходной шине 3 синхронизации процессора. По сбросу триггера 46 сбрасывается триггер 47 и снимается сигнал Запрос. Следующий запрос на микропрограммное прерывание может вырабатываться при следующем нажатии клавиши Сервис после завершения выполнения одной операции как после, так и до нажатия клавиши Окончить (т.е. до снятия признака режима Сервис в блоке микропрограммньгх прерываний процессора). , Работу в режиме Сервис осуществляется тод управлением микропро раммы. Для ;зьтолнения опредигелной операции (например, отображения оперативной памяти процессора), оператор 1311 с клавиатуры вводит буквенно-цифровую мнемонику операции, которая обрабаты вается устройством для сопряжения в режиме Считать описанным образом, с той разницей, что в этом случае при микропрограммной установке режим Считать формирователем 14 сигнала прерываний не вырабатывается сигнал запроса на микропрограммное прерывание в процессор. Блокировка осуществляется сигналом режима Сервис, по ступающим по выходной шине -3 синхронизации процессора на вход элемента НЕ 61 (фиг.5). Вывод отображаемой информации (например, содержимого оперативной памяти) происходит в режиме Записать, устанавливаемом мик ропрограммно и вьшолняемом описанным образом с той разницей что запрос н микропрограммное прерывание в формирователе 14 сигнала прерывания блоки руется сигналом режима Сервис. Дополнительные операции вьшолняются также в режиме Сервис. Ввод мнемоники, задающей вьшолнение той или иной операции, осуществляется с клавиатуры пульта оператора таким же образом, как и для любой другой операции в режиме Сервис. После ввода мнемоники микропрограммно в регистр 10 признаков операций (фиг..1) по выходной информационной шине t процессора заносится управляющая информация, соответствующа введенной мнемонике. . Регистр tO признаков операций обеспечивает формирование потенциаль ных сигналов, которые по входной управляющей шине 4 передаются в процес сор для задания необходимых режимов функционирования процессора при выполнении дополнительных операций. Если для вьшолнёния дополнительны огГёраций по управлению системой необходимы адреса (загрузка программ, останов по сравнению адресов, установка адреса команды), то адрес, вве денный оператором вместе с мнемоникой, микропрограммно заносится с выходной информационной шины 1 процессора в регистр 11 хранения адресов при наличии разрешающего сигнала на линии 28 из регистра 10 признаков опера1щи. Далее этот адрес по дополнительной информационной шине 6 поступает в процессор и используется при выполнении операции. 2 Узел 13 анализа управляющих сигналов (фиг.З) предназначен для приема и преобразования асинхронных управляющих сигналов, поступаюпщх от внешнего устройства для выдачи этой информации в процессор, а также для формирования запроса на микропрограммное прерывание в режиме Сервис. Рассмотрим для примера работу узла анализа управляющих сигналов при нажатии клавишного переключателя Окончить. При нажатии клавиши Окончить высокий потенциал появляется на выходной управляющей шине 18 внешнего устройства и устанавливает в единичное состояние триггер 40 при-наличии разрешающего потенциала режимов Считать или Записать, поступающего с третьего разрешающего вькода регистра 8 режимов по линии 22. При отжатии клавиши Окончить по единичному состоянию триггера 40 устанавливается триггер 41. Кроме того, на синхровход триггера 41 подается разрешающий синхросигнал с выходной шины 3 синхронизации процессора для синхронизации вьфабатываемых при нажатии клавиш сигналов с работой процессора. Высокий потенциал с выхода триггера 41 поступает на зле-т мент IfflH 52 для вьфаботки в формирователе 14 сигнала прерывания сигнала запроса на микропрограммное прерывание, поступающего в процессор по входной шине 5 прерывания процессора. Кроме того, высокий потенциал с выхода триггера 41 поступает на входную информационную шину 2 процессора, что дает возможность микропрограммно опросить состояние данного узла. Сбрасываются триггеры 40 и 41 сигналом из регистра 8 режимов при микропрограммной установке признака сброса. Остальные элементы схемы по роены и работают аналогично. Узел контроля (фиг.4) повьшгает надежность устройства связи. Контролируя работу интерфейса на линии устройство для сопряжения - внешнее устройство. Интерфейс организован таким образом, что-в ответ на сигнал Цикл, сопровождающий байт информации, внешнее устройство должно вьщать сигнал Обратная связь, по которому сбрасывается сигнал Цикл, а по снятию сигнала Цикл внешнее устройство снимает сигнал Обратная связь. Схема контроля предназначена для фиксации моментов зависа ния т.е. когда в ответ на сигнал Цикл внешнее устройство не вьщает сигнал Обратная связь или, вьщав, не снимает ее.

Схема работает следующим образом.

Из процессора по выходной шине 3 синхронизации поступают тактовые импульсы, период которых по крайней ме ре в два раза больше промежутка времени, в течение которого осуществляется нормальный прием байта информации внешним устройством с помощью сигналов Цикл и Обратная связь. По заднему фронту тактового импульса высокий потенциал появляется на выходе элемента НЕ 54 и на выходе элемента И 57. Сигнал Цикл, поступающий с входной управляюще й шины 17 внешнего устройства, устанавливает высокий потенциал на выходе элемента ИЛИ 58, что устанавливает в единичное состояние триггер 60. Если в ответ на сигнал Цикл абонент вьвдает сигнал Обратная связь и цикл приема байта будет завершен нормально, то по снятии сигнала Обратная связь поступающего по выходной управляющей шине 18 внешнего устройства, сбрасывается триггер 60. Если же сигналы Цикл или Обратная связь зависают, то триггер 60 остается в единичном состоянии. Тогда по переднему фронту следующего тактового импульса высокий потенциал появляется на выходах элементов И 56 и 59. Этот сигнал является признаком сбоя в работе интерфейса и по линии 26 поступает в узел 13 анализа управляющих сигналов (фиг.З), где устанавливает триггер 53. При этом с помощью элемента ИЛИ 52 вырабатывается запрос на микропрограммное прерывание, в результате обработки которого указание о сбое становится доступным оператору.

фиг. 2

1132282

/

1

6f

Н

и

63 J

.62

фиг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Двухтактный двигатель внутреннего горения | 1924 |

|

SU1966A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3805245, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-12-30—Публикация

1982-07-08—Подача