первый и второй ключи соответственно к источнику опорного напряжения и к шине нулевого потенциала, второй вход дифференциального Усилителя подключен к первым выводам третьего и четвертого масштабных .резисторов, вторые выводы которых подключены соответственно к исто 1нику опорного напряжения и через третий Ключ к шине нулевого потенциала, а также три элемента И и два элемента ИЛИ-НЕ.

Недостатком прототипа является невысокая точность.

Целью изобретения является повшоение точности работы умножителя.

Поставленная цель достигается тем, что в предлагаемый умножитель 1:ийротно-модулированных сигналов введен RS-триггер, кодо-ртправляемый блок задержки, параллельный регистр суммирующий счетчик, геневатор счетных импульсов, блок сложения по мо дулю два, первый вход которого подключен к второму входу элемента ИЛИ-НЕ к S-входу RS-триггера, к первому информационному Ьходу кодоуправляемого блока задержки и к выходу умножителя, второй вход блока сложения по модулю два подключен к первому входу устройства, R-входу RS ригггера и к второму информационному входу кодо-управляемого блока задержки, выход блока сложения по модулю два подключен к первому входу элемента И, к второму входу которого подключен выход генератора счетных импульдов, выход элемента И подключен к суммирующему входу суммирующего счетчика, выход элемента ИЛИ-НЁ подключен к установочному входу суфлирующего счетчика и к входу синхронизации параллельного регистра соответственно, информационные входы параллельного регистра подключены к информационным выходам суммирующего счетчика и к выходам RS-триггера, информационные выходы параллельного регистра подключены к управляющим входам кодо-управляемого .блока задержки, выходы, которого подключены к управляющим входам первого и второго ключей, управляющий вход третьего ключа является вторым входом умножителя.

Сущность изобретения состоит в снижении методичесой погрешности умножителя за счет обеспечения отно-сительного фазового сдвига 0ц, за- , висящего от текущих значений ШИМ-сигналов 4

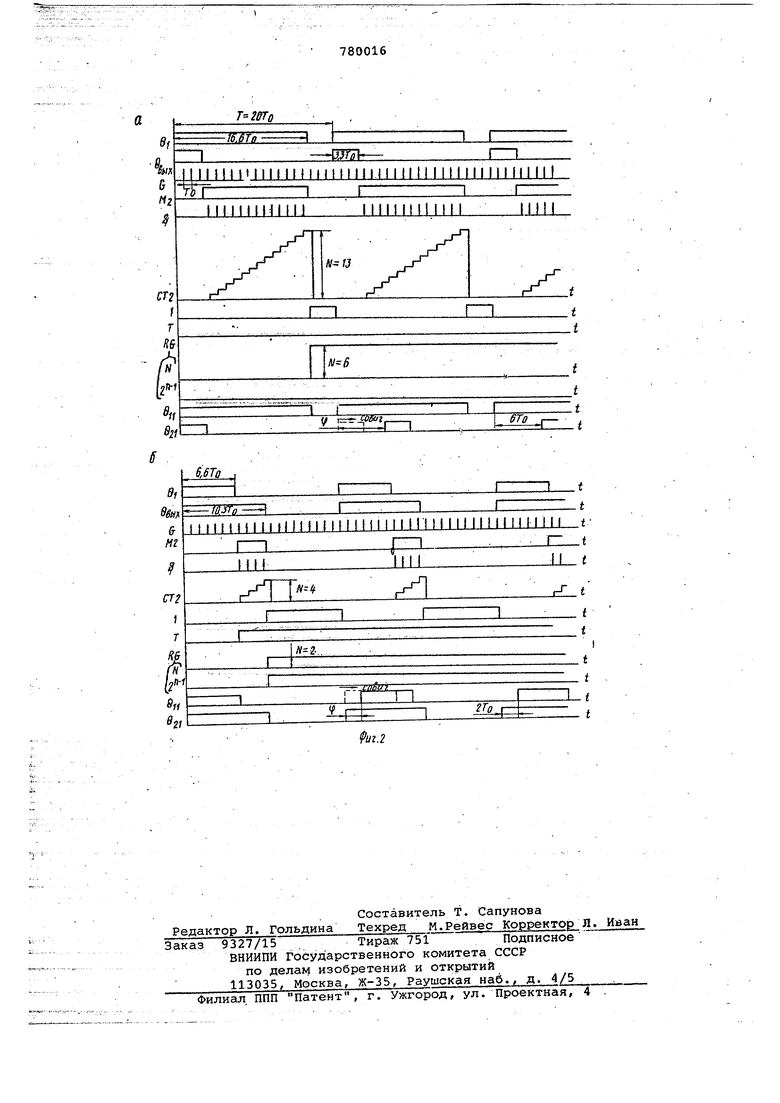

Функциональная схема предлагаемого умножителя 1чиротно-модулированных сигналов показана на фиг. 1; временная диаграмма работы цифровой части cxeNttJ приведена на фиг. 2.

Умножитель широтно-модулйрованных сигналов содержит дифференциальный . усилитель 1 и широтно-импульсный .

модулятор 2, элемент ИЛИ-НЕ 3, первый вход каторого является первым входом 4 умножителя, элемент И 5, кодо-управляемый блок 6 задержки, параллельный регистр 7, суммирующий счетчик 8, генератор 9 счетных .импульсов, блок 10 сложения по модулю два, первый ключ 11, первый масштабный резистор 12 и второй масштабный резистор 13, второй 14 и третий 15 КЛ10ЧИ, третий 16 и четвертый 17 масштабные резисторы, сглаживающие конденсаторы 18 и 19, источник 20 опорного напряжения, выход 21 умножителя, второй вход 22 умножителя, триггер 23.

Управляющие входа двух ключей 11 14 подключены к соответствующим выходам кодо-управяяемого элемента задержки.

Первый и второй входы схемы ИЛИНЕ 3 подключены соответственно к входам блока 10 Сложения по модулю два, к R- и S-входам триггера 23 и к информационньлм входам кодо-управляемого блока 6 задержки.

Выход схемы ИЛИ-НЕ подк:лючён к установочному R-входу с задержкой счетчика 8 и к входу синхронизации регистра 7. Выходы генератора 9 счетных импульсов и лока 10 сложения по модулю два подключены к элементу И 5, выход которого подключен к суммирующему входу счетчика 8. Информационный кодовый выход счетчи,ка 8 со сдвигом на один разряд подключен к информационному кодовому входу регистра 7, подключенного последним разрядом к выходам триггера 23.

Устройство работает следующим образом.. .

Пусть в начальный момент времени триггер 23, счетчик 8 и регистр 7 находятся в нулевом состоянии. На входы 4 и 22 умножителя поступают синхронные и синфазные ШИМ-сигнаЛы с некоторыми относительными длительностями & и &2 . Входной ШИМ-сигнал с относительной длительностью &2 управляет линейной импульсно-управляемой проводимостью, которая состоит из последовательно соединенного ключа 15 и.масштабного резистора 16. Двумя другими линейными импульсно-управляемыми проводимостями, содержащими ключ 11, резистор 12 и ключ 14, резистор 13, управляют ШИМ-сигналы с относительными длительностями в и которые поступают с вы содов кодо-управляемого блока б задержки. Эти относительные, длительности равны соответственно относительным длительностям в и в так как коДо-управляемый блок б за- держки осуществляет только задержку ШИМ-сигналов согласно управляющему коду , При достаточно большой емкости конденсаторов 18 и 19 обеспечиваетс развязка плеч моста, по переменному току, что дает возможность считать средние значения линейных импульсно-управляемых проводимостей пропс эциональными относительным длительностям управляющих ШИМ-сигналов Тогда изменение длительностей управляющих ШИМ-сигналов в и & приво дит к пропорциональному изменению проводимостей первого (ключ 11 , резистор 12) и третьего (ключ 15, , резистор 16) плеч моста, что вызывает изменение потенциалов по постоянному току на входах дифференциального усилителя 1, к которым подключены сглаживающие конденсаторы 18 и 19. Дифференциальный операционный усилитель 1 постоянного тока, включенный в одну диагональ моста, выделяет и усиливает разность потенцисшов на этих конденсаторах. В другую диагональ моста включен источник 20 опорного напряжения. Выходное напряжение усилителя 1 с помощью широтно-импульсного модул тора 2 преобразуется в ШИМ-сигнал с относительной длительностью который через кбдо-управляемую схему 6 задержки поступает на управляющий вход ключа 14 линейной импульс но-управляемой проводимости второго плеча моста (резистор 13, ключ 14 обеспечивая автоматическое сведение его баланса, т.е. вы 5авнивание постоянных составляющих потенциалов на входах усилителя 1. Таким образом, в установившемся состоянии схемы уравновешивается баланс моста., т.е. средние значения про водимостей .с ответственно первого, вто рого , третье г6 и четверт го плеч моста. Очевидно, что проводи юсть четве того плеча моста запишется в виде лми где G. - проводимость соответствую щего резистора 17. Проводимости остальных плеч моста для постоянных составляющих токо имеют следующие выражения Gn 1 - г f;B,:lR,,,, 16 а 0a/Rifc R, - проводи V 6 iz -Na мости, и сопротивленсоответствующих реаисто-ров 12, 13 16. 1аким образом, значение выходной величины находится из уравнения (1) . 1-4 вь.х К , (2) К Gi Slu/ JnG-t . . С приходом -&, и &вь1к сумматор 10 rio модулю два вырабатывает реэностный интервал (Ci - Твьщ , за время которого аа счетчик 8 поступает импульсная последовательность fо с генератора 9 счетных импульсов через элемент И 5. RS-триггер 23 устанавливается к моменту окончания интервалов Т или Сзмх по большему из них: в О при t и в 1 при . В случае равенства 1: г TBWK состояние триггера 23, являясь неопределенным, не влияет на работу схемы, так как содержимое счетчика 8 оказывается равным нулю.При завершении действия t, иТрщСхема ЙЛИ-НЕ 3 вырабатывает разрешающий сигнал для осуществлв1 ия приема информациирегистром 7 и последующего (задержка по входу R) сброса в О счетчика 8. Перезапись кодового эквивалента (Cf ) счетчика в регистр производится со сдвигом на один разряд, благодаря чему регшизуется операция деления на два. В последний разряд регистра 7 записывается содержимое триггера 23. Кодо-управляемый блок 6 выполняет задержку одного из сигналов по входам. .«HA или «иВ при нгшичии единицы на управляющем входе V А или Y В соответственно. Таким образом, ШИМ-сигналы на выходах кодоуправляемого элемента задержки ©-и и ©наследуют со сдвигом фаз U, / -:РеыхГ. . 2. Работа цифровой ча1сти схемы пояс- няется временной диаграммой (см. фиг. 2а, б) для двух вариантов соответственно: в 7ввмхИ в,, ввьш В первом случае осуществляется сдвиг сигнала еых относительно 01 , а во втором - в относительно egyx. Введение определенного фазового сдвига (3) обеспечивает минимизацию погрешности функционирования двух последовательно включенных импульсно-управляемых проводимостей импульсно-управляемого делителя напряжения (элементы 11-14, 18). Учет этой дополнительной погрешности и позволяет повысить точность работы мостовой схемы в целом. . В основу построения умножения широтно-модулированных сигналов поЛджеи принцип введений управляемого фаэЪвого. сдвига ШИМ-сигналой, нап равленного на снижение методической . погрешности, обусловленной последо еа гельннм включением двух ймпульсно й с ЙЯяёмых проводимостей, которыепредставляют собой импульсно-управляемый делитель напряжения{ИУДН). Можно показать, что приведенная методическая погрешность работы ИУДН в статическом режиме бпрёЖё- ляется выражением ,, Ucp-dcp d- (1) где Оср - среднее значение напряжения на конденсаторе дл идеального режима функци онирования ИУДН. Учитывая прог1орци6нальн6сть проИУДН значенйям бтносй тельдых длительностей управляющих ШИМ-сигналов : для идеального режима функционирования, среднее значеййё йапрЯ){ения на конденсаторе ср- G i-QjQji . - IsrМожно показать, что погрешность, ; определяемая по формуле ()) при изменении &ц) от О до 1 и неизмененных © и ©2 меняет свой знак и может бытьсведена к нулю при некотором значении BtfЗначение относительного сдвига фаз , позволяю цее снизить погрешност более на порядок, определяется из выражения ,-&2-t/ - . %Mv,H 5;(6) Таким образом, из полученного вы ра5кения,(6) следует прйнятЬё для р ёалйМцйй в умножителе широтно Йддулированных сигналов выражение (3 в прёдЛа г аемом уйнЬжителе снйже на болёё чеМ на порядок методйчёс 1Ш1ггогрШ ю&ть ШйуЯ1 «5 -;--1 ег;цШ1й ёЛя ЙаПряжеЙйМ, т6 WiliiЙa ёт точность работы умножителя ши рбтно-мбдулированных сигналов по : :гр а йменшо с прототипом. Достоинствами умножителя являют ся акжё васокая надежность, обусловленная простотой схемы, помехоустойчивость, вытекающая из принципа усреднения ШИМ-сигналов, незави сймость выходной характеристики от изменений опорного напряжения, что является свойством мостовой схемы. Предлагаемый умножитель обладает К тому же высокой технологичностью что следует из/ возможности йсполь iBf iiiJr типовых интегральных микроЙхём, В том числе среднемасштабных и ймее:т по этой причине хорошие вес га аритные й :экъномйческйе показатели . Формула изобретения Умножитель широтно-модулированны сигналов, содерж ащий последовательHCi соединенные дифференциальйый уси литель и широтно-ймпульсный модулятор, элемент ИЛИ-НЕ, первый вход которого является первым входом умножителя , элемент И, первый, второй третий и четвертый масштабные резисторы, первый и второй сглаживающие конденсаторы, первый , второй и третий ключи, источник опооного напряжения, причем первый вход дифференциального усилителя подключен к первым выводам первого и второго масштабных реSWCTdpoB , вторые вцводы которых подключены через первый и второй ключи соответственно к источнику опорного напряжения и к шине нулевого потенциала, второй вход дифференциального усилителя подключен к первым выводам третьего и четвертого масштабных резисторов, вторые выводы которых подключены соответственно к источнику Опорного напряжения и через третий ключ к шине нулевого потенци- . ала, первый и второй входы дифференциального усилителя подключены через первый и второй конденсаторы соответственно к шине нулевого потенциала, отличающийся тем, что, с целью повышения точности, в него введены RS-триггер, кодоуправляемый блок задержки, параллельный регистр, суммирующий счетчик, генератор счетных импульсов, блок сложения по модулю два, первый вход которого, подключен к второму входу элемента ИЛИ-НЕ,к S-входу. КЗ-триггера , к первому информационному входу кодо-управляемого блока задержки и к выходу умножителя, второй вход блока сложения по модулю два подключен к первому входу устройства, R-нходу RS-трйггера и к второму информационйбйу входу кодо-управляемого блока задержки, выход блока сложения по модулю два подключен к первому входу элемента: И , к второму входу которого подключен выход генератора счетных импульсов, выход эле-. мента И Шдключен к суммирующему входу суммирующего счетчика, выход элемента ИЛИ-НЕ подключен к установочному входу суммирующего счетчика и к входу синхронизации параллельного регистра cooтвeтcтвeннo информационные входы параллельного.регистра подключены к информационным выхо; ам суммирующего счетчика и к выхоД-.м RS-трйггера-, информационные выходы параллельного регистра подключены .к управляющим входам кодоуправляемого блока задержки, выходы которого подключены к управляющим входам первого и второго ключей, упраЪляющий вход третьего ключа является вторым входом умножителя. Источники информации, принятые во внимание при экспертизе i 1.Авторское свидетельство СССР № 260290, кл. G Об G 7/16, 1970. 2.Авторское свидетельство СССР № 525114, кл. G Об G 7/161, 1976 (прототип) /

WT:

Si

SHX G нг

W

|l

Jll

11

11 H 111 И I I i H 111 n И 11 И

1

Htlllll

CT2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Множительно-делительное устройство | 1985 |

|

SU1305677A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2000 |

|

RU2171995C1 |

| Множительное устройство | 1977 |

|

SU693390A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2004 |

|

RU2255340C1 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| Акселерометр | 2017 |

|

RU2653140C1 |

| Функциональный широтно-импульсный преобразователь кода | 1987 |

|

SU1437882A1 |

V .rr - g Z -IIjего

Авторы

Даты

1980-11-15—Публикация

1978-12-28—Подача