{5) ПРЕОБРАЗОВАТЕЛЬ ЧИСЛО-ИМПУЛЬСНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь число-импульсного кода в параллельный двоичный код | 1984 |

|

SU1182685A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1990 |

|

SU1725399A1 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367035A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей в измерительных и вы-чи ели тел ьных у строй ст вах.

Известно устройство для счета количества единиц в последовательности двоичных символов, содержащее входной регистр, сумматоры и выходной регистр D.

Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь число-импульсного кода в последовательный двоичный код, содержащий входной регистр, счетчик, элементы И и элемент задержки 2.

Недостаток известных преобразователей - сложность.

Целью изобретения является упрощение преобразователя.

Поставленная цель достигается тем, что в преобразователе число-им- пульсного кода в параллельный двоичный код, содержащем входной регистр, счетчик, элементы И и элемент задержки, счетчик выполнен реверсивным, входной регистр выполнен в виДе регистра сдвига, информационный вход которого является информационным входом преобразователя и соединен с первым входом первого элемента И, тактовый вход регистра сдвига является тактовым входом преобразователя и

10 соединен с первым входом второго элемента И и через элемент задержки - с вторым входом первого элемента И, последовательный выход регистра сдвига соединен с вторым входом второго

15 элемента И, выходы первого и второго элементов И соединены соответственно с входом сложения и вычитания ревер-. сивного счетчика, выходы которого являются выходами преобразователя, а

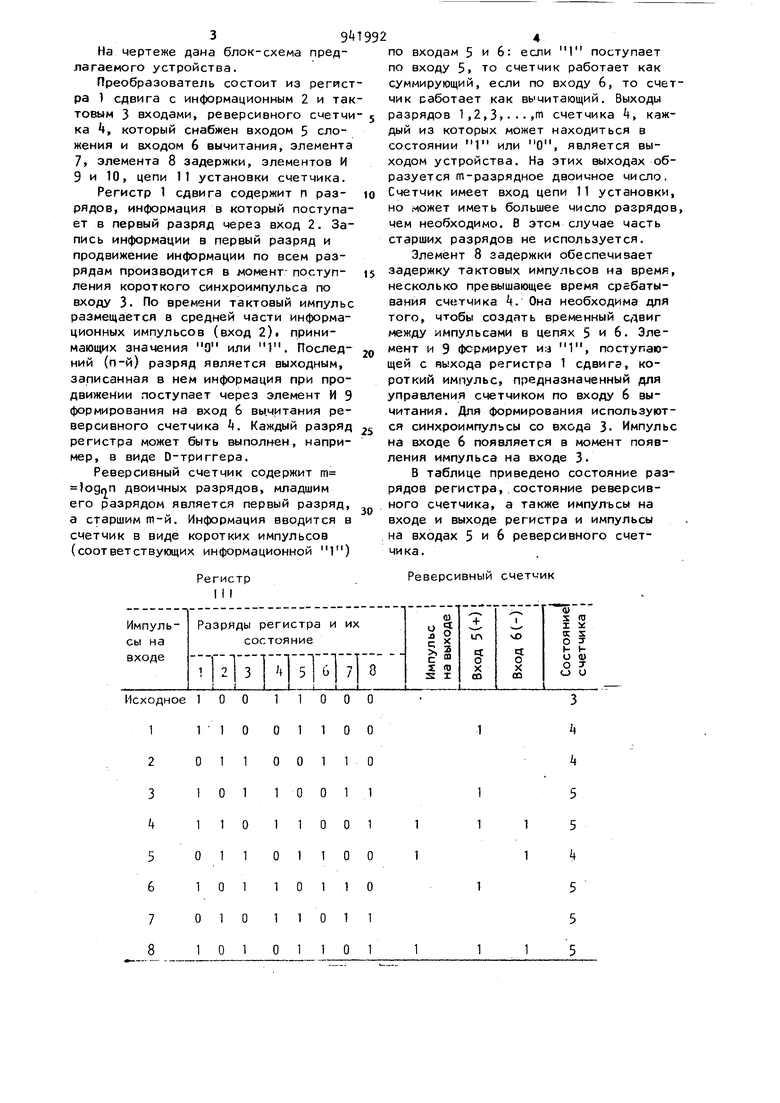

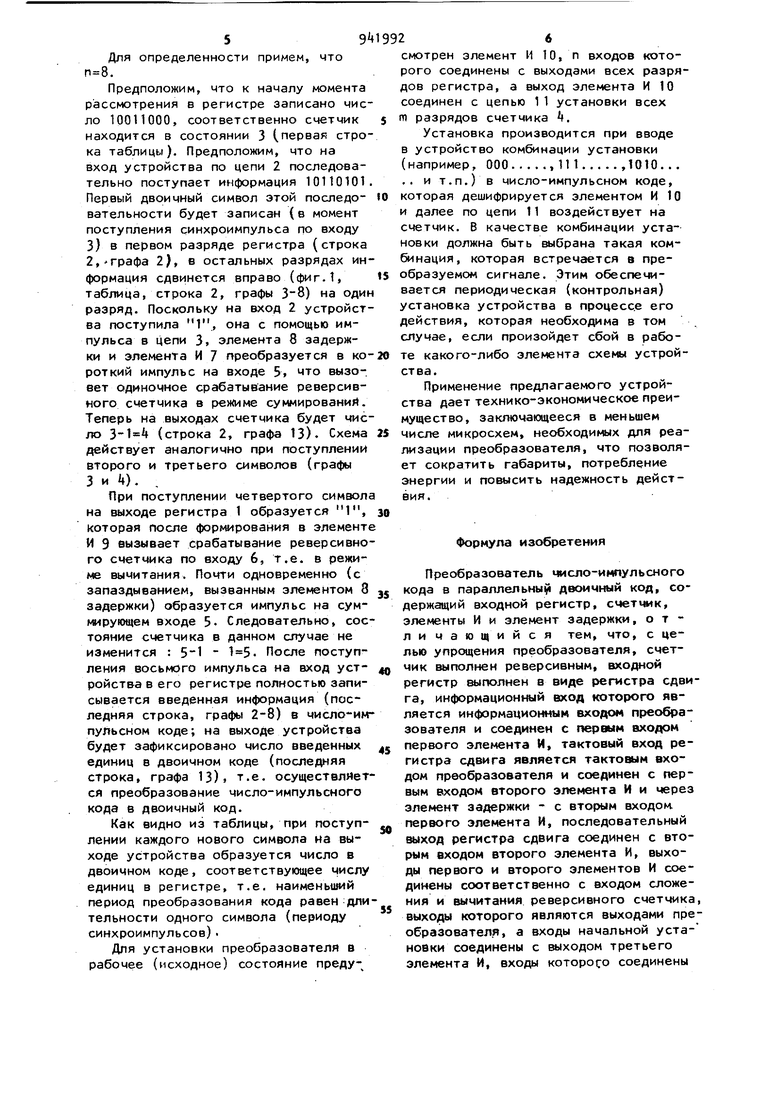

20 входа начальной установки соединены с обходом третьего элемента И, входы которого соединены с разрядными выхсгдами регистра сдвига. 39+ На чертеже дана блок-схема предлагаемого устройства. Преобразователь состоит из регист ра 1 сдвига с информационным 2 и так товым 3 входами, реверсивного сметчи ка k, который снабжен входом 5 сложения и входом 6 вычитания, элемента 7, элемента 8 задержки, элементов И 9 и 10, цепи 11 установки счетчика. Регистр 1 сдвига содержит п разрядов, информация в который поступает в первый разряд через вход 2. Запись информации в первый разряд и продвижение информации по всем разрядам производится & момент- поступления короткого синхроимпульса по входу 3. По времени тактовый импульс размещается в средней части информационных импульсов (вход 2). принимающих значения О или 1. ПоследНИИ (п-й) разряд является выходным, записанная в нем информация при продвижении поступает через элемент И 9 формирования на вход 6 вы.читания реверсивного счетчика Ц. Каждый разряд регистра может быть выполнен, например, в виде D-триггера. Реверсивный счетчик содержит т одлП двоичных разрядов, младшим его разрядом является первый разряд, а старшим ш-й. Информация вводится в счетчик в виде коротких импульсов (соответствующих информационной 1)

Регистр

Реверсивный счетчик

5 5 it 5 5 5 по входам 5 и 6: если 1 поступает по входу 5. то счетчик работает как суммирующий, если по входу 6, то счетчик работает как вычитающий. Выходы разрядов 1,2,3...,П1 счетчика 4, каждый из которых может находиться в состоянии 1 или О, является выходом устройства. На этих выходах образуется т-разрядное двоичное число. Счетчик имеет вход цепи 11 установки, но может иметь большее число разрядов, чем необходимо. В этом случае часть старших разрядов не используется. Элемент 8 задержки обеспечивает задержку тактовых импульсов на время, несколько превышающее время срабатывания счетчика k. Она необходима для того, чтобы создать временный сдвиг между импульсами в цепях 5 и 6. Элемент и 9 формирует из 1, поступающей с выхода регистра 1 сдвиге, короткий импульс, предназначенный для управления счетчиком по входу 6 вычитания. Для формирования используются синхроимпульсы со входа 3- Импульс на входе 6 появляется в момент появления импульса на входе 3. В таблице приведено состояние разрядов регистра, состояние реверсивного счетчика, а также импулъсы на входе и выходе регистра и импульсы на входах 5 и 6 реверсивного счетчика. Для определенности примем, что . Предположим, что к началу момента рассмотрения в регистре записано число 10011000, соответственно счетчик находится в состоянии 3 (первая строка таблицы). Предположим, что на вход устройства по цепи 2 последовательно поступает информация 10110101. Первый двоичный символ этой последовательности будет записан (в момент поступления синхроимпульса по входу 3) в первом разряде регистра (строка 2,Графа 2), в остальных разрядах информация сдвинется вправо (фиг.t, таблица, строка 2, графы 3-8) на один разряд. Поскольку на вход 2 устройства поступила 1, она с помощью импульса в цепи 3, элемента 8 задержки и элемента И 7 преобразуется в короткий импульс на входе 5, что вызовет одиночное срабатывание реверсивного счетчика в режиме суммирований. Теперь на выходах счетчика будет число 3-1 (строка 2, графа 13). Схема действует аналогично при поступлений второго и третьего символов (графы 3 и 1). , При поступлении четвертого символа на выходе регистра 1 образуется 1, которая после формирования в элементе И 9 вызывает срабатывание реверсивного счетчика по входу 6, т.е. в режиме вычитания. Почти одновременно (с запаздыванием, вызванным элементом 8 задержки) образуется импульс на суммирую1цем входе 5. Следовательно, состояние счетчика в данном случае не изменится : 5- После поступления восьмого импульса на вход устройства в его регистре полностью записывается введенная информация (последняя строка, графы 2-8) в число-импульсном коде; на выходе устройства будет зафиксировано число введенных единиц в двоичном коде (последняя строка, графа 13). т.е. осуществляется преобразование число-импульсного кода в двоичный код. Как видно из таблицы, при поступлении каждого нового символа на выходе устройства образуется число в двоичном коде, соответствующее числу единиц в регистре, т.е. наименьший период преобразования кода равен длительности одного символа (периоду синхроимпульсов). Для установки преобразователя в рабочее (исходное) состояние преду926 смотрен элемент И 10, п входов которого соединены с выходами всех разрядов регистра, а выход элемента И 10 соединен с цепью 1 1 установки всех т разрядов счетчика . Установка производится при вводе в устройство комбинации установки (например, 000,111,1010. ., ,. и т.п.) в число-импульсном коде, которая дешифрируется элементом И 10 и далее по цепи 11 воздействует на счетчик. В качестве комбинации установки должна быть выбрана такая комбинация, которая встречается в преобразуемом сигнале. Этим обеспечивается периодическая (контрольная) установка устройства в процессе его действия, которая необходима в том случае, если произойдет сбой в работе какого-либо элемента схемы устройства. Применение предлагаемого устройства дает технико-экономическое преимущество, заключающееся в меньшей числе микросхем, необходимых для реализации преобразователя, что позволяет сократить габариты, потребление энергии и повысить надежность действия. Формула изобретения Преобразователь число-импульсного кода в параллельны двоичный код, содержащий входной регистр, счетшлк, элементы И и элемент задержки, о т ли чающийся тем, что, с целью упрощения преобразователя, счетчик выполнен реверсивным, входной регистр выполнен в виде регистра сдвига, информационьый вход которого является информационным входом преобразователя и соединен с первым входом первого элемента И, тактовый вход регистра сдвига является тактовым входом преобразователя и соединен с первым входом второго элемента И и через элемент задержки - с вторым входом, первого элемента И, последовательный выход регистра сдвига соединен с вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с входом сложения и вычитания реверсивного счетчика, выходы которого являются выходами преобразователя, а входы начальной установки соединены с выходом третьего элемента И, входы KOTopoi o соединены с разрядными выходами регистра сдвига. Источники информации, принятые во внимание при экспертизе s

Bf. аяф

m

вл си

.

Buxet

т

-f

f 1 . Авторскоесвидетельство СССР № 450160, кл. GОб F 5/02, 197. 2. Авторскоесвидетельство СССР № i 47711, кл. GОб F , 1973 (прототип)i

Авторы

Даты

1982-07-07—Публикация

1980-11-28—Подача