(54) УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО СЧЕТА КОЛИЧЕСТВА . ЕДИНИЦ (НУЛЕЙ) в двоичном ЧИСЛЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного счета количества единиц (нулей) в двоичном числе | 1979 |

|

SU781811A2 |

| Устройство для контроля двоичной информации в кодах Бергера | 1982 |

|

SU1068942A1 |

| Устройство для кодирования линейных полиномиальных кодов | 1989 |

|

SU1711338A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Кодер | 1990 |

|

SU1783623A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Система сжатия и восстановления информации | 1971 |

|

SU437070A1 |

Изобретение относится к вычислительной технике и может быть применено в системе защиты от ошибок двоичной ин.фориации, передаваемой между отдельными дискретными блоками вычислительных машин.

По основному авт.св. 450160 известно устройство для параллельного счета количества единиц (нулей) в двоичном числе, содержащий п-разрядный входной регистр, входной регистр, rpyrfn сумматоров, по n/2k сумматоров в каждой.группе (1 к logjn) , причем выхог суммы последнего сумматора каждой группы и выход переноса сумматора последней К-ой группы соединены с вхо-. дами соответствующих разрядов каждого регистра, входы каждого i-ro сумматора К-ой группы соединены с выходами переноса 2 i-ro и (2 1-1)-го сумматоров (К-1)-ой группы и .с выходом суммы (1-1)-го сумматора. К-ой группы, выходы 2 1-го и (2 i-l)-ro разрядов входного регистра соединены с входами 1-го сумматора первой группы 1.

,Недостаток известного устройства состоит в его ограниченных функциональных возможностях. Этот недоста-ток обусловлен тем, что устройство выполняет только функции параллельного двоичного счетчика.

Целью изобретения является расширение функциональных возможностей устройства за счет преобразования исходного кода в помехозащищенный эквивалентный код Бергера . Кодовое слово эквивалентного кода

10 Бергера включает в себя информационную часть и проверочную. Информационная часть представляет собой исходное п-разрядное двоичное слово, а проверочная - двоичное число К ,

15 равное.числу нулей в исходном двоичном слове, если старший разряд в нём имеет единичное значение, или двоичное число суммы двух чисел К и если старший разряд в исходном двоич20ном слове имеет нулевое значений. K-j в этом случае - также число нулей в исходном двоичном слове, а Kj ( - 1)-п,где имеет целое значение такое, что выполняется условие:

25

( п

min

Указанная цель достигается тем, что устройство для параллельного счета количества единиц (нулей) в 0 двoич oм числе дополнительно сойержит элемент И, входы которого соединены с выходом старшего разряда входного регистра и управляющей шиной устройства, а выход подключен к третьим входам первых сумматоров тех групп, номера которых соответствуют номерам единичных разрядов двоичного представления числа К 2 (К (2 - l)-nj q - целоечисло; min (2 - 1) n; (n - разрядность исходного числа),

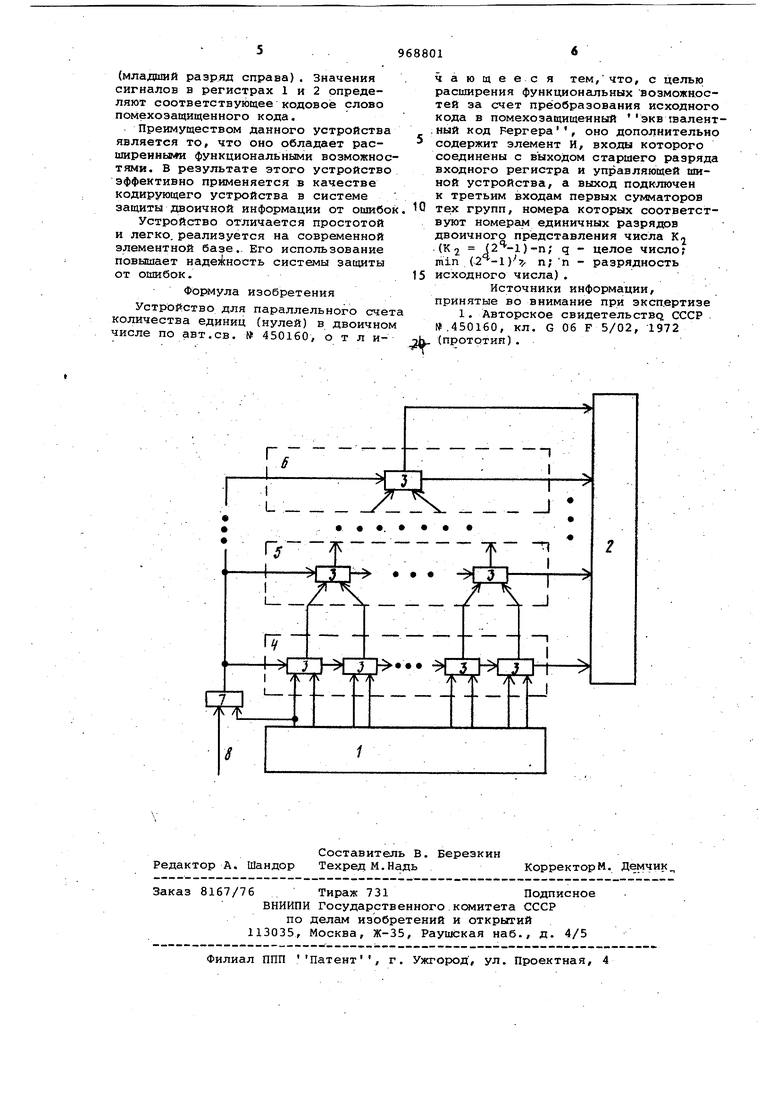

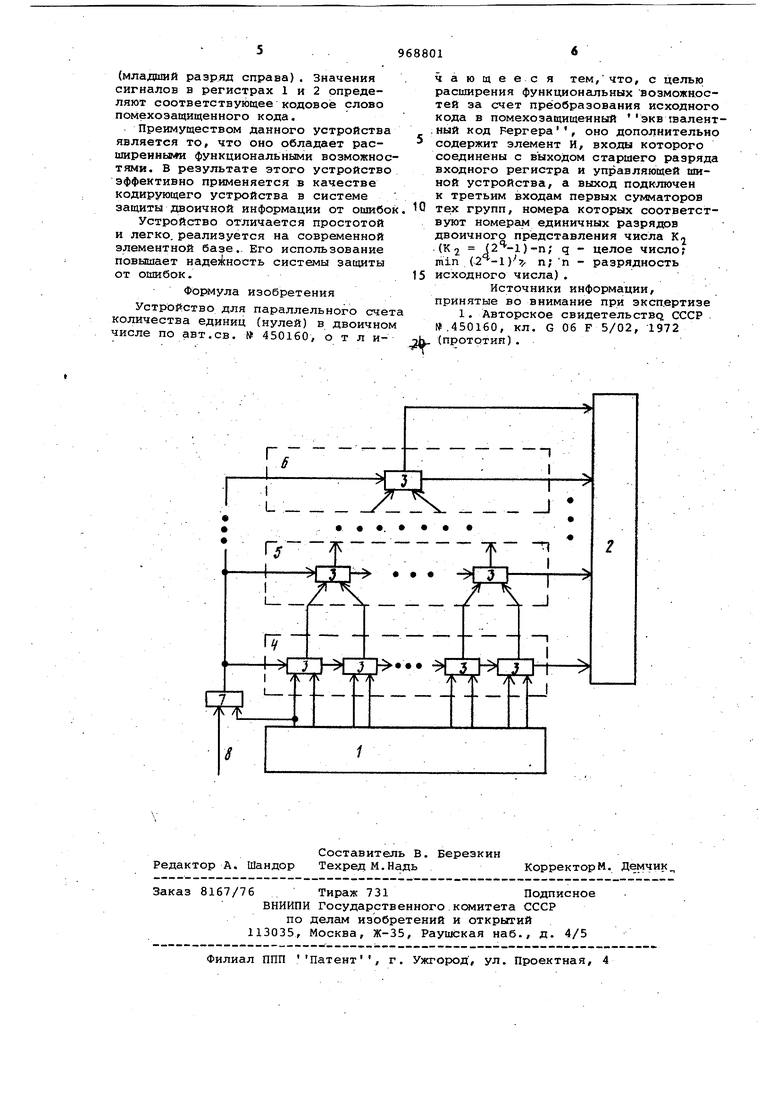

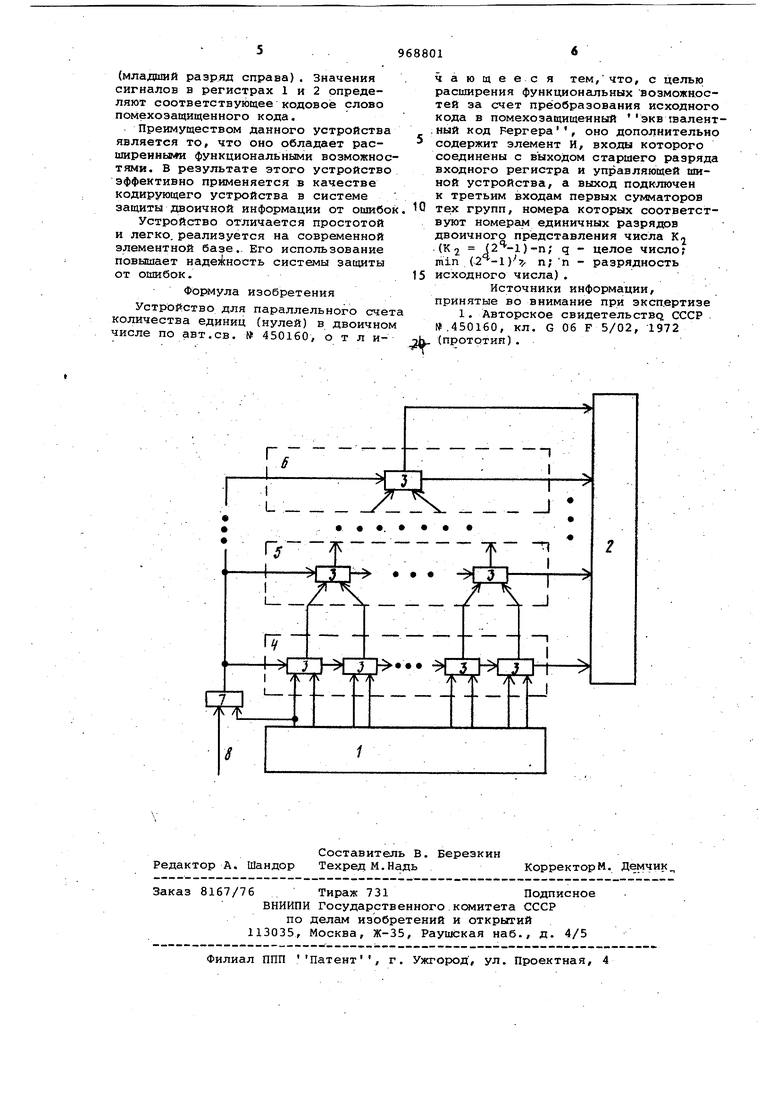

На. чертеже представлена функциональная схема устройства.

Устройство содержит п-разрядный входной регистр 1, выходной регистр 2, сумматоры 3, соединенные в группы 4, 5, б, элемент И 7,. управляющую шину 8.

Устройство имеет следующую- структуру связей: инверсные выходы 2 i-ro и (2 i-l)-ro разрядов входного регистра 1 соединены с входами 1-го сумматора 3 первой группы 4 (i 1, ...,п/2). В последующих группах. 5, 6, 7 входы каждого j-ro сумматора 3 К-ой группы (К -1,2,...,1од2п) соединены, с выходами переноса 2 j-ro и (2 j-l)-ro сумматоров 3 (К-1)-ой группы и с выходом суммы (j-l)-ro сумматора 3 К-ой группы ( j 1, .. . , Iog.n-K) , Выход суммы пос.педнего сумматора 3 каждой группы (нумераци слева направо) и выход переноса сумматора 3 последней группы 6 соеди нены со входами соответствующих разрядов выходного регистра 2. Первый вход элемента И 7 соединен с выходом старшего разряда входного регистра 1 (старший разряд регистра 1 находится слева), второй - с управляющей шиной 8, а выход соединен с третьим входом первого сумматора 3 соответствуюидах групп 4,5,6 сумматоров 3.

Подключение третьего входа первого сумматора 3 К-ой группы; к выходу элемента И 7 осу1цествляется в том случае, если сопоставленный этой группе i-ый двоичного числа К имеет значение ,.Младший разряд двоичного числа К сопоставляется первой группе 4 сумматоров 3, остальные разряды сопос.тавляются другим группам сумматоров 3 в соответствии с естественным возрастанием порядкового номера.

входной регистр 1 предназначен для приема и хранения исходного двоичного слова.

Выходной регистр 2 предназначен для хранения результата преобразования в двоичном коде.

Группы 4, 5, 6 сумматоров 3 представляют собой параллельный двоичный счетчик, который также осуществляет формирование проверочных разрядов кодового слова помехозащищенног кода.

Элемент И и шина 8 предназначены для задания режима работы устройства.

Устройство работает в двух режимах.

В первом 3том режиме устройство 5 осуществляет подсчет числа нулей в исходном двоичном слове,, записанном во входной регистр 1. Для задания этого, режима работы устройства на второй вход элемента И 7 подается 0 по шине 8 потенциальный сигнал с значением О. В этом случае на третьем входе первого сумматора 3 каждой группы 4, 5, 6 присутствует сигнал с значением О. Такое исходное состояние вьциеописанных

элементов обеспечивает первый режим работы устройства.

Второй режим работы устройства позволяет осуществлять преобразование исходного двоичного слова в ко.довое слово помехозащищенного кода.. . В эгом режиме устройство осуществляется формирование сигна лов проверочных, разрядов соответствующего 5 кодового слова, которые записываются в выходной регистр 2. .

Для задания второго режима работы устройства на второй вход элемента И 7 подается по шине 8 потенциальный Q сигнал с значением Ч . В этом режиме работы устройства значение сигнала на выходе элемента И 7 определяется значением сигнала старшего разряда входного регистра 1.

. Работу устройства во втором режиме функционирования рассмотрим на конкретном призере при преобразовании восьмиразрядных (п 8) двоичных слов в кодовые слова помехозащищенного кода. 0

Конструкция устройства в этом случае соответствует .структуре,изображенной на чертеже без учета разрывов в связях.. 5 Для рассматриваемого варианта

третий вход первого сумматора 3 каждой группы 4,5, 6 подключен к выходу элемента И 7, так как число в двоичном коде имеет вид 111.

Значение определено по формуле

К (2 - 1)-8, где q „4, что следует из .условия: min () 7/8.

Пусть в регистре 1 записано слово 00111111 (старший разряд находится слева). На третий вход первого сумматора 3 каждой из групп 4, 5, 6 поступает сигнал с значением . На первый и второй входы первого сумматора 3 первой группы 4 посту. На

пают сигналы с значением

первый и второй входы остальных

сумг аторов 3 первой группы 4 поступают сигналы О .. В результате преобразования в регистр 2 записываются сигналы проверочных разрядов,

определяемые двоичным словом 1001

(младший разряд справа). Значения сигналов в регистрах 1 и 2 определяют соответствуйщее кодовое слово помехоэащищенного кода.

Преимуществом данного устройства является то, что оно обладает расширеиньми функциональными возможностями. В результате этого устройство эффективно применяется в качестве кодирующего устройства в системе защиты двоичной информации от ошибок

Устройство отличается простотой и легко, реализуется на современной элементной базе.. Его использование повышает надежность системы защиты от ошибок.

Формула изобретения

Устройство для параллельного счет количества единиц (нулей) в двоичном числе по авт.св. № 450160, о т л иг

чающееся тем,что, с целью расширения функционгшьных возможностей за счет преобразования исходного кода в помехозащищенный эквивалентный код Feprepa, оно дополнительно содержит элемент И, входы которого соединены с выходом старшего разряда входного регистра и управляющей шиной устройства, а выход подключен к третьим входам первых сумматоров

0 тех групп, номера которых соответствуют номерам единичных разрядов двоичного представления числа К . (К 2 ()-п; q - целое число; min ()-7 п;п - разрядность 5 исходного числа)..

Источники информации, принятые во внимание при экспертизе

(прототип).

Авторы

Даты

1982-10-23—Публикация

1981-05-19—Подача