(54) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ПРОГРАММИРОВАНИЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1983 |

|

SU1273974A1 |

| Устройство для обучения программированию | 1989 |

|

SU1679525A1 |

| Устройство для обучения операторов | 1987 |

|

SU1492368A1 |

| Устройство для обучения операторов | 1988 |

|

SU1554001A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Обучающее устройство | 1977 |

|

SU822230A2 |

| Устройство для обучения операторов | 1988 |

|

SU1594582A1 |

| Устройство для обучения и контроля знаний обучаемых | 1982 |

|

SU1065869A1 |

| Устройство для формирования учебной информации | 1988 |

|

SU1562951A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

1

Изобретение относится к вычислительной технике, может найти применение в системе образования для обучения программированию, как тренажер и учебно-демонстрационное устройство. 5

Известно устройство, в котором микрокоманды находятся в запоминающем блоке, откуда производятся их последовательное считывание. .Устройство содержит схему, хранящую заранее уста- 10 новленные адреса, схему, осуществляющую сравнение; схему контролирУйедую повторное прохождение команд; схему контролирующую повторную обработку данных 1 .15

Недостаток устройства - отсутствие демонстрационных средств и наличие одного автоматического режима обработки информации, что снижает его педагогическую ценность.20

Известно также устройство которое содержит центральный блок обработки . данных и периферийный блок, осуществляющий функцию вспомогательной пг1мяти.В периферийном блоке двоичные эле-2$ менты информации записываются в по следовательных разделах памяти. Расположение разделов памяти - фиксированное и адресация осуществляется с помощью групп адресных элементов, KO-JQ

торые обеспечивают последовательный доступ к позициям памяти. Устройство содержит также блок управления, вырабатывающий универсальные логические адресные сигналы, предназначенные для блока памяти, вырабатывакяциёся путем воздействия базированных сигналов на адресные сигналы пользователей, получаемые центральным блоком обработки. Из этого следует, что при необходимости заменить блок памяти в блоке перестановки достаточно использовать количественные параметры (2 .

Недостаток устройства - невозможность демонстрации деталей выполнения отдельных команд, наблюдения за всеми промежуточными результатами и сложно организованный рабочий цикл.

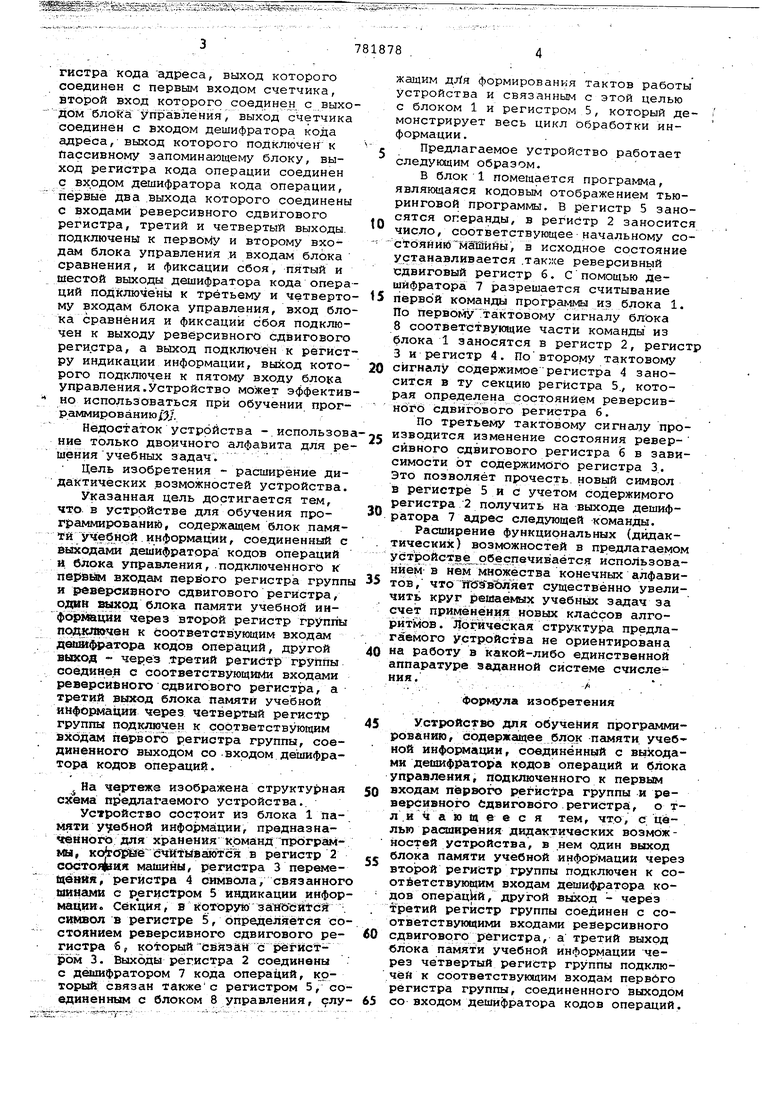

Наиболее близким к предлагаемому является устройство, содержащее пассивный запоминаюспий блок, выход которого подключен ко входу регистра кода операций, блок управления которого подключен к регистру кода адреса, блок сравнения и фиксации сбоя, дешифратор кода операций, данифратор кода адреса, счетчик, реверсивный сдвиговый регистр, регистр индикации, ричем второй выход пассивного запоминающего блока соединен с входом регистра кода адреса, выход которого соединен с первым входом счетчика, второй вход которого соединен с выхо дом блока уп1равлёния, выход счетчика соединён с входом дешифратора кода адреса, выход которого подключенк Пассивному запоминающему блоку, выход регистра кода операции соединен с входом дешифратора кода операции, первые два выхода которого соединены с входами реверсивного сдвигового регистра, третий и четвертый выходы, подключены к первому и второму входам блока управления .и входам блока сравнения, и фиксации сбоя, пятый и шестой выходы дешифратора кода опера ций подключены к третьему и четверто му входам блока управления, вход бло ка сравнения и фиксации сбоя подключен к выходу реверсивного сдвигового реги.стра, а выход подключен к регист ру индикации информации, выход которого подключен к пятому входу блока управления.Устройство может эффектив но использоваться при обучении программированию 0/ Недостаток устройства -.использов ние только двоичного алфавита для ре шения учебных задач. Цель изобретения - расширение дидактических возможностей устройства. Указанная цель достигается тем, что в устройстве для обучения программировании, содержащем блок памяти учебной . информации , соединенный с выходами дешифратора кодов операций и блока управления, подключенного к nepBtSM входам первого регистра групп и реверсивного сдвигового регистра, сдан щахоя блока памяти учебной инф6 р ции через второй регистр группы подключен к соответствующим входам дешй атора кодов операций, другой выход через .третий регистр группы соедияей с соответствующийи входами реверсиемого сэдвигового регистра, а третий выход блока памяти информации через четвертый регистр группы подключен к соответствующим входам первого регистра группы, соединенного выходом со входом дешифратора кодов операций. На чертеже изображена структурная схема предлагаемого устройства.. Устройство состоит из блока 1 памяти учебной информации, предназначенного для хранения команд прогрйммы, кЫгбЙЙё счйтйвайбтся в регистр 2 состояния машины, регистра 3 перемемевня, регистра 4 символа, связанног шинами с регистром 5 индикации инфор мации, секция, в которую зайЬсйтсй символ в регистре 5, определяется со стоянием реверсивного сдвигового регистра б, который Сйязай с |)егйстром 3. Выходы регистра 2 соединены с дешифратором 7 кода операций, который связан такжес регистром 5, с единенным с блоком 8 управления, слу

781878 жащим дЛя формирования тактов работы Устройства и связанным с этой целью с блоком 1 и регистром 5, который демонстрирует весь цикл обработки информации . Предлагаемое устройство работает следующим образом. В блок 1 помешается программа, являющаяся кодовым отображением тьюринговой программы. В регистр 5 заносятся операнды, в регистр 2 заносится число, соответствующее начальному состояний маТЙййы, в исходное состояние устанавливается ,так;;се реверсивнь1й сдвиговый регистр б. С помощью дешифратора 7 разрешается считывание первой команды програм мы из блока 1. По первому актов ому сигналу блока 8 соответствующие части команды из блока 1 заносятся в регистр 2, регистр 3 и регистр 4. Повторому тактовому сигналу содержимоерегистра 4 заносится в ту секцию регистра 5., которая определенасостоянием реверсивного сдвигового регистра 6. По третьему тактовому сигналу производится изменение состояния реверсйвного сдвигового регистра б в зависимости от содержимого регистра 3. Это позволяет прочесть, новьлй символ в регистре 5 и с учетом содержимого регистра 2 получить на выходе дешифратора 7 адрес следующей команды. Расширение функциональных (дидактических) возможностей в предлагаемом Устройстве обеспечивается использованием в нем множества конечных алфавитов, что существенно увеличить круг решаемых учебных задач за счет применения новых классов алгоритмов. Логическая структура предлагаемого Устройства не ориентирована на работу в какой-либо единственной аппаратуре заданной системе счисления. . Формула изобретения Устройство для обучения программированию, содержащее блок памяти учебиой информации, соединённый с выходами дешиф1 атора кодов операций и блока управления, подключенного к первым входам первого регистра группы и реверсивного Сдвигового регистра, о тл .и ч а ю ад е е с я тем, что, с целью расширения дидактических возможностей устройства, в нем один выход блока памяти учебной информации через второй регистр группы подключен к соотйетствующим входам дешифратора кодов операц 1й, другой вьюсод - через третий регистр группы соединен с соответствующими входами реверсивного сдвигового регистра, а третий выход блока памяти учебной информации через четвертый регистр группы подключен к соответствующим входам первбго регистра группы, соединенного выходом со входом дешифратора кодов операций.

Источники информации, принятые во внимание при экспертйзё

781878

2; Патент Франции № 2295480. . кл. G Об F 15/00, .

Авторы

Даты

1980-11-23—Публикация

1979-04-18—Подача